标签:style blog http color os strong sp 数据 div

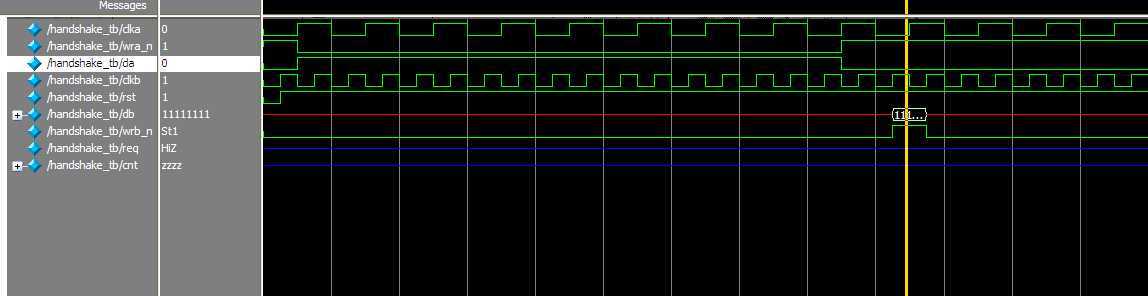

1 module handshake( 2 input clka,wra_n,da,clkb,rst, 3 output reg [7:0] db, 4 output reg wrb_n 5 ); 6 7 reg ack,temp,req1; 8 reg [7:0] data; 9 always@(posedge clka or negedge rst) 10 if(!rst) 11 data<=8‘d0; 12 else if(!wra_n) 13 data<={data[6:0],da};//data<={da,data[7:1]}; 14 always@(posedge clkb or negedge rst) 15 if(!rst) 16 begin 17 req1<=1‘b1; 18 temp<=1‘b1; 19 end 20 else 21 begin 22 temp<=wra_n; 23 req1<=temp; 24 end 25 assign wra_n_rising=temp&&(~req1);//捕获wra_n的上升沿,使能wrb_n一个时钟周期 26 always@(posedge clkb or negedge rst) 27 if(wra_n_rising) 28 begin 29 wrb_n<=1‘b1; 30 db<=data; 31 end 32 else 33 begin 34 wrb_n<=1‘b0; 35 db<=8‘hxx; 36 end 37 endmodule

题目要求:完成两个时域的接口转换电路。

解释:串转并:data<={data[6:0],da};(从D7开始输入,不断左移)data<={da,data[7:1]}(从D0开始输入,不断右移)

捕获写信号的上升沿,转化为与数据同时输出的b时域的使能信号。

标签:style blog http color os strong sp 数据 div

原文地址:http://www.cnblogs.com/fkl523/p/4045683.html