标签:输出 失败 如何使用 r++ 打开 ash lock div2 stm32f0

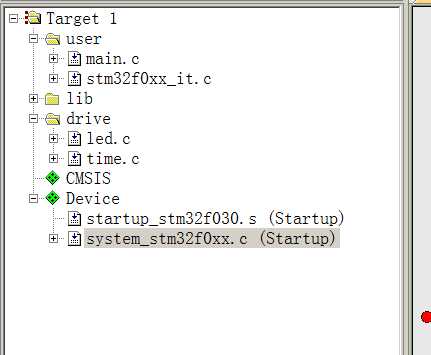

以STM32F030,uVision开发环境为例。

1、打开项目,找到system_stm32f0xx.c并打开

2、找到static void SetSysClock(void)函数,用以下代码替换:

static void SetSysClock(void)

{

__IO uint32_t StartUpCounter = 0, HSIStatus = 0; //

RCC->CR |= ((uint32_t)RCC_CR_HSION); //使能内部时钟 HSI

do //等待内部时钟起振

{

HSIStatus = RCC->CR & RCC_CR_HSIRDY; // 设置RCC

StartUpCounter++; //启动计数器

}

while((HSIStatus== 0) && (StartUpCounter != HSI_STARTUP_TIMEOUT)); // 等待 HSE 启动稳定

if ((RCC->CR & RCC_CR_HSIRDY) != RESET) //判断启动状态

{

HSIStatus = (uint32_t)0x01;

}

else

{

HSIStatus = (uint32_t)0x00; //启动不成功

}

if (HSIStatus == (uint32_t)0x01) //启动成功

{

/* Enable Prefetch Buffer and set Flash Latency */

FLASH->ACR = FLASH_ACR_PRFTBE | FLASH_ACR_LATENCY; //flash总线时钟使能

/* HCLK = SYSCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1; //外设高速AHB2总线时钟等于系统时钟/1

/* PCLK = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE_DIV1; //外设低速APB1总线时钟等于系统时钟/1

/* PLL configuration = HSI/2 * 12= 48 MHz */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLSRC | RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSI_Div2 | RCC_CFGR_PLLMULL12);

//RC时钟2分频后 进行12倍频

//=8M/2*12=48M

RCC->CR |= RCC_CR_PLLON; //使能锁相环倍频开关 /* Enable PLL */

while((RCC->CR & RCC_CR_PLLRDY) == 0) //等待锁相环就绪

{ }

/* Select PLL as system clock source * //选择锁相环输出时钟作为系统时钟

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)RCC_CFGR_SWS_PLL)

{ } //等待锁相环输出时钟已经成为系统时钟

}

else

{ } //启动失败,在此写代码

}

标签:输出 失败 如何使用 r++ 打开 ash lock div2 stm32f0

原文地址:https://www.cnblogs.com/beiyhs/p/11211691.html