标签:版本 sys 下载 str risc 高电平 内存映射 中断处理程序 适配器

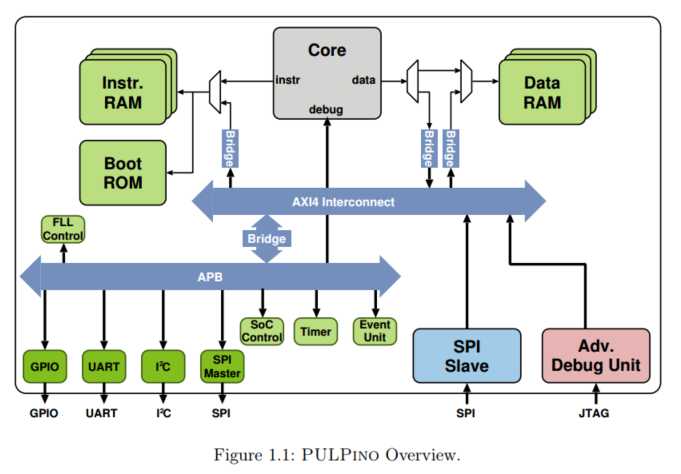

一、概述 PULPino是一个以RISCV架构RI5CY/ZERO-RISCY为内核的单核SoC,复用了PULP的多个组件。PULP使用相互独立的单端口data RAM与instruction RAM。它还包括一个boot ROM,内有boot loader,可以通过SPI从外设flash加载程序,

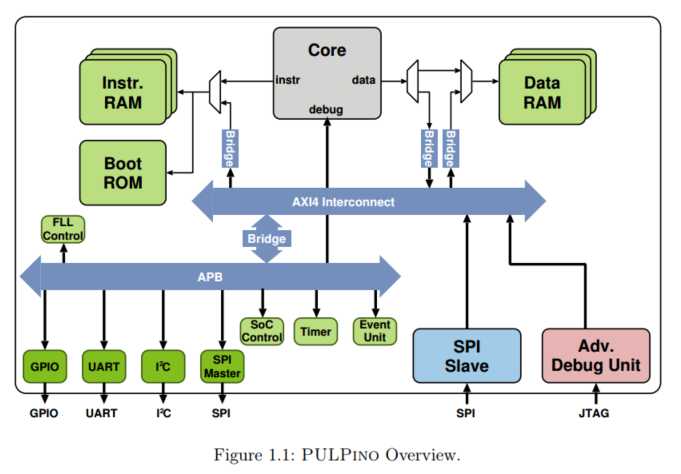

图1.1展示了SoC的模块框图。PULPino使用AXI作为主要的互连,具有到APB的桥接器,用于连接简单的外设。AXI与APB都具有32位的数据通道。处于debug的需求,SoC包括一个advanced debug unit可以同JTAG直接访问内核寄存器、两个RAM与内存映射IO。两个RAM经由总线适配器与AXI相连。

虽然PULPino有FPGA版本,但其主要针对RTL仿真与ASIC。FPGA版本在性能方面并不是特别优化,因为我们主要将其用作仿真平台而不是独立平台。

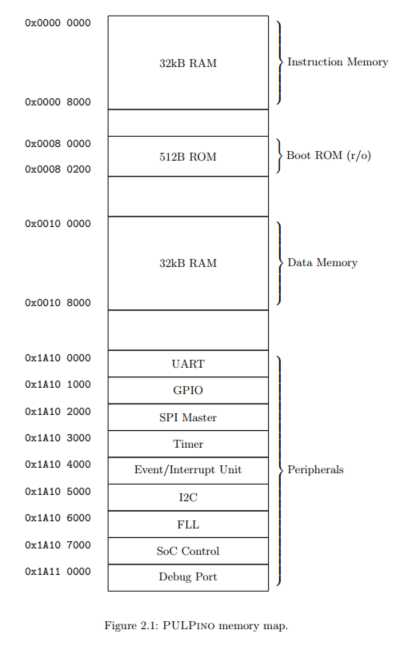

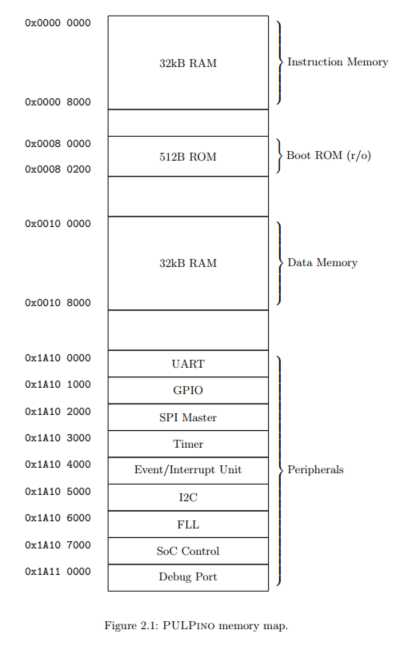

二、内存映射 图2.1展示了假设数据和指令RAM均为32kB情况下的PULPino的默认内存映射。这可以在PULPino顶级SystemVerilog文件中更改。

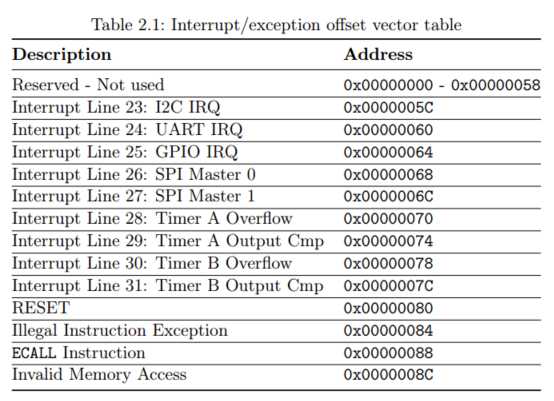

2.1 中断向量表

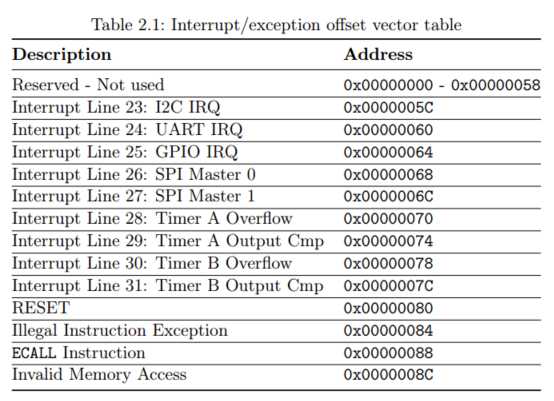

PULPino的中断向量表遵循RI5CY核心的定义。

中断像量表中的条目必须是一个32位,或者一个或两个16位指令,告诉核心如何处理中断。在大多数情况下,这意味着核心将执行跳转到实际的中断处理程序。

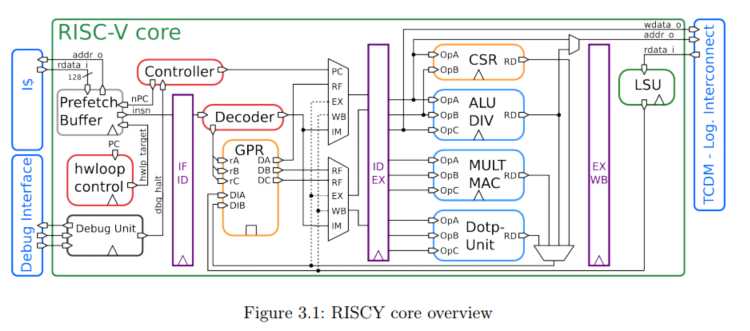

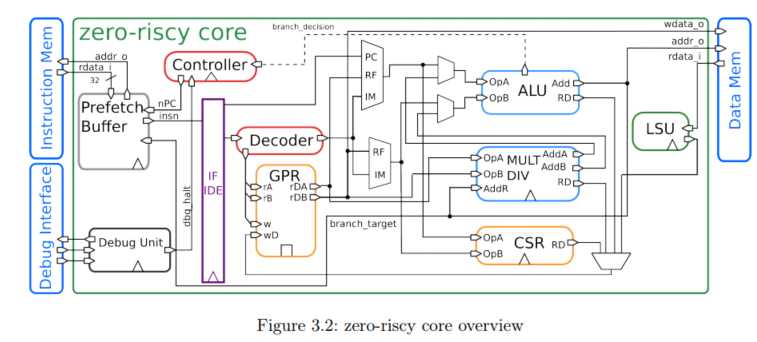

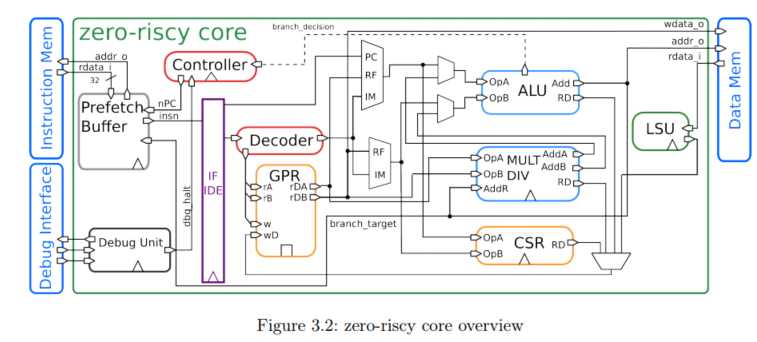

三、CPU内核 PULPino支持RISCV RI5CY与RISCV ZERO-RISCY两种内核。两个内核具有相同的外部接口,因此可以做到拔插兼容。图3.1 3.2展示了两个内核的架构。

内核使用十分简单的数据和指令接口与数据指令存储器进行通信。为了与AXI通信,在PULPino中实例化了core2axi协议转换器。

处于调试的目的,所有的内核寄存器都已经进行了内存以你干涉,允许通过AXI访问。内核中的调试单元通过总线、读取/设置内核寄存器、halts内核来处理请求。内核支持性能计数器。性能计数器主要用于计算内核内部事件,如停顿,也可以计算内核外部事件。因此,在ext_perf_counters_i端口可以附加任意事件。每次端口有高电平到来时,内核都会增加此事件类型对应的内部性能计数器。

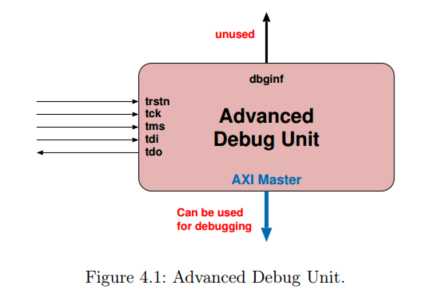

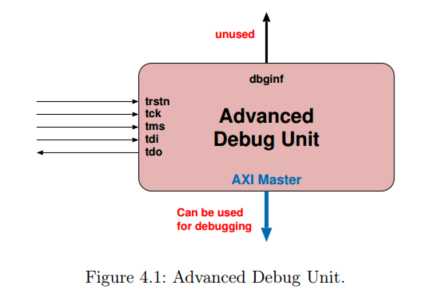

四、advanced debug unit

advanced debug unit包含一个AXI主机接口用于访问外设和存储器。PULPinoV1的advanced debug unit不具有专门的用于读取内核寄存器的接口

所有的内核寄存器都进行了内存映射,这意味着他们都可以通过AXI总线被读取。因此进行可以通过JTAG进行调试,还可以通过SPI或者任何其他接口进行调试。

JTAG信号被连接到SoC的引脚上。

有关调试的相关细节,请查看advanced debug unit的文档

五、外设PULPino中的所有外设都连接到APB总线,但SPI从设备除外,它是一个十分特殊的设备。有关SPI从设备的相关信息,参考第六节

原文下载:https://github.com/pulp-platform/pulpino/blob/master/doc/datasheet/datasheet.pdf

【翻译|PULPino|RISCV】PULPino数据手册

标签:版本 sys 下载 str risc 高电平 内存映射 中断处理程序 适配器

原文地址:https://www.cnblogs.com/picky-eater/p/11242718.html