标签:bcd 规则 应用 之间 info 避免 关于 蓝色 bit

(1)

Grey码在FPGA实际应用中是实用的码,在8421BCD码累加计数器中,如果寄存器需要发生多位(两位或者以上)的跳变,会出现中间态,这样作为组合逻辑的输入是不稳妥的。

下面看两个中间态的例子:

这是累加器的状态转换时序观察,存在中间不希望的状态。如果作为组合逻辑的输入,状态有可能跑飞。

左边0111 -> 0101 -> 1000,右边0101 -> 0111 -> 0110

(2)

采用格雷码可以避免中间态的出现,因为相邻两个状态之间只有1 bit差异。

下面是8421BCD码(自然计数码)和格雷码的对应关系,以3bit为例:

自然码 0 1 2 3 4 5 6 7

自然码二进制 000 001 010 011 100 100 101 111

格雷码对应的十进制 0 1 3 2 6 7 5 4

格雷码 000 001 011 010 110 111 101 100

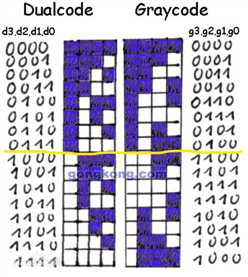

在百度百科上面看到了这个图片,发现了规律:

对于这个4 bit格雷码,我们发现最高位(g3)在组群前一半是0,后一半是1,非常整齐。而且非最高位(g2,g1,g0)组成的状态关于黄线对称,比如离黄线最近的g2g1g0都是100,再远一位是101,。。。最远一位是000。

按照这个规则,我们可以由n长度的格雷码生成n+1长度的格雷码。

- - 附录 - -

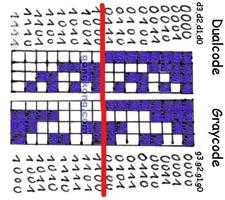

把这个图倒过来,看到白色蓝色的方块图案:

我们发现格雷码的方块图案关于红线是轴对称的(除了最高位g3),

8421BCD码的方块图案关于红线是取反轴对称的(除了最高位g3)。

标签:bcd 规则 应用 之间 info 避免 关于 蓝色 bit

原文地址:https://www.cnblogs.com/YangGuangPu/p/11259514.html