标签:nbsp document inner cti alert me eth input esc ram

This document describes am335x cpufreq technology insider.

How to get current cpufreq, and to change cpufreq. Learning Processor Clocking Control(PPC) Interface Specification, learning APCI Specification.

NA

Am335x cpufreq be set by inner contex-M3,The inner contex-M3 running platform firmware. The platform firmware can be load , when booting kernel.

[ 2.118896] Power Management for AM33XX family

[ 2.127075] Trying to load am335x-pm-firmware.bin (60 secs timeout)

[ 2.137084] Copied the M3 firmware to UMEM

The Processor Clocking Control (PCC) interface is implemented by platform firmware in

order to provide a channel for the Operating System to direct and

obtain performance

information on a per-processor basis in cases where the platform

firmware would

normally be directing the control of the processor performance. In

this model the

platform firmware remains in direct control of the processor

clocking control registers.

The Operating System computes the required performance for each

processor and

communicates this to the platform firmware via the PCC shared

memory interface. The

platform firmware is responsible for managing the hardware

clocking controls in order to

deliver the requested performance. The interface also provides the

capability for the

Operating System to obtain the actual performance level delivered.

In cases where the

platform is unable to meet the Operating System request, such as a

thermal or power

budget conditions, flags are set to indicate this to the Operating

System

The Processor Clocking Control

interface relies on a reserved area in the system memory

map for communications between the platform firmware and the

Operating System.

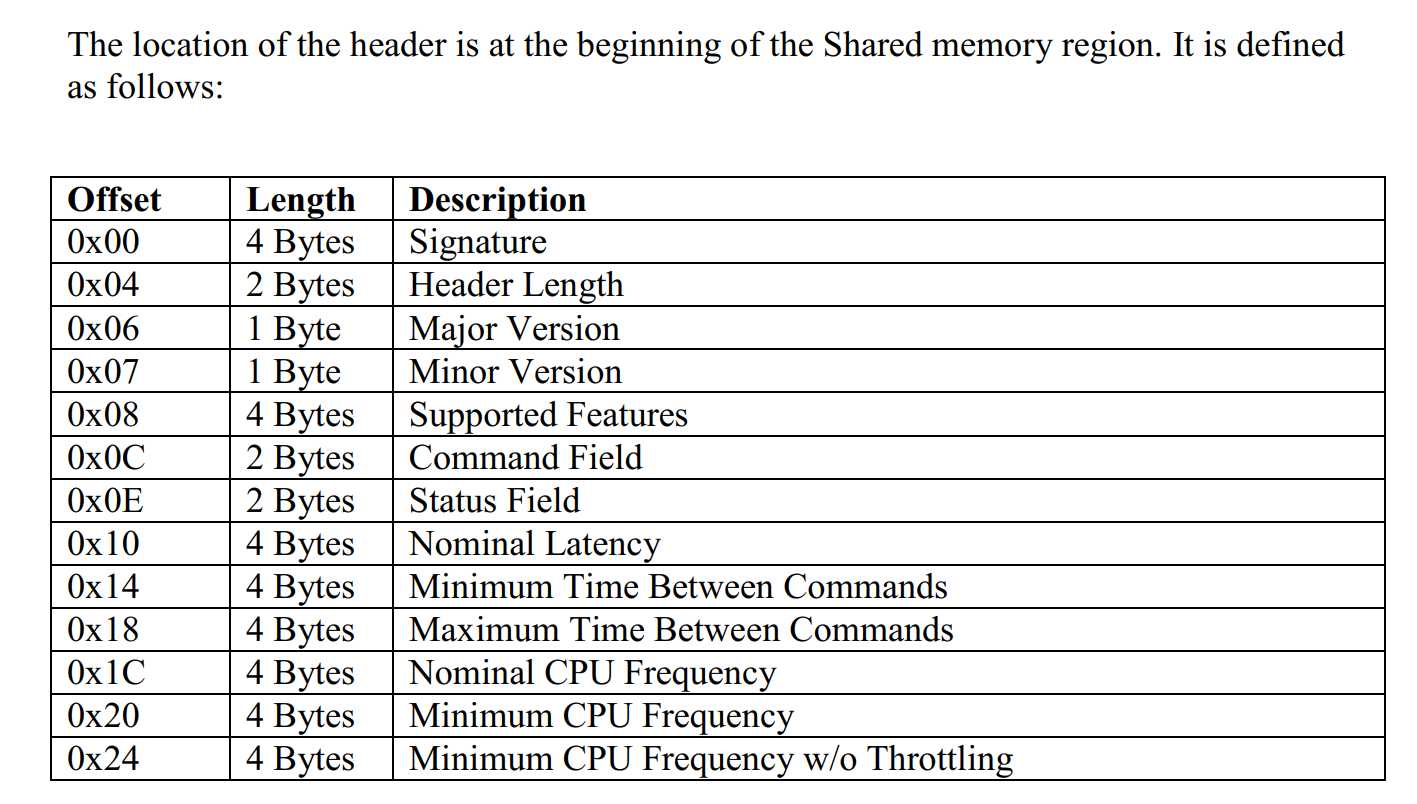

The shared memory region is a single header structure in memory. The region of

Memory is specified in she SharedMemoryRegion field obtained ty evaluating the PCCH() method. The region contains a haeder followed by one input and ome output buffer for each logical processor.

Support command :

Alert Mechanism:

NA

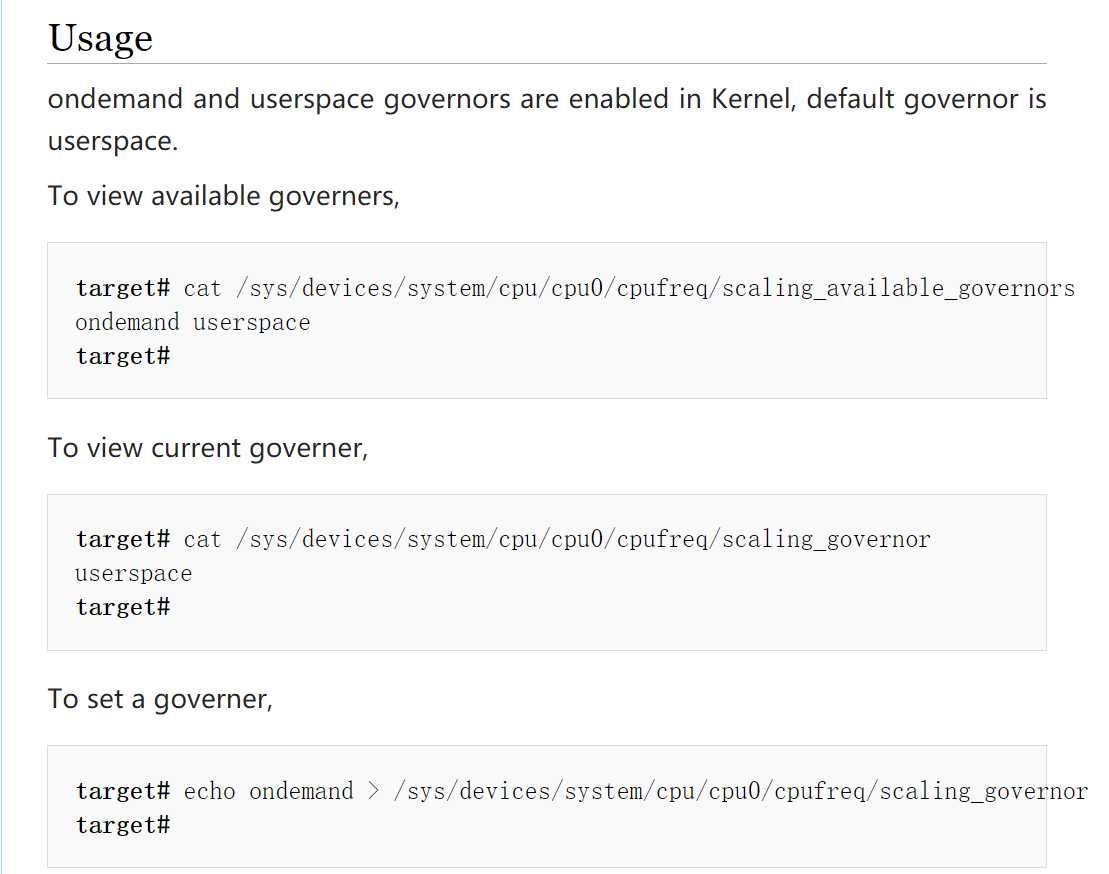

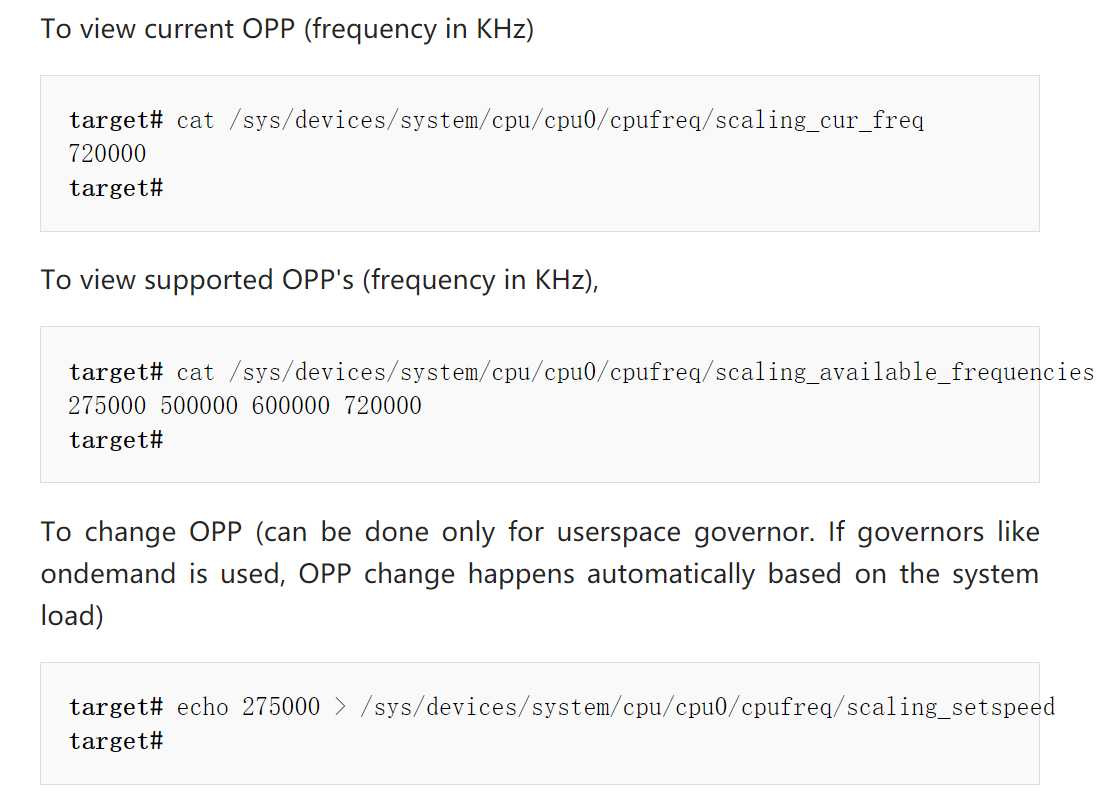

Set cpufreq mode:

am335x system upgrade set/get current cpufreq(二十一)

标签:nbsp document inner cti alert me eth input esc ram

原文地址:https://www.cnblogs.com/lianghong881018/p/11378104.html