标签:电阻 tran 之间 which 生成 tree 信号 需要 nic

STA的主要工作是计算电路网络的延时,如今的电路网络还是由CMOS cell和net组成的,所以STA所要计算的延时仍是电容的充放电时间。等量子计算机普及的时候,如今的这一套理论都将随着科技的进步被丢到故纸堆里。在量子计算机君临之前,如今的天下还是CMOS的,所以要搞STA,首先需要明白如何计算CMOS cell delay跟net delay。

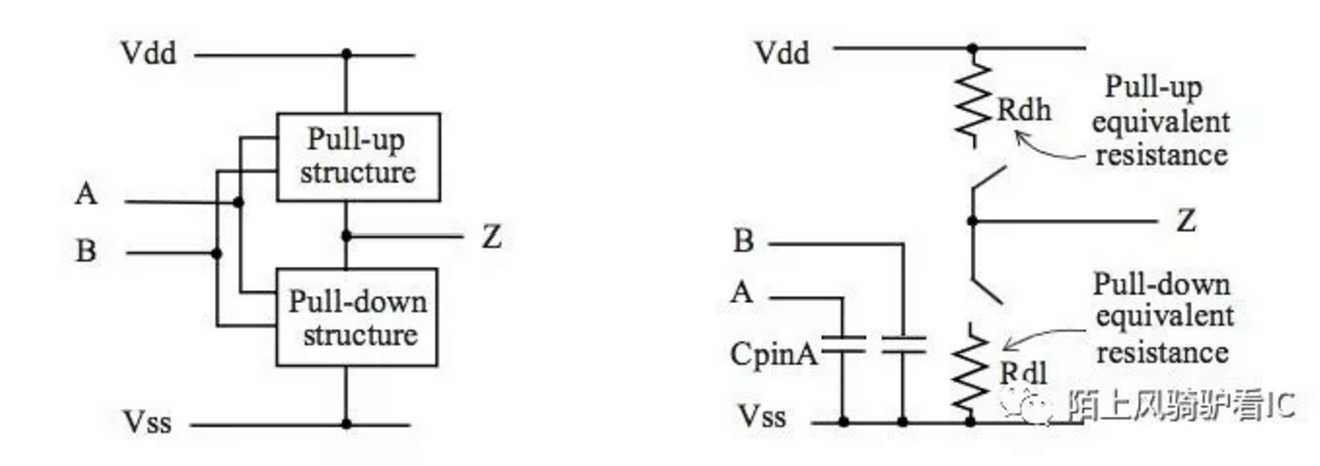

STA所有的行为都可以概括为建模和解方程,在STA眼里电路网络就是一张RC网络。cell被模拟成输入电容、输出电容、上拉电阻和下拉电阻。输入电容为前一级驱动的负载,输出电容为自身的负载,上拉电阻/下拉电阻决定了该cell对负载电容充/放电电流的大小,从而决定了该cell的负载能力,即驱动能力。

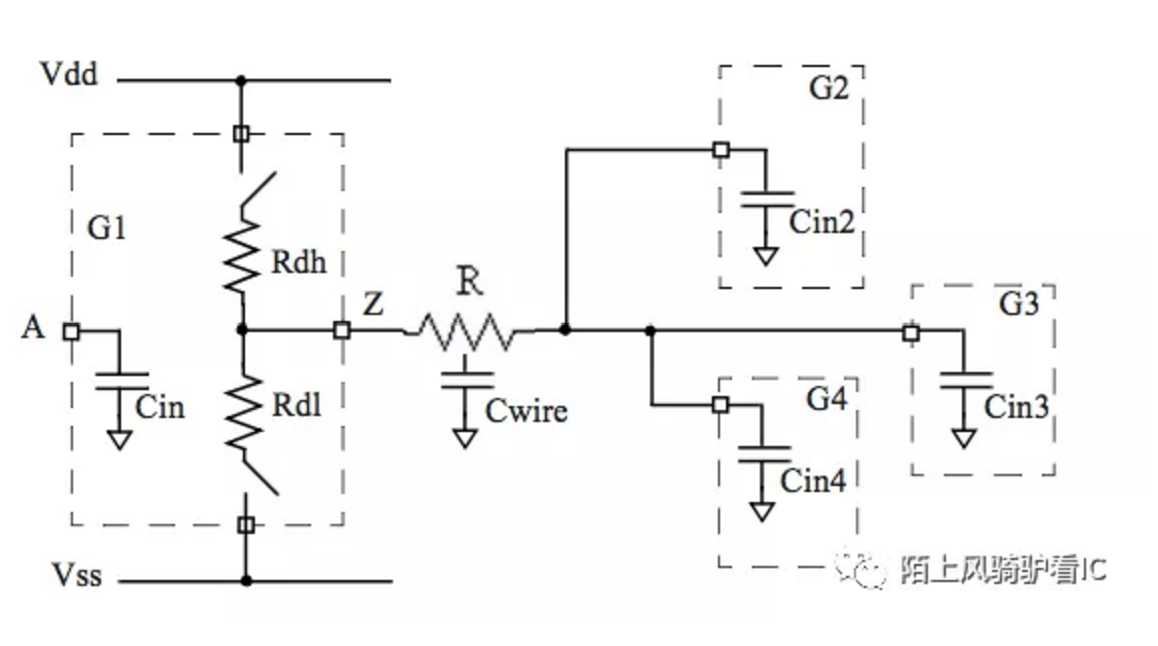

一个cell的负载,除了自身的输出电容,还包括所驱动cell的输入电容和所有相关连线的电容电阻,所谓的延时就是给负载电容充/放电的时间,根据电容充放电公式:Vout=Vdd * [1-e(-t/RC)]可知,在工作电压一定的情况下,充放电时间完全由RC决定,所以如何构建RC模型成了STA的核心。

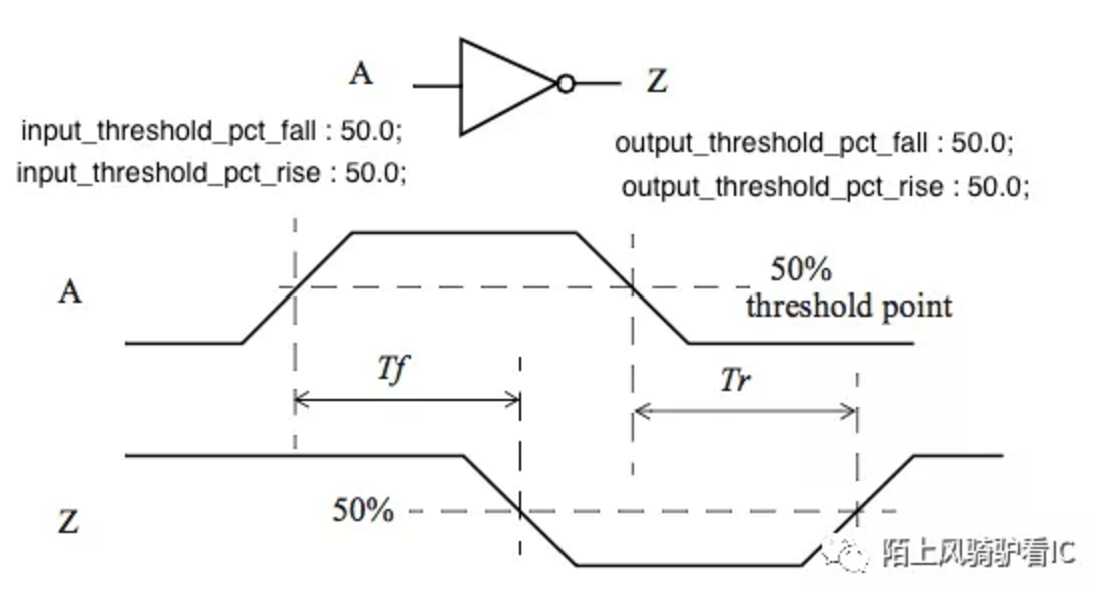

如今所用的STA方法学会分别计算cell delay跟net delay,根据cell的输入transition和输出load通过查表从library中得到cell delay和输出transition,在library的表头有四个attribute,这四个attribute决定了cell delay是如何衡量的,通常这四个值都是50%,所表诉的意思是:从输入信号电压上升/下降到工作电压的50%到对应的输出信号电压翻转为工作电压的50%之间的时间为cell delay。进一步追溯,cell delay的计算分为三部分:library的生成、输入transition的计算、输出load的计算。library不论是来自Foundary厂还是各大厂自己定制,都是经过一系列我看不懂的类似于SPICE仿真流程生成的。

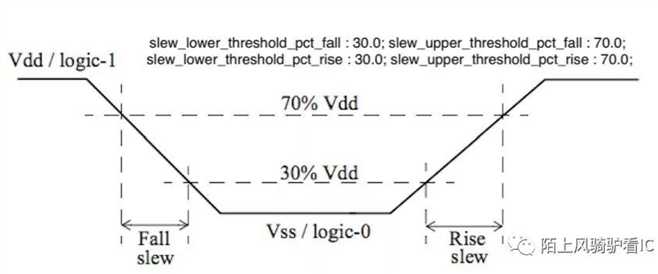

Transition的计算是逐级递进的,port的transition由硅农在SDC中指定,如set_driving_cell,第一级Port的transition来自driving cell的output transition,经由net的RC网络到达下一级cell的input pin,再从library中查得该级cell的output transition依次类推。同样在library的表头有四个变量,用以标示如何衡量rise/fall transition time。如从工作电压的30%上升到工作电压的70%为rise transtion time,从工作电压的70%下降到工作电压的30%为fall transition time。

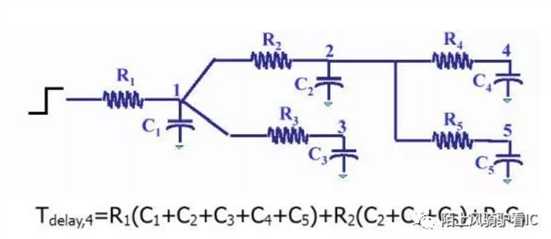

输出load包括cell自身的输出电容、连线电阻电容及其所驱动cell的输入电容,输出load的计算,关键在于如何建模,如今最常用的是elmore模型,谷歌『elmore』可以找到大量论文,有兴趣者请自行谷歌,摘抄一段维基百科的描述:『Elmore delay is a simple approximation to thedelay through an RC network in an electronic system. It is oftenused in applications such as logic synthesis, delay calculation, static timing analysis, placement and routing, sinceit is simple to compute (especially in tree structured networks, which are the vast majority of signal nets within ICs) and isreasonably accurate. Even where it is not accurate, it is usually faithful, inthe sense that reducing the Elmore delay will almost always reduce the truedelay, so it is still useful in optimization.』

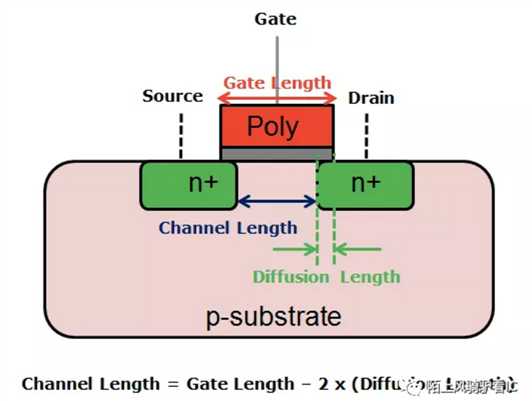

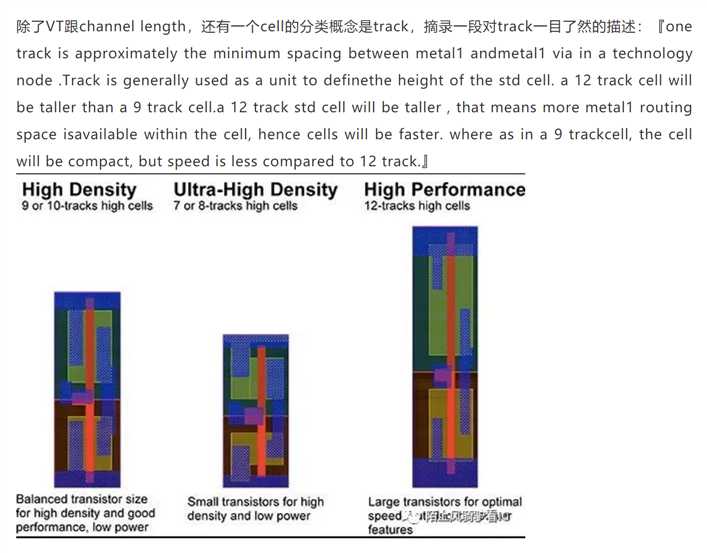

做STA之前十分有必要对库进行必要的分析,如果有多种VT,要知道相同size的cell不同VT之间的timing/leakage差别、同一VT的cell 不同size之间的timing/leakge的差别、如果有多种channel length,要知道相同size的cell不同channel length之间的timing/leakage差别。不同VT的cell由于mask的不同,使得阈值电压不同,从而得到不同的performance跟leakag。另两个容易混淆的概念是channel length跟effect channel length:通常说工艺是多少nm,其中一个重要的表征就是channel length,而effect channel length则是指沟道实际的长度,有效沟道长度越短,管子速度就越快,leakage也越大。谷歌找到这张图表述的更清晰,将两个长度一个叫gate length一个叫channel length,两者间的关系在图中也一目了然。

标签:电阻 tran 之间 which 生成 tree 信号 需要 nic

原文地址:https://www.cnblogs.com/lelin/p/11391873.html