标签:style blog http color io os ar 使用 strong

[转]亚稳态分析 | 发布时间:2011-05-12 19:56:15 |

技术类别:CPLD/FPGA | ?? |

1,简介

这篇文章是我对电子设计中,亚稳态问题的一种分析和总结。文章通过对数字电路中器件的工作机制的介绍,引出亚稳态问题的发生机制。并通过对亚稳态问题发生机制的探讨,用以得到一种能够清楚地,有的放矢地解决亚稳态问题的能力。而这种能力,将会成为你作为一个工程师的价值所在。希望通过这个探讨,可以使你设计出属于自己的预防亚稳态的方法。对于常用的预防亚稳态的方法,由于网上已经有大量介绍,并且涉及到具体问题的分析,这里将不做重点介绍。

? ?

2,CMOS中的信息保存

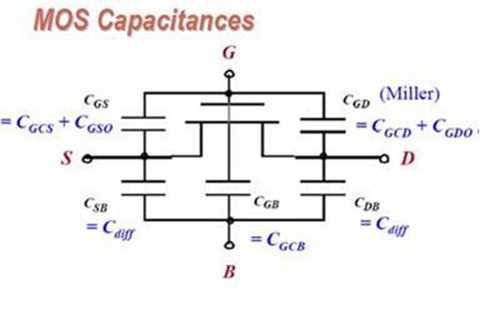

Fig.?1.?MOS管的电容模型

当一个MOS工艺晶体管被制造之后,在不同极之间,因为介电物质的存在,会形成电容。当晶体管工作时,这些电容会被充/放电。当充放电回路上的R,C有不同取值的时候,回路的时间常数(由RC表示)会不同。

? ?

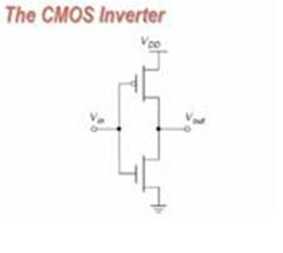

在数字电路中,最简单的结构是反向器(inverter)。在CMOS工艺中,它由一个NMOS加一个PMOS组成。

? ?

Fig.?2.?反向器

对于这个反向器,可以简化成由工作电阻Ron,结点电容CL组成的充放电电路。

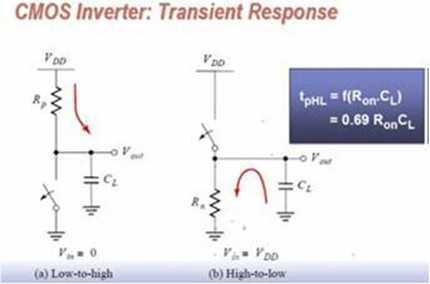

Fig.?3.?反向器充放电模型

? ?

当Inverter输入为0时,PMOS导通,对CL充电,时间由Rp*CL决定

当Inverter输入为1时,NMOS导通,对CL放电,时间由Rn*CL决定

其中CL由P/NMOS的漏极结点上所有相关的电容组成,这是一种近似的计算方法(将分布的电容进行集总)。

CL=Cdb+Cgd(Miller效应)+Cwire+Cg_fanout

? ?

从这里我们得到

1,任何信号都需要时间才能从输入端口传递到输出端口。

2,对CL的充放电影响系统的动态(翻转)功耗,如果想降低功耗,可以对不使用的信号添加使能。

3,由于Rp?!=?Rn,所以Rp*CL?!=?Rn*CL,所以rising?time?!=?falling?time

对于分析亚稳态的问题,只需要记住第一条,任何信号从输入端口传递到输出端口都需要一定的时间。对于任何其他门电路,分析过程都一样。

? ?

3,SETUP/HOLD?时间的意义

S/H时间是时序器件的属性。下面我们来说一下,这两个时间是如何产生的。

任何器件"原则"上都是电平有效的,边沿触发的器件是一种"把戏"。

? ?

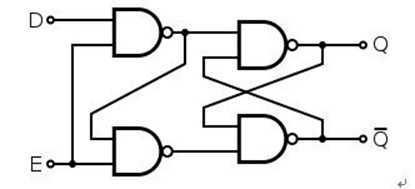

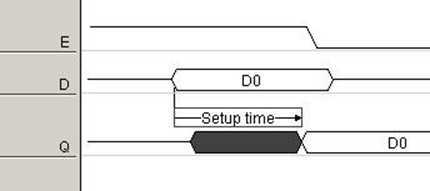

首先我们看一下D锁存器。

Fig.?4.?D锁存器

真值表:

E??D??Q

0??x??PreQ

1??0??0

1??1??1

? ?

时序表示(局部)

Fig.?5.?D锁存器时序图

当E维持在高电平的时候,D端在某一时刻,输入一个值D0。这个值从D端与非门进入,在器件内会有一个延迟,再加上反馈回与非门一个输入端的信号与另一个输入端的信号可能存在不一致,使得在整个D锁存器的建立过程中,Q端输出的电压会存在一个"不稳定阶段",我们可以把它叫做Setup?time,这个不稳定阶段的"长度"与上一节提到的器件传输时延,和D端输入电平,Q端初始电平有关(假设E端电平始终不变)。注意,这个时间段的起始位置在D开始有效的那一点上。因为D输入后,还要经过一个时间段,Q端才开始"震荡"。

? ?

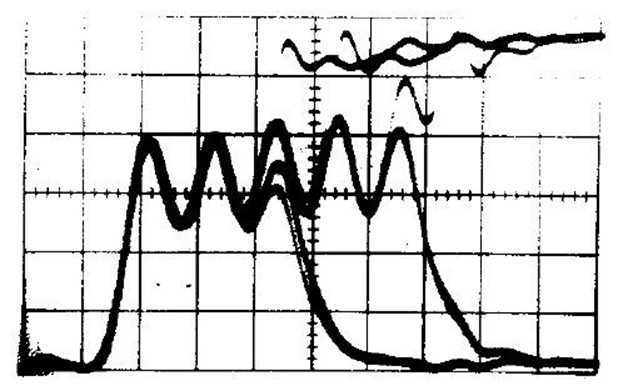

Fig.?6.?D锁存器在设置电平的阶段,输出端的电平

? ?

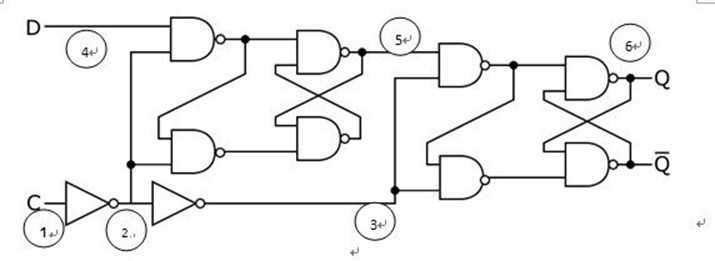

在时序电路中,我们经常用到的D触发器,就是通过诸如D锁存器一样的电平器件所组成的。这里我们提供一个典型的由D锁存器所组成的上升沿有效的D触发器模型。

? ?

Fig.?7.?上升沿有效的D触发器(DFF)

在D锁存器时序的基础上,分析一下D触发器的时序(局部)

Fig.?8.?上升沿有效的D触发器的时序图

? ?

Fig.?8?中的2/E1,4/D1,5/Q1/D2与D锁存器中的时序一模一样。

从时钟端口1上升沿(50%)开始,到窗口时间前面那一点结束,这段时间就是DFF的设置时间。

从时钟端口1上升沿开始,到窗口时间后面的那一点结束,这段时间就是DFF的保存时间。

从时钟端口1上升沿开始,到输出点Q稳定结束,这段时间就是DFF的clock?to?output时间,可用Tcko,Tco表示。

分析过程同D锁存器。

? ?

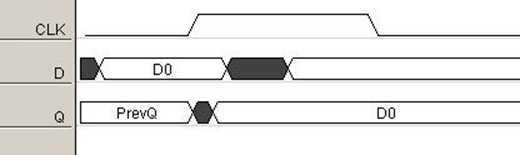

通常来讲,对于一个高速器件,这个时间窗口都会非常小。现在我们把时间窗口缩到正常比例,并略去DFF内部时序,只关注D,Q,CLK,我们会得到下面这个图。

Fig.?9.?在时序仿真中,可能出现的实际时序图

? ?

到这里,我们说一下"负保持时间"。如果在纯时序器件前端加上一些组合逻辑,从而组合成一个有一定功能的时序器件。那么因为前面这个组合逻辑会占用一部分传输时间,因此从这个不纯的时序器件上看,采样窗口就会相对时钟上升沿提前,当采样窗口的尾部可以提前到时钟上升沿之前的时候,就会出现负保持时间(设置时间永远在上升沿前面,永远是正的)。这说明:"不纯的时序器件内部的组合逻辑的传输时间"大于"纯时序器件原来的保持时间的绝对值"。

从这里,我们可以得到,

1,主从结构的时序器件的S/H?时间和其内部第一级锁存结构的设置时间,以及其可能含有的Inverter的传输时间有关。

2,主从结构的时序期间的CKO时间和其内部第二级锁存结构的设置时间,以及其可能含有的Inverter的传输时间有关。

3,主从结构的时序器件的第一级锁存结构的设置时间是影响其采样窗口的主要因素。数据在这个采样窗口被捕获进触发器。

4,任何在采样窗口时间内的电平异常,都可能引起采样异常,这就是导致亚稳态的最根本原因。

? ?

4,亚稳态的产生

如果说实际电路中的信号曲线像成年人一样复杂,那么时序仿真中的曲线就像小学生一样简单,而逻辑仿真中的曲线简直就像婴儿一样可爱。

? ?

然而优秀的工程师的过人之处就是知道"什么时候""该用什么样的方法"去化简并分析问题。

? ?

下面我们设想一下,在窗口时间内,如果输入电平一直是不稳定的,会发生什么事?

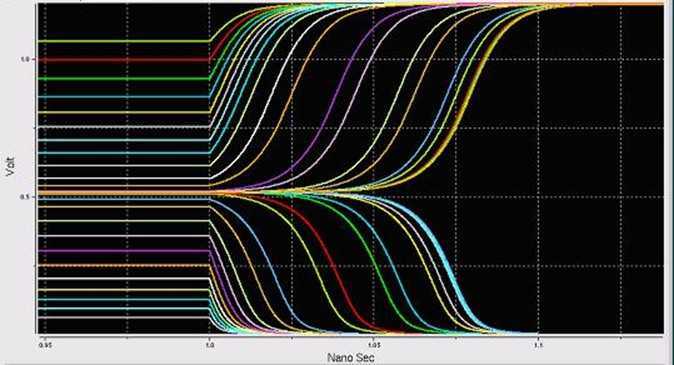

Fig.?10.?不同初始电平导致不同决断时间

? ?

如Fig.?10,假设当DFF第一级的E关断时,D点的不同输入电平会"定格"在那个值上(具体真实情况,需要查看第一级器件内部结构),这个初始值会影响第一级锁存器的设置时间,或者说决断时间。因为如果这个初始值恰好在中间电平,那么第一层与非门的输出端就会经过一个较长时间才能达到应有的电平高度,再加上互相反馈输入的联合影响,最后整个锁存器的设置时间都会被拉长。

? ?

另外,由于系统随时都存在各种噪声,因此加上噪声会导致最后的电平与输入逻辑无关。但由于锁存器件有一种正反馈效应,因此初始信号越清晰,输出信号会被越快的设置好,受噪声的影响越小。所以从概率上讲,决断时间不会无限长。

? ?

但是如果不加控制,这个不稳定的电平可能会对后面器件的电平设置带来不可预测的后果。

? ?

从这里我们可以看到:

1,采样窗口应该越小越好,这样会减少采样异常的可能性。但是由于系统时钟同样越来越快,从而这个采样窗口所占时钟周期的比例,变化并不会非常大(数量级的变化)。

2,如果我们能保证采样窗口内的数据是绝对稳定的,那么就可以完全避免亚稳态。但这一条在有异步电路,或者有跨时钟域的情况发生时,是很难完全保证的。

3,亚稳态有两种危害,"输出较长时间的不稳定电平"和"逻辑错误"。

? ?

以上是在器件的角度分析为什么会产生亚稳态。下面我们再升高一个级别,到RTL级去看看为什么会产生亚稳态。

? ?

5,相同时钟域内的亚稳态------S/H时间违约

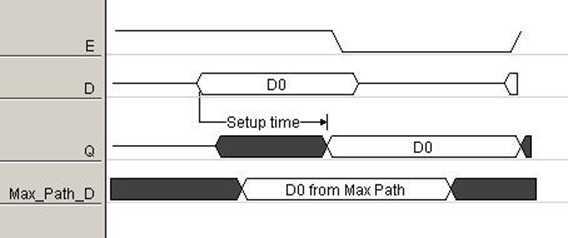

想象一下,在两个相邻的DFF中间,有一条很长很复杂的组合逻辑器件链条。因此从前一级DFF出发的数据,需要经过很久很久才能在后一级DFF的输入端稳定下来。这个时间甚至要接近时钟周期(如果时钟周期只比关键路径长一点,这种情况是很可能的)。那么这个信号在采样窗口开始之后,才稳定下来,因此DFF第一级没有足够时间正确无误地设置电平,从而导致亚稳态的出现。这种情况叫做设置时间违约(setup?time?violation)

Fig.?11.?Setup?time?violation

? ?

由于这种情况的发生是由于组合逻辑传输时间过长引起的,所以在设计时,只需要考察最长的那些路径。

? ?

下面来看另一种情况。如果在第一周期上升沿,从前一级触发器出发的D0到达了下一级(这时时钟周期已经接近下一周期的上升沿了)。这时有一个在第二周期上升沿,从前一级触发器出发的D1经过一个非常短的路径到达了下一级。如果这个传输时间小于保持时间,那么,在上一个D0还没有完全结束采样的时候,D1会过来破坏这个采样。因此产生保持时间违约(hold?time?violation)。

? ?

由于这种情况的发生是由于组合逻辑传输时间过短引起的,所以在设计时,只需要考察最短的那些路径。

? ?

当我们清楚了S/H时间违约的原理后,就很容易想出预防的办法。

对于设置时间违约,这是ASIC时序分析中最主要问题。如果从最长路径上传过来的信号到达的时间太晚,以至于错过了采样窗口,就会发生设置时间违约。如何处理这种错误显而易见,那就是让他更早的到达,或者说更早的在下一级输入端口稳定下来。如何才是更早?

1,增加时钟周期的长度,但这意味着整体速度下降。因此一般不这么做。

2,重新分配关键路径,将过长的路径中的一部分组合逻辑从路径中分离出来,放到相邻的时序级里面,或者单独形成一级(CPU中的多级流水就是基于这种技术),使得每一级里面的路径长度(其实是耗时长度)相差无几。但前提是不破坏逻辑功能,和系统功能。

3,如果这些都做不到,那就只能从组合逻辑的结构上下手,调整结构。

对于保持时间违约,处理方法也很明显,那就是让他更晚的到达,或者说更晚的在下一级输入端口稳定下来,来防止对上一个数据造成影响。增加传输时间总是比减少传输时间简单。因此通常的做法是在传输路径上增加buffer,其实就是由两个反相器构成的器件,不影响逻辑功能,只增加延迟。Buffer还有一个功能,就是当信号线过长的时候,其上的RC会增加,因此为了保持接收端的信号完整性,比如增强输出端的驱动能力(供给电流的能力),如果输出端的器件没有高驱动能力的版本(EDA公司提供的库中,很多器件都有多种驱动能力的版本),则可以通过增加buffer来分割长信号线,用以"分段驱动"。

? ?

由于亚稳态的出现是一种概率现象,并且结果正确与否也是一种概率现象,因此为了便于估算,提出了一种统计模型来预测亚稳态所造成的危害的程度,这就是平均无故障时间"MTBF"。关于这个公式的推导,网上可以找到资料,这里忽略。记住一点,MTBF=1/失效率。后面介绍为什么使用二级DFF的时候还会提到。

? ?

其实对于相同时钟域内的时钟树来讲,在不同点也存在相位差别。但这种差别可以通过计算时钟信号线的长度来进行预测,并可通过时钟域内的时钟树综合算法来求得优化的结构。因此相对来讲,比较好解决。

? ?

对于跨时钟域通信,异步同步通信来讲,情况变得相对复杂。跨时钟域也是一种异步同步通信。两个时钟域内的时钟没有必然的频率关系和相位关系。造成这种情况的原因在于,在工程上,对待同一个时钟域的分析就已经比较复杂,目前有一些方法来优化时钟树,但当引入多个时钟的时候,如果进行联合分析,问题的复杂性会变得很大。因此工程上采用"各自独立分析优化,在此基础上进行互相通信设计"。

? ?

下面分析一下异步同步交界面,跨时钟域交界面的亚稳态分析。

? ?

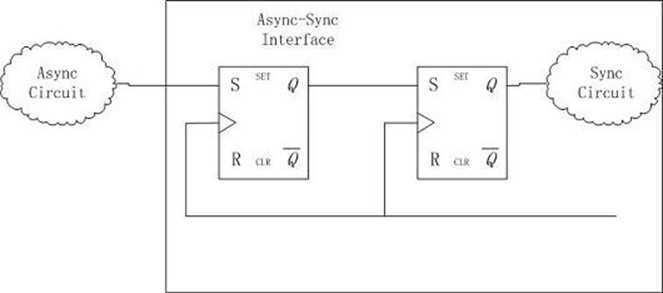

6,同步异步交界面的亚稳态

想象一下,在一个同步异步交界面上,或者跨时钟域的交界面上,外部发来的数据的到达时间,是很难与本地时钟产生什么必然的时序上的关系的。或者更确切的说,外部数据在本地输入端口的稳定时间与本地时序器件的采样窗口在时序上没有必然的联系。因此造成了同步异步接口间,跨时钟域接口间的亚稳态问题。

Fig.?12.?异步同步信号间的接口

? ?

如何解决这个问题的方法也是显而易见的,那就是:保证本地时序器件的采样窗口内所接受到的数据是绝对稳定的。但是做到这一点是极其困难的。对于异步同步交界面,由于异步数据与本地同步信号之间没有任何联系,因此原则上,是无法保证稳定采样的。对于跨时钟域的交界面,由于两个时钟之间的相位没有必然的联系,两个时钟之间的频率没有必然的联系,因此原则上,也是无法保证稳定采样的。

下面说一下常用的解决办法,由于涉及到具体问题的分析,并受到篇幅的限制,所以具体内容从略。

一,?同步器

同步器就是将几个用本地时钟驱动的时序器件串联起来,去采样输入的异步数据。为什么会有这种方法呢。回忆决断时间的概念。当在第一级的时序器件出现亚稳态的问题时,其输出会出现一种不稳定的中间值,并且这个时间受多种因素影响,或者说这个输出在高电平到低电平之间满足一定形式的概率分布。当第二个时序器件的采样窗口到来的时候,在第二级输入端口上的电平仍然处在可以使第二级出现亚稳态的电平范围内的概率会变得很小,如果再加上第三级,在第三极上的这个概率几乎可以忽略不计。从数学上讲,每个时序器件的亚稳态的出现都有一定的概率,如果多个期间串联,总概率是各自概率的积,因此增加期间,会消除"亚稳态"。但是这里的消除是指降低不稳定的时间,使得输出电平的稳定时间接近时钟周期。至于能否采样到正确的逻辑,则基本取决于第一个时序器件的输出。前面分析过,当亚稳态出现时,输出逻辑与输入逻辑的关系是不确定的。因此在逻辑上无法消除亚稳态的影响。

? ?

前面提到MTBF=1/失效率,当多个DFF串连时,

MTBF=1/(失效率1×失效率2×…×失效率n)

当两个DFF串联的时候,基本可以保证这个MTBF很大。对于量产的产品,全部产品无故障的时间为MTBF/产品量,因此如果产量较大,则需要有非常大的MTBF。

? ?

如果这种方法作用在控制信号上的时候,如果出现采样失效(比如跨时钟域时,采样率不匹配),则可以多等待几个周期,以保证有效采样到逻辑信号。还有机会完成控制操作。如果是数据信号,则这种方法很难保证无差错传输。

? ?

二,异步FIFO与握手协议

这两种方法可以用来传输对传输质量要求较高的数据信号,并且主要用在跨时钟域传输中。因为这种传输模式下,发送源,与接收目的地都需要有时钟控制。

异步FIFO方法是一种总线思维,当然是一种比较简单的结构。握手协议是一种逻辑方法,与TCP握手类似。

网上资料比较多,相对也比较好理解,就不多说了。

? ?

三,延迟锁定环Delay?locked?loop

DLL是一种使用在跨时钟域传输模式下的避免亚稳态的方法。很好理解,如果能够统计出在交界面上的信号的有效时间与发送源时钟信号周期的相对关系,就可以通过"将目的地时钟信号与发送源时钟信号的延迟关系进行锁定"来保证"在目的地的采样周期永远在信号有效的时间范围内"。这是一种将两个非同步时钟进行同步的一种方法。

? ?

网上有资料,就不多说了。

7,复位信号与亚稳态

当理解亚稳态的形成机制后,再理解复位信号可能导致的亚稳态问题就变得非常简单。

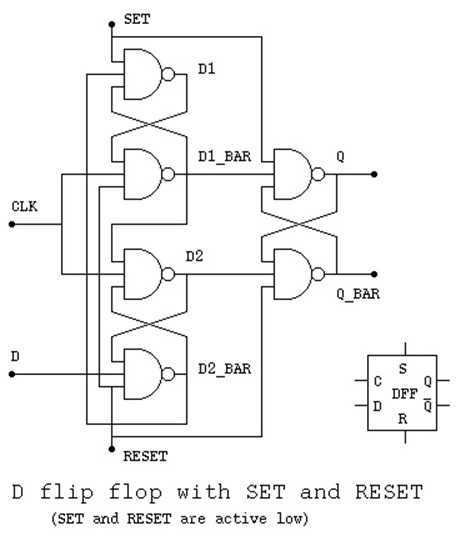

Fig.?13.?带复位信号的D触发器

? ?

由于复位信号是在随机状态下产生的,因此对系统的影响,及分析过程与异步同步交界面的亚稳态问题类似。网上分析很多,读者也可以自行分析。

? ?

8,结语

亚稳态产生的主要原因是,在时序器件的采样窗口内,无法保证输入信号始终保持在一个稳定的电平上。因此我们需要通过减小采样窗口来增加采样成功率(使用边沿触发器件对于电平触发器件来说,也是一种减小采样窗口的方法),或者通过对采样窗口或输入数据的稳定窗口的"移动"来保证采样成功,用以解决亚稳态问题。但在有异步信号的参与时,问题的解决将变得异常复杂。因此目前还没有一种通用的,有效的,可行的解决方法。但通过对亚稳态形成机制的探讨,可以使我们游刃有余的从工程的角度上解决实际项目中可能出现的具体的亚稳态问题。

? ?

来自 <http://bbs.ednchina.com/BLOG_ARTICLE_2041196.HTM>

? ?

标签:style blog http color io os ar 使用 strong

原文地址:http://www.cnblogs.com/shanesblog/p/4050235.html