标签:style blog http color os ar sp div on

module multiplier( input clk,rst, input [7:0] A,B, output [16:0] C); reg [3:0] cnt; reg [16:0] temp; always@(posedge clk or negedge rst) if(!rst) begin cnt<=0; temp<=0; end else if(cnt==8) cnt<=0; else if(B[cnt]) begin temp<=temp+(A<<cnt); cnt<=cnt+1; end else cnt<=cnt+1; assign C=(cnt==8)?temp:0; endmodule

1 `timescale 1ns/1ns 2 module multiplier_tb; 3 reg [7:0] A,B; 4 reg clk,rst; 5 wire [16:0] C; 6 7 multiplier U( 8 .A(A), 9 .B(B), 10 .clk(clk), 11 .rst(rst), 12 .C(C) 13 ); 14 15 initial 16 begin 17 rst=0; 18 clk=0; 19 A=8‘hfc; 20 B=8‘hcf; 21 #5 rst=1; 22 end 23 always 24 #10 clk=~clk; 25 26 endmodule

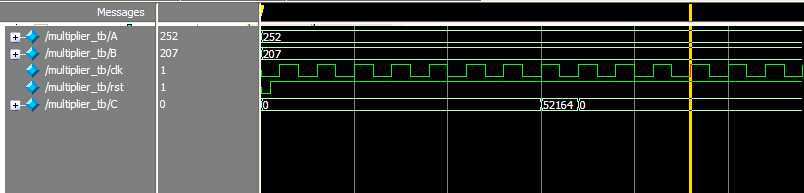

图中在第8个脉冲就输出了乘积,为什么这样呢?由程序可知,temp和cnt在一个进程内被赋值,也即:第8个clk沿到达后,temp和cnt同时完成赋值,一个是得出乘积,一个是cnt=8;又由于assign的即时性,所以在第8个clk,已得出乘积。

要考虑乘数的位权,小学都知道乘法算式要错位的写,现在怎么不知道了!!

简单无符号乘法器(怎么总是有疏漏,神啊!必须要level up了!)

标签:style blog http color os ar sp div on

原文地址:http://www.cnblogs.com/fkl523/p/4050733.html