标签:reduce code idt rmi 如何 单位 而且 ref 通过

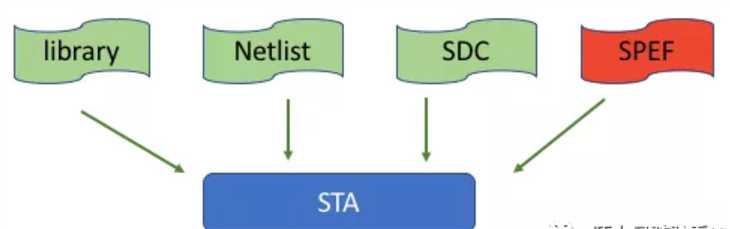

RC corner,这里的RC指gate跟network的寄生参数,寄生参数抽取工具根据电路的物理信息,抽取出电路的电阻电容值,再以寄生参数文件输入给STA工具,常见的寄生参数文件格式为SPEF。

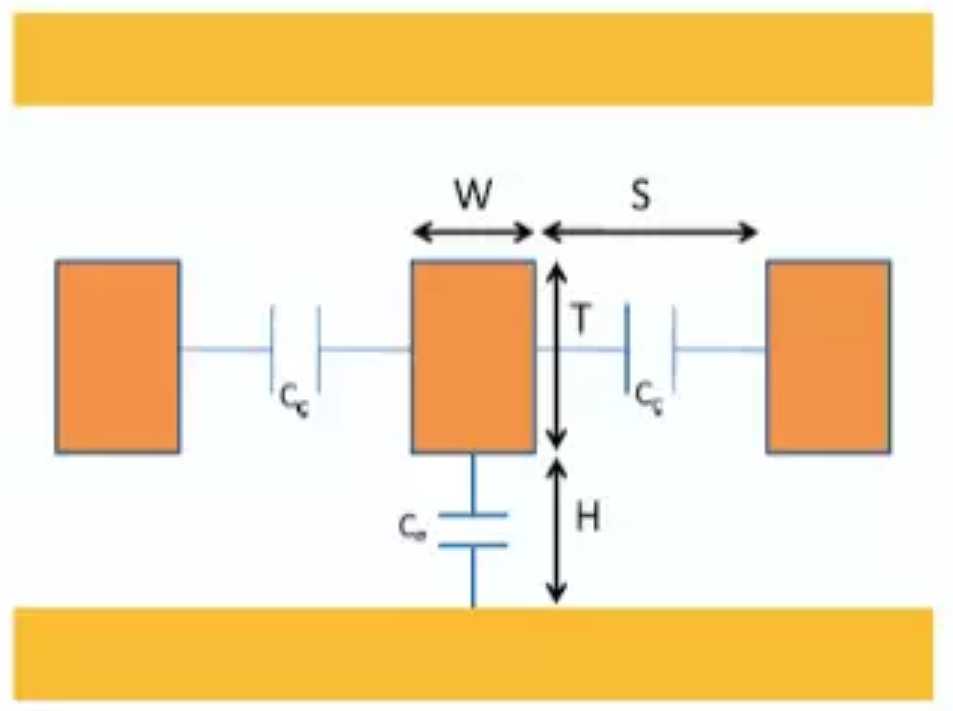

ICer都知道在集成电路中是多层走线的,专业术语叫metal layer,不同工艺有不同层metal layer,任何两层metal layer间由介电材料隔离,『走线』通过过孔(VIA)连接。Width跟Spacing是衡量绕线的两条最重要的物理设计规则,它们随着工艺的进步逐步减小。 介电材料、绕线材料、线间距、线宽及线的厚度这些物理特性决定了network的RC值。

Network电容:

耦合电容:Coupling capacitance=e*T/S

表面电容:Surface capcitance=e*W/H

边缘电容:Fringe capcitance

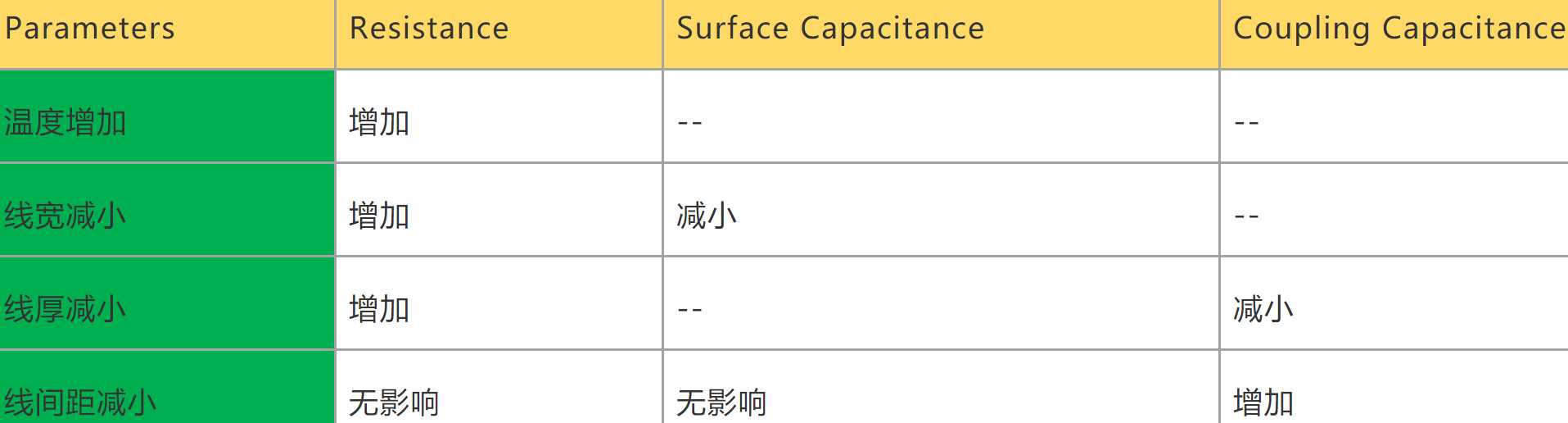

决定容值的因素:

介电常数:e

线宽:W

线厚:T

线间距:S

介电材料的厚度:H

随着工艺进步,W, S, T 逐代递减,表面电容跟随减小,耦合电容随之增加,耦合电容在总电容中占比增加,当线厚 T 一定时为了减少耦合电容要么增加线间距要么减小介电常数。通常为了减小噪声敏感信号线(如clock net)上的耦合电容,在物理实现时会人为增加对应信号的线宽及线间距,俗称NDR。要减小介电常数需要从材料入手,从 .18开始引入low K介电材料。

Network电阻:

R=r/W*T, r为电阻率,除了跟线宽 W 和线厚 T 相关之外,还跟温度相关,随着温度的上升而增大。

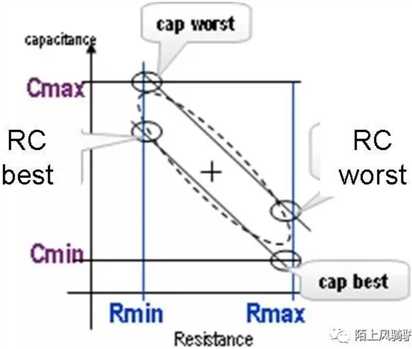

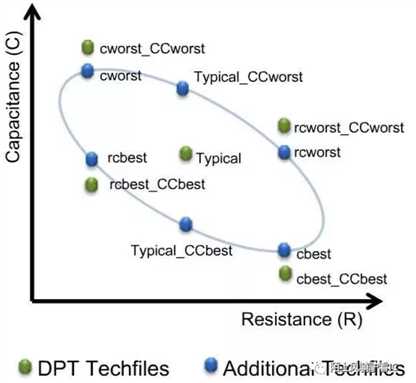

由上面的分析可知,Network的单位电容和单位电阻是不可能同时最大或同时最小的。有了这些铺垫,来看一下不同工艺结点是如何定义RC corner的。

90nm 之前,Cell delay占主导,Network电容主要是对地电容,STA只需要两个RC corner即可:

Cbest(Cmin): 电容最小电阻最大

Cworst(Cmax):电容最大电阻最小

90nm 之后,netdelay的比重越来越大,而且network的耦合电容不可忽略,所以又增加了两个RC corner:

RCbest(XTALK corner): 耦合电容最大,(对地电容*电阻)最小

RCworst(Delay corner): 耦合电容最小,(对地电容*电阻)最大

至此总共有两个需要setup timing sign-off的RC corner,有四个需要hold timing sign-off的RC corner:

Setup time sign-off 的RC corner是: Cworst / RCworst

Hold time sign-off 的RC corner是: Cbest / RCbest / Cworst / RCworst

C-best:

It hasminimum capacitance. So also known as Cmin corner.

InterconnectResistance is larger than the Typical corner.

Thiscorner results in smallest delay for paths with short nets and can be used formin-path-analysis.

C-worst:

Refers tocorners which results maximum Capacitance. So also known as Cmax corner.

Interconnectresistance is smaller than at typical corner.

Thiscorners results in largest delay for paths with shorts nets and can be used formax-path-analysis.

RC-best:

Refers tothe corners which minimize interconnect RC product. So also known as RC-mincorner.

Typicallycorresponds to smaller etch which increases the trace width. This results insmallest resistance but corresponds to larger than typical capacitance.

Corner hassmallest path delay for paths with long interconnects and can be used formin-path-analysis.

RC-worst:

Refers tothe corners which maximize interconnect RC product. So also known as RC-maxcorner.

Typicallycorresponds to larger etch which reduces the trace width. This results inlargest resistance but corresponds to smaller than typical capacitance.

Corner haslargest path delay for paths with long interconnects and can be used formax-path-analysis.

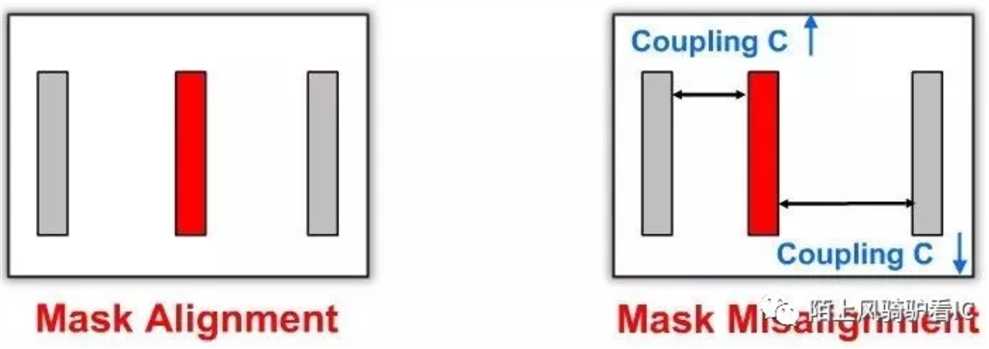

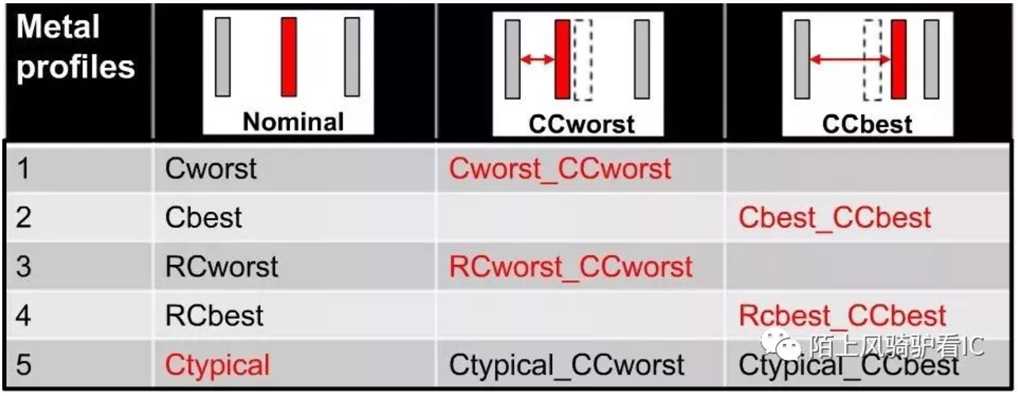

引入的DPT(Double Patterning Technology)之后,在同一层layer上要做两次mask,两次mask之间的偏差,会导致线间距变化,从而影响耦合电容值,需要将这一因素考虑到RC corner中,所以DPT 的RC corner是:Cworst_CCworst, RCworst_CCworst, Cbest_CCbest, RCbest_CCbest.

其中:

Setup timesign-off 的RC corner是: Cworst_CCworst / RCworst_CCworst

Hold timesign-off 的RC corner是: Cbest_CCbest / RCbest_CCbest / Cworst_CCworst /RCworst_CCworst

除以上这些corner外,还有一个corner叫Typical corner,对应于DPT的是Ctypical_CCworst, Ctypical_CCbest,这些corner不用于timing sign-off。

标签:reduce code idt rmi 如何 单位 而且 ref 通过

原文地址:https://www.cnblogs.com/lelin/p/11421362.html