标签:into war hardware 技术 cloc his opera round ble

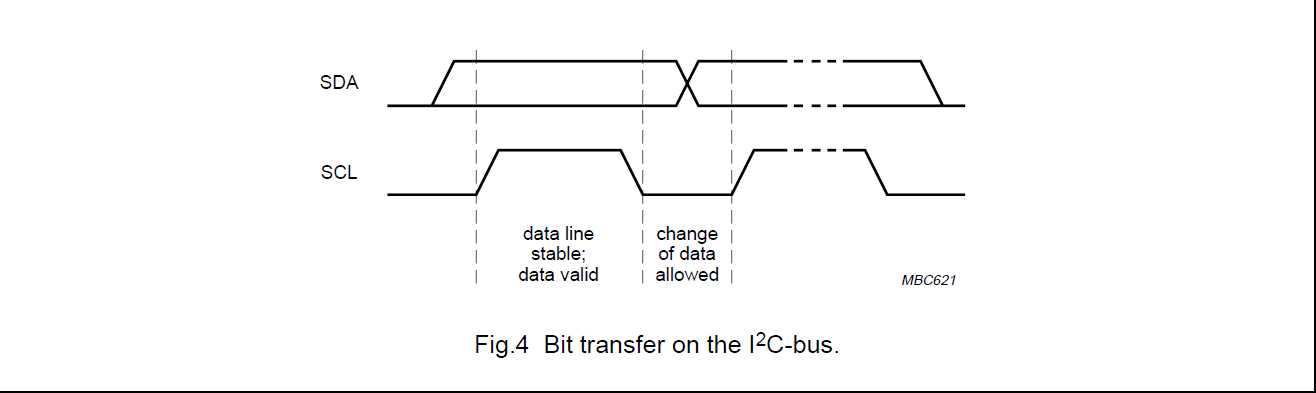

The data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW(see Fig.4).

Within the procedure of the I2C-bus, unique situations arises which are defined as START(S) and STOP(P) conditions(see Fig.5).

A HIGH to LOW transition on the SDA line while SCL is HIGH is one such unique case. This situation indicates a START condition.

A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition.

START and STOP conditions are always generated by the master. The bus is considered to be busy after the START condition. The bus is considered to be free again a certain time after the STOP condition. the bus free situation is specified in Section 15.

The bus stays busy if a repeated START(Sr) is generated instead of a STOP condition. In this respect, the START(S) and repeated START(Sr) conditions are functionally identical(see Fig.10). For the remainder of this document, therefore, the S symbol will be used as a generic term to the represent both the START and repeated START conditions, unless Sr particular relevant.

Detection of START and STOP conditions by devices connected to the bus is easy if they incoperate the necessary interfacing hardware. However, microcontrollers with no such interface have to sample the SDA line at least twice per clock period to sense the transition.

Every byte on the SDA line must be 8-bits long. The number of bytes that can be transmitted per transfer is unrestricted. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit(MSB) first. If a slave can‘t receive or transmit another complete byte of data until it has performed some other function, for example servicing an internal interrupt it can hold the clock line SCL LOW to force the master into a wait state. Data transfer then continues when the slave is ready for another byte of data and release clock line SCL.

标签:into war hardware 技术 cloc his opera round ble

原文地址:https://www.cnblogs.com/bootblack/p/11461285.html