标签:语句 cin 验证 alt 时钟 end sed 如何 top

写在前面的话

缩减运算符是单目运算符,也有与或非运算。其与或非运算规则类似于位运算符的与或非运算规则,但其运算过程不同。位运算是对操作数的相应位进行与或非运算,操作数是几位数则运算结果也是几位数。而缩减运算则不同,缩减运算是对单个操作数进行与或非递推运算,最后的运算结果是一位的二进制数。缩减运算的具体运算过程是这样的:第一步先将操作数的第一位与第二位进行与或非运算,第二步将运算结果与第三位进行与或非运算,依次类推,直到最后一位。例如:

reg[3:0]B;

reg C;

C=&B;

相当于

C=((B[0]&B[1])&B[2])&B[3];

工程实例

下面,梦翼师兄给大家编写一个实例,通过仿真波形来验证运算结果是否如我们所说。可综合模块代码如下

|

/**************************************************** * Engineer : 梦翼师兄 * QQ : 761664056 * The module function:缩减语句运算模块 *****************************************************/ 01 module reduce(clk,rst_n,c); 02 input clk;//系统时钟输入 03 input rst_n;//系统复位 04 05 output reg c;//输出寄存器定义 06 07 reg [3:0]B;//内部寄存器定义 08 09 always@(posedge clk or negedge rst_n) 10 begin 11 if(!rst_n) 12 begin 13 c<=0; 14 B<=4‘b1111; 15 end 16 else 17 begin 18 c<=&B; 19 end 20 end 21 22 endmodule |

编写测试代码如下

|

/**************************************************** * Engineer : 梦翼师兄 * QQ : 761664056 * The module function:缩减语句测试模块 *****************************************************/ 01 `timescale 1ns/1ps 02 module tb; 03 reg clk; 04 reg rst_n; 05 06 wire c; 07 08 initial 09 begin 10 clk=0; 11 rst_n=0; 12 # 1000.1 rst_n=1; 13 end 14 15 always #10 clk=~clk; 16 17 reduce reduce( 18 .clk(clk), 19 .rst_n(rst_n), 20 .c(c) 21 ); 22 endmodule |

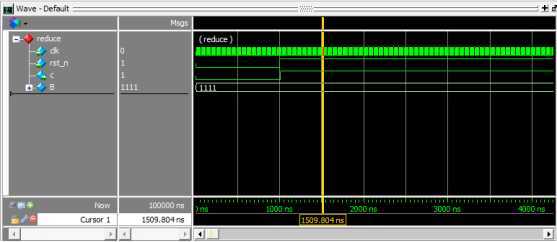

查看仿真波形如下:

通过该波形可以看出,当变量B的四个位全部为高时,由于是“逻辑与”的运算,所以最终输出的变量C为高电平。

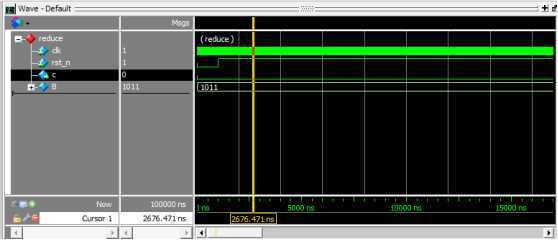

那么如果我们在变量B中加入一个零,结果会如何呢?我们仿真如下:

可以看到,如果变量B中存在零,那么输出结果由于“逻辑与”会得到低电平。

标签:语句 cin 验证 alt 时钟 end sed 如何 top

原文地址:https://www.cnblogs.com/mengyi1989/p/11515976.html