标签:user 流程 ima port support https xls man href

打算使用Cyclone IV的FPGA挂DDR2,按照流程,先使用Quartus跑IP,跑引脚分配,综合OK了再设计硬件,这部分主要是DM和DQS信号比较头疼,研究了好久才找到方法。

在Intel官网查找DDR2 IP的User Guide找到详细的IP描述文件参考链接:

在文档中清楚的告诉你生成的IP有对应的 xxx_example_top.v 测试文件,只需要把改文件添加至工程并设为TOP文件编译就可以做一些测试,具体细节参考文档。

生成IP并添加 XXX_example_top.v 测试文件后,参考Cyclone IV Device Handbook Volume 1 得到 DM和DQS信号如何设计的信息如下所示:

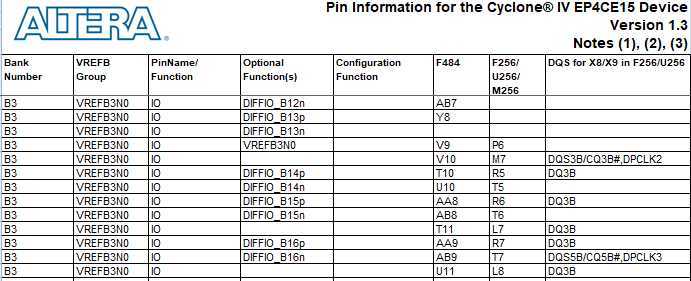

按照该信息找到Cyclone IV的Pin-outs文件, 下载xls文件,我使用的是Cyclone IV E15的,所以下载了E15的xls文件。下载打开后可在Pin List中查看到对应封装的 DDR2 引脚分配信息,

根据自己的情况把IO分配至工程中,编译验证。

完成DQ、DM、DQS信号分配后剩下的是Address信号分配了,参考Handbook得知Address可以使用任意IO,如下图:

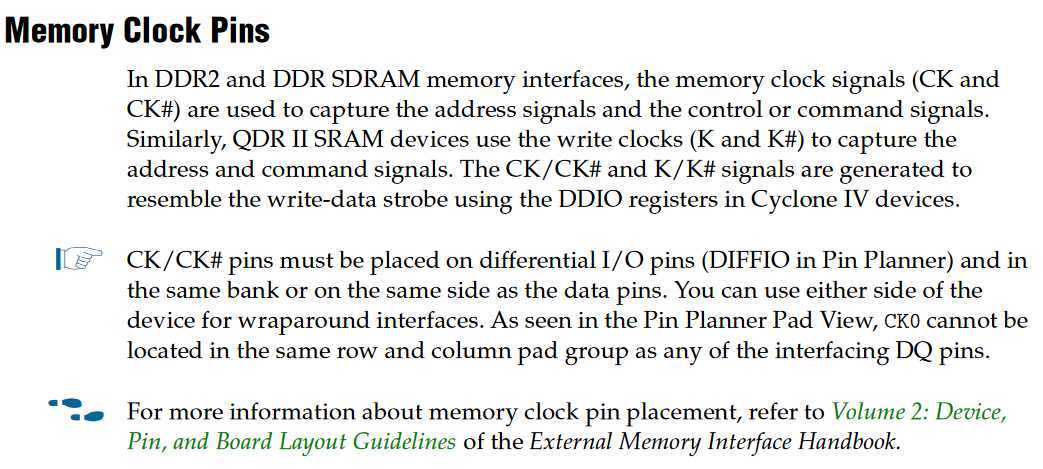

CK信号分配参考如下:

标签:user 流程 ima port support https xls man href

原文地址:https://www.cnblogs.com/DPShadow/p/11520711.html