标签:原因 其他 signed slave res 无效 class 没有 模块

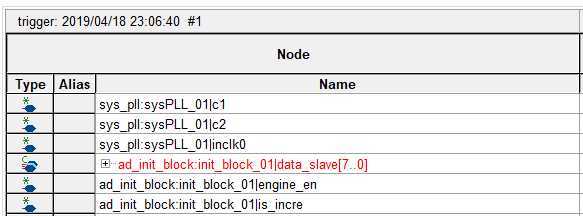

在Quartus SignalTap 工具中加入信号,发现加入的信号变成红色,如图所示的data_slave[7..0]:

这样的信号是没有办法观测的,不会根据SignalTap 的Clock和Trigger进行更新,原因是Synthesis过程将它省略,

添加综合选项(Synthesis Attribute)可以让综合器保留这些对顶层模块输入输出没有帮助的信号,常用的有:

wire[7:0] cnt/*synthesis keep*/; // Keep the Entity of Wire

reg signed[11:0] corr_i_out/*synthesis preserve*/; // Keep the Entity of Register

实际上,对于组合逻辑的输出可以用keep,而时序逻辑块的输出信号常用preserve选项。

同时,红色的无效SignalTap信号会影响SignalTap中其他的信号。这样的空头支票放入SignalTap组件之中,很大概率会影响系统的时序,比如,使得其他待观测的信号全部观察不到了!

在设计调试的时候一定要取消这样的“空头支票”。

SignalTap II Logic Analyzer 无法观测到信号?

标签:原因 其他 signed slave res 无效 class 没有 模块

原文地址:https://www.cnblogs.com/YangGuangPu/p/10733167.html