标签:复位 闪烁 自动 应用 Edito ttl UNC 后缀名 vtt

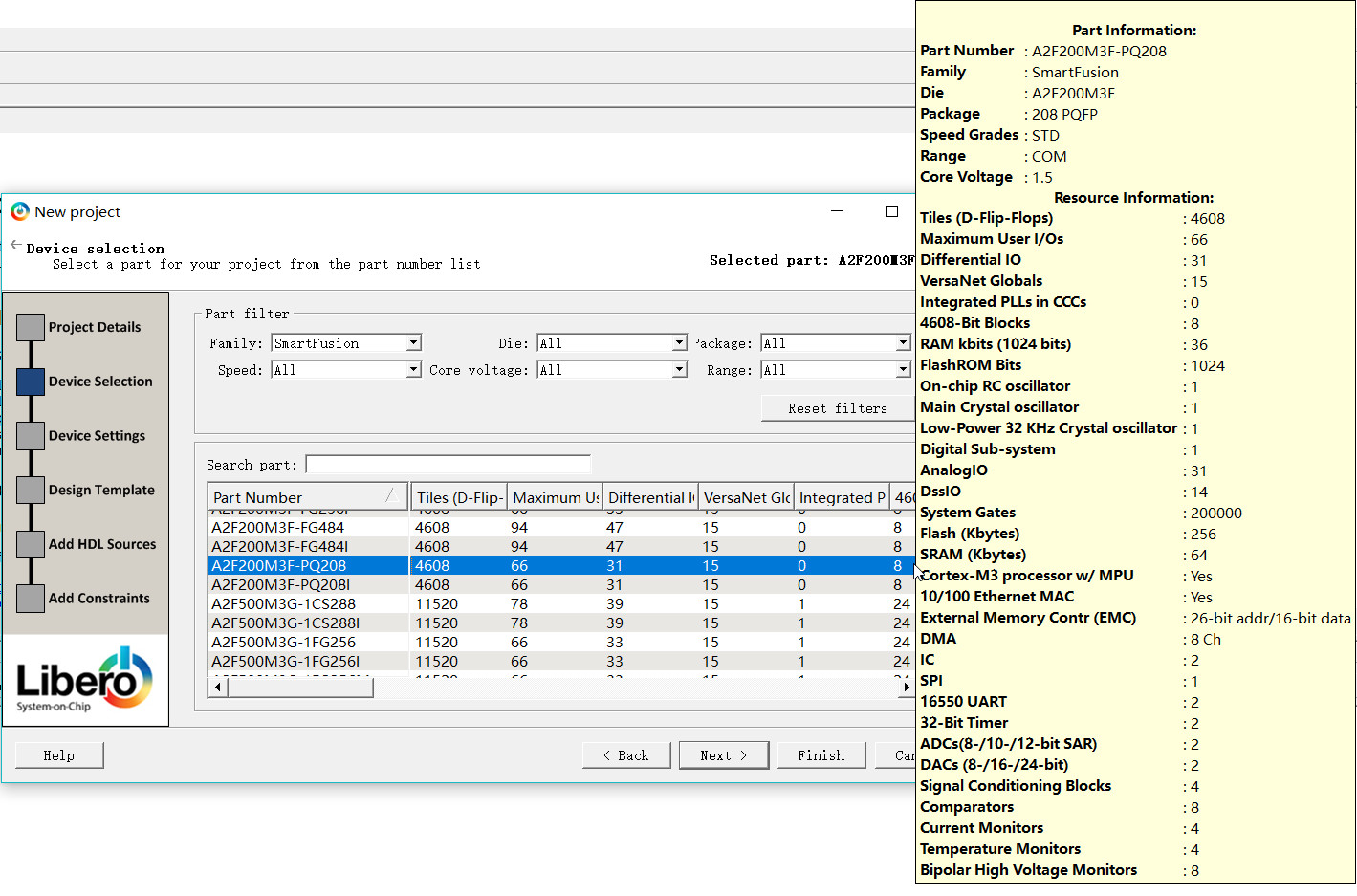

上一篇文章,介绍了Microsemi Libero系列教程(一)-Libero开发环境介绍,下载,安装与注册,作为嵌入式开发中的Hello World,点灯是再也基础不过的实验了,通过点灯实验,可以了解芯片GPIO的控制和开发环境IDE新建工程的流程,对于FPGA来说,每个IO口几乎一样,所以本篇文章主要学习一下如何基于Microsemi Libero集成开发环境建立一个示例工程,让一个LED以500ms的频率闪烁,以Microsemi SmartFusion系列FPGA——A2F200M3F为例,Microsemi其他系列FPGA芯片过程类似。

工欲利其事,必先利其器,充分的准备工作很有必要。

软件准备:

硬件准备:

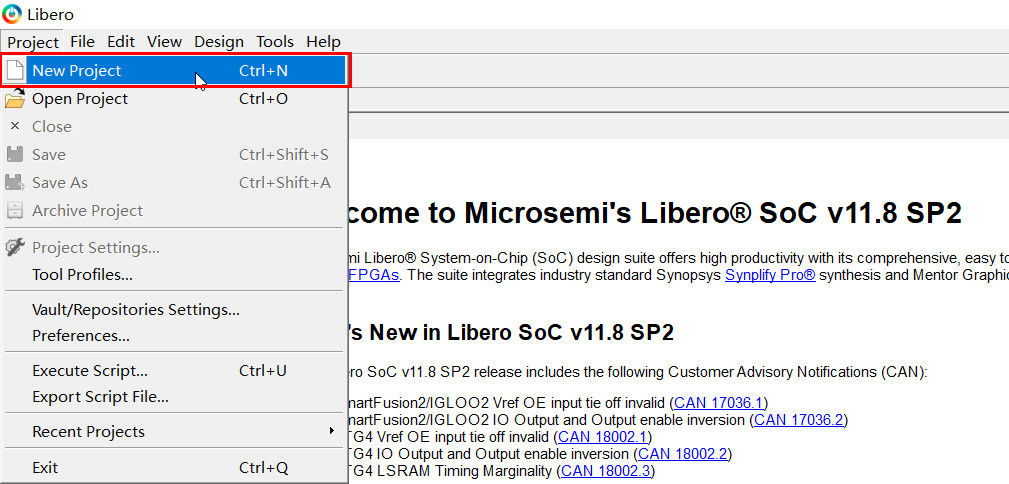

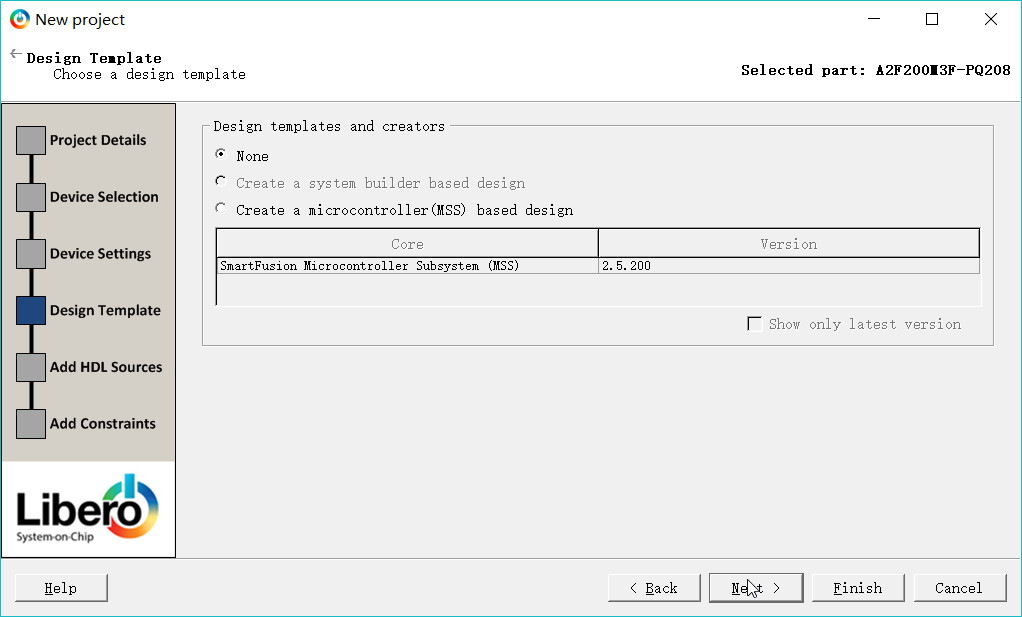

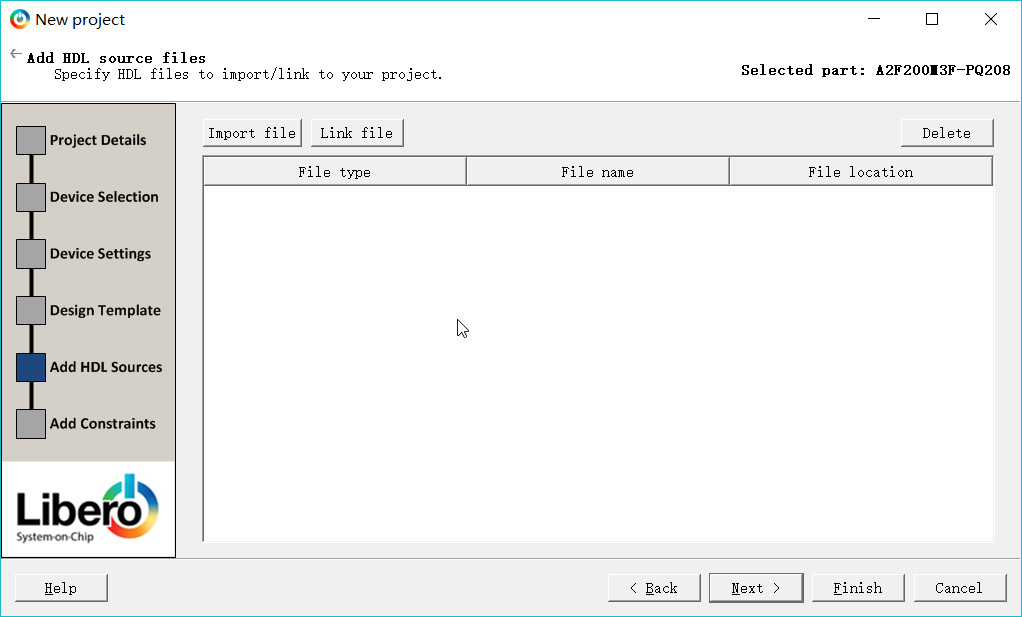

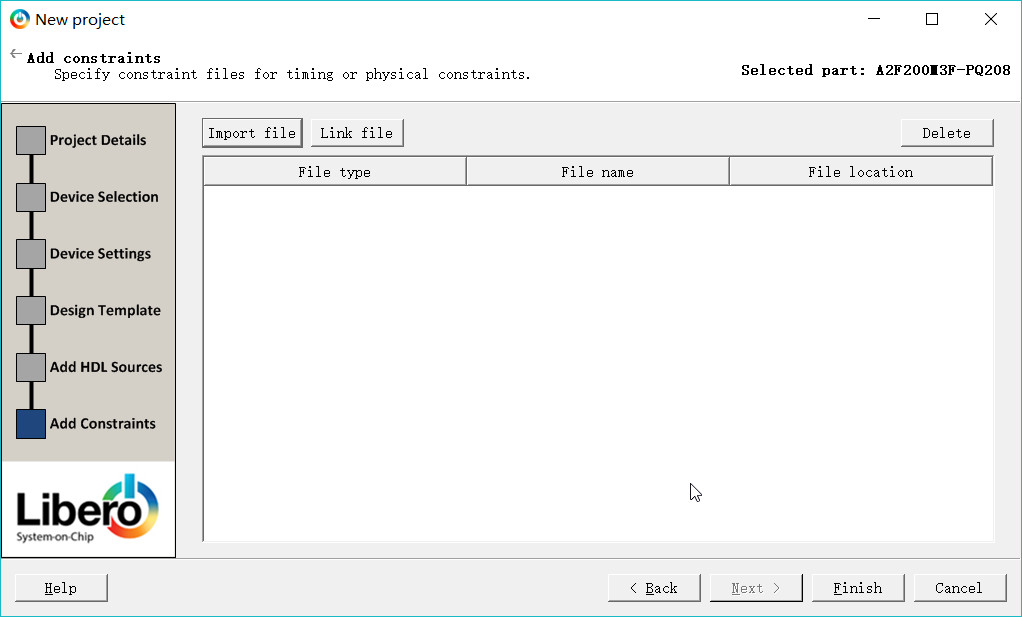

Project -> New Project,新建一个工程。

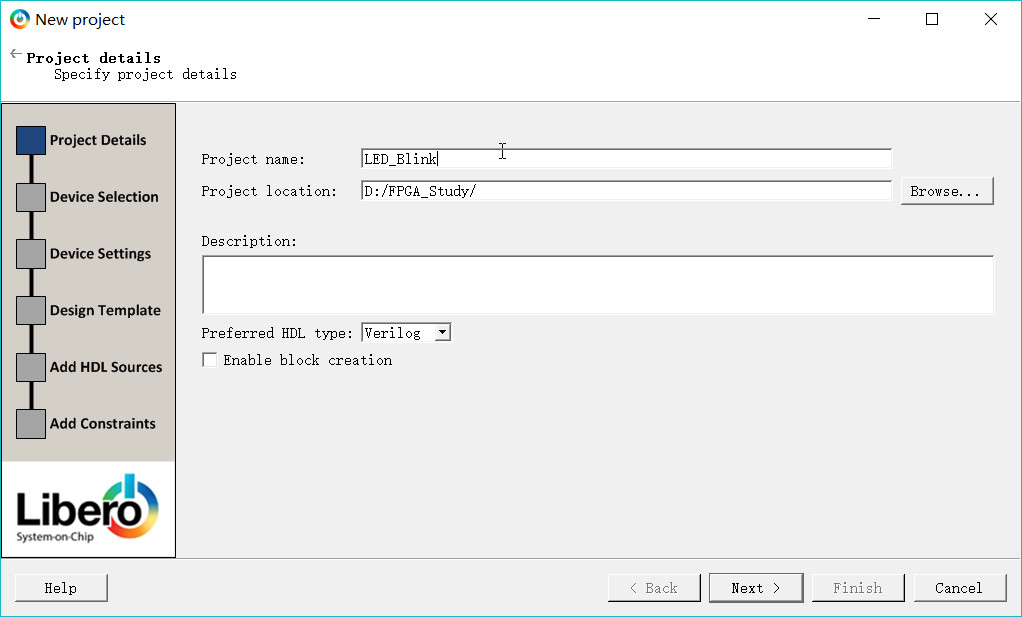

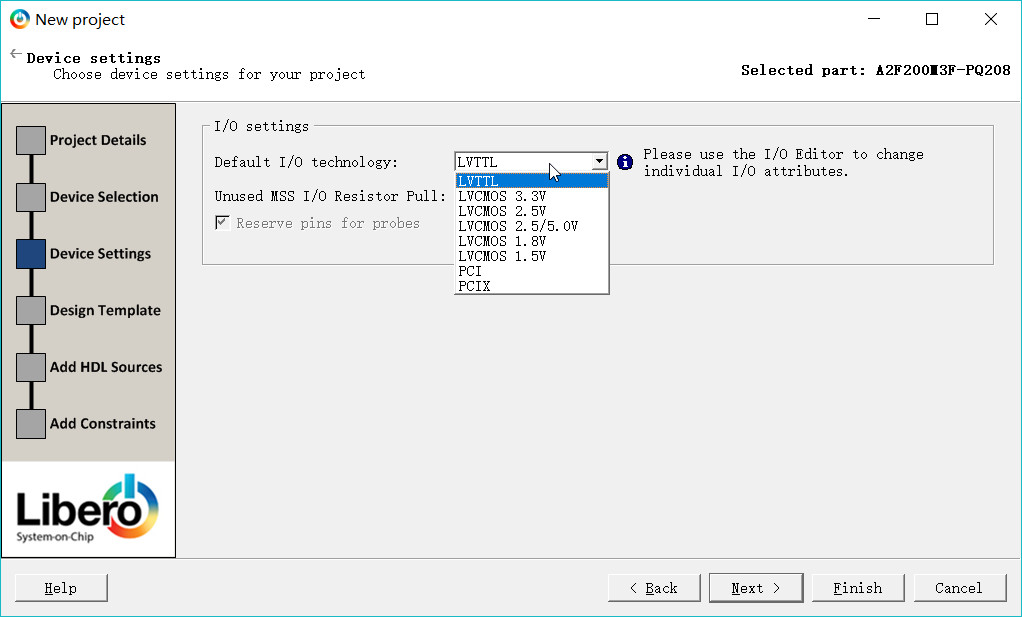

LED_Blink,选择工程存放的路径,工程名称和路径不要有中文字符和空格,选择源文件的类型Verilog或者VHDL。

到这里,工程就创建完成了,然后会在存储路径下生成一个和工程名称一样的文件夹,工程相关的所以文件都存放在这里。主要包括以下几个文件夹:

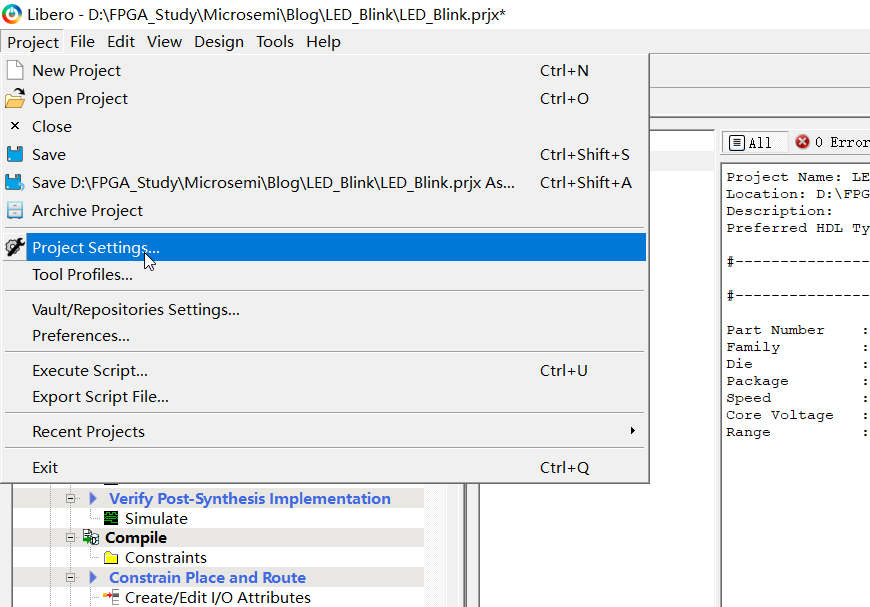

具体每个文件夹存放的是什么文件,我们在以后的文章再详细介绍。以上的工程配置在创建完工程之后,也可以再次更改,可以通过Project->Project Setting查看或更改配置:

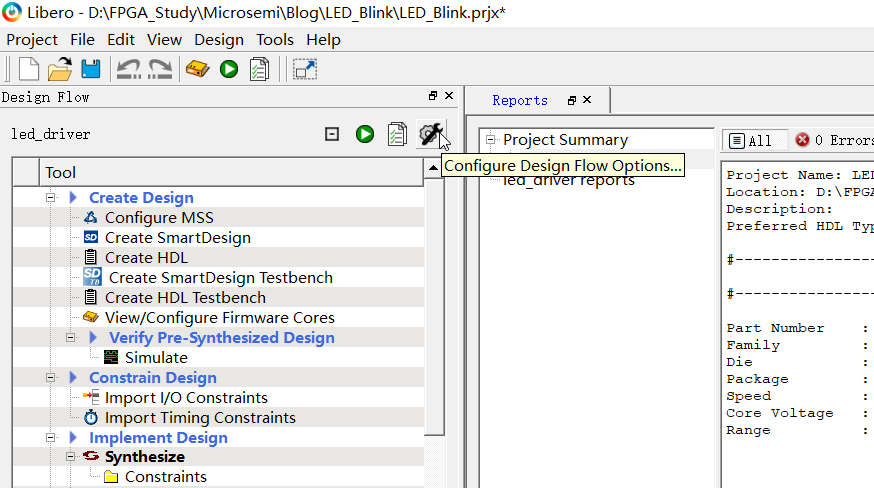

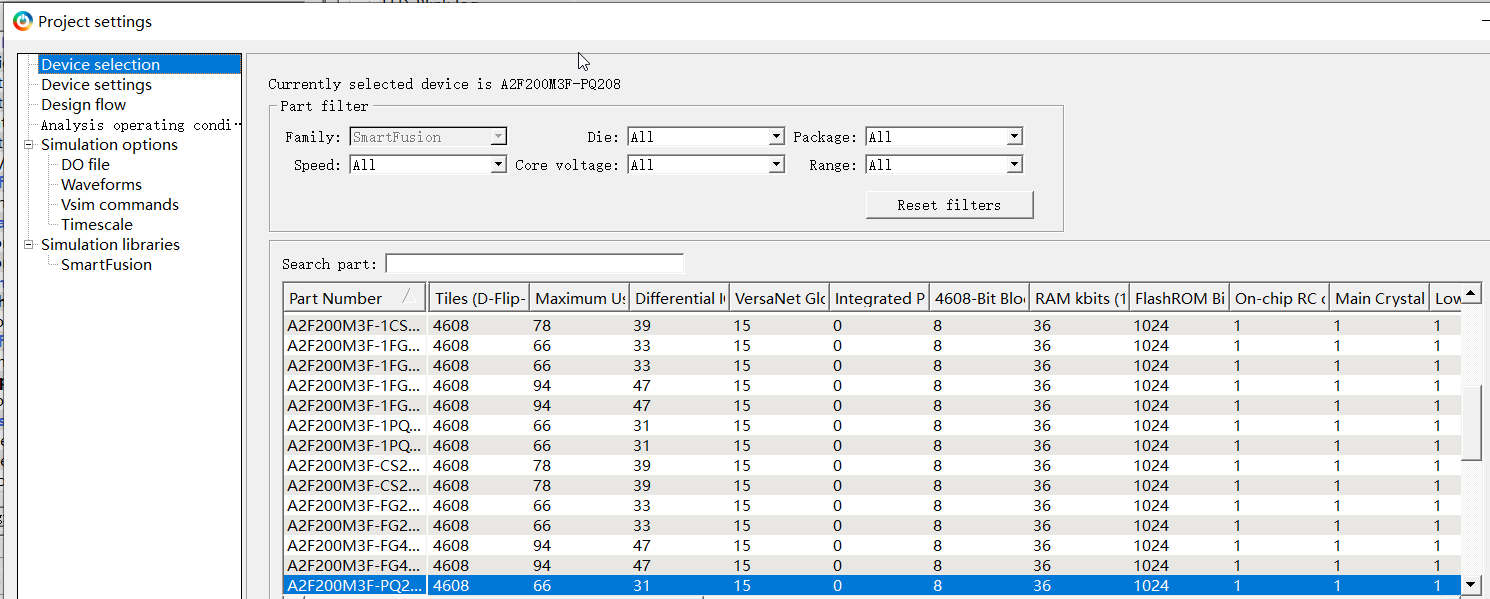

或者通过点击如下图标来进入配置界面:

弹出如下窗口,和新建工程是一样的,可以更改FPGA的型号,但只限于同一个系列内。

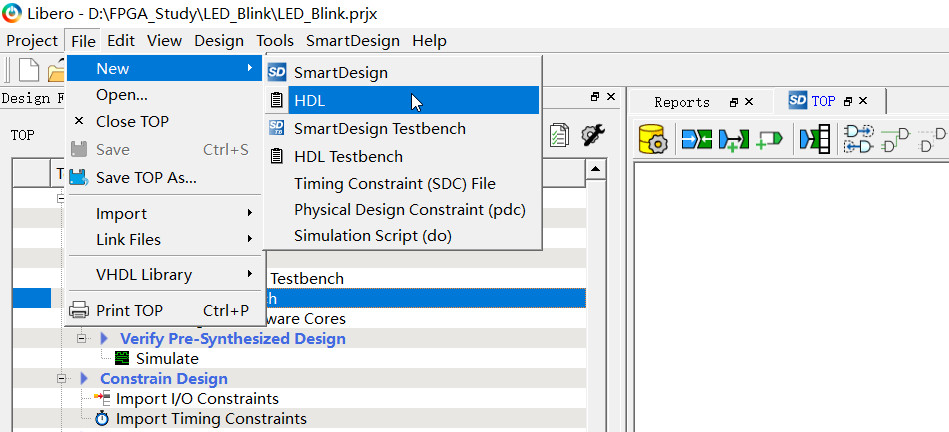

Microsemi Libero开发环境支持HDL方式和SmarDesign方式来创建设计,HDL方式支持VerilogHDL和VHDL两种硬件描述语言,而SmartDesign方式和Xilinx的Schematic原理图方式是一样的,是通过图形化的方式来对各个模块之间的连接方式进行编辑,两种方式都可以完成设计。由于本实验功能简单,所以以使用Verilog文件为例。

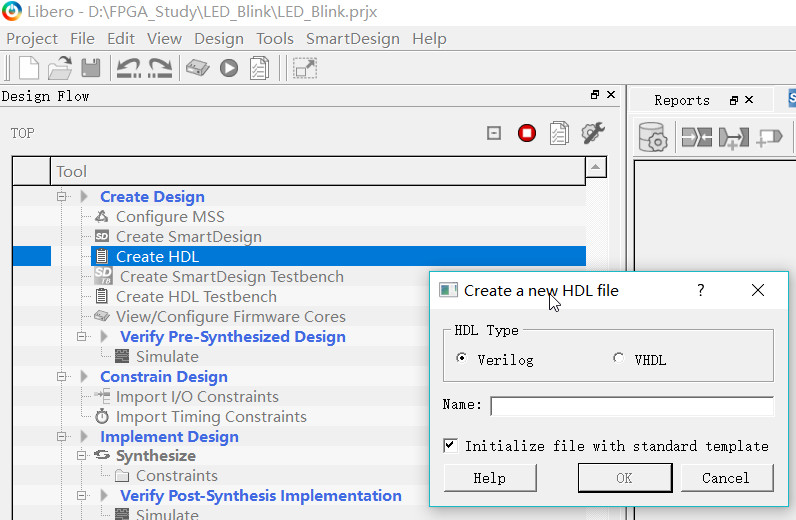

创建Verilog文件有多种方式,可以直接双击左侧菜单中的Create Design->Create HDL

或者点击File->New->HDL,这两种方式都可以创建一个Verilog设计文件,这里选择Verilog文件。

输入模块名称:led_driver,不用添加.v后缀名,Libero软件会自动添加。

源代码:

module led_driver(

//input

input clk, //clk=2MHz

input rst_n, //0=reset

//output

output reg led

);

parameter T_500MS = 999999; //1M

reg [31:0] cnt;

always @ (posedge clk)

begin

if(!rst_n)

cnt <= 32'b0;

else if(cnt >= T_500MS)

cnt <= 32'b0;

else //cnt < T_500MS

cnt <= cnt + 32'b1;

end

always @ (posedge clk)

begin

if(!rst_n)

led <= 1'b1;

else if(cnt >= T_500MS)

led <= ~led;

end

endmodule可以看到,代码非常的简单,定义一个计数器,系统时钟为2MHz=500ns,500ms=1M个时钟周期,当计数到500ms时,LED翻转闪烁。

编写完成,之后,点击对号进行语法检查,如果没有语法错误就可以进行时序仿真了。

底部切换到Design Hierarchy选项卡,在led模块上右键选择Create Testbechch创建仿真文件,选择HDL格式。

给创建的testbench文件名一般为模块名后加_tb,这里为:led_driver_tb,因为我们的板子外部晶体为2M,所以这里系统时钟周期为500ns,这个也可以在文件中更改。

点击OK之后,可以看到,Libero软件已经为我们生成了一些基本代码,包括输入端口的定义,系统时钟的产生,输入信号的初始化等等。我们只需要再增加几行即可。

`timescale 1ns/100ps

module led_driver_tb;

parameter SYSCLK_PERIOD = 500;// 2MHZ

reg SYSCLK;

reg NSYSRESET;

wire led; //add output reg

initial

begin

SYSCLK = 1'b0;

NSYSRESET = 1'b0;

end

initial

begin

#(SYSCLK_PERIOD * 10 )

NSYSRESET = 1'b0; //add system reset

#(SYSCLK_PERIOD * 100 )

NSYSRESET = 1'b1; //add system set

end

always @(SYSCLK) //generate system clock

#(SYSCLK_PERIOD / 2.0) SYSCLK <= !SYSCLK;

led_driver led_driver_0 (

// Inputs

.clk(SYSCLK),

.rst_n(NSYSRESET),

// Outputs

.led(led ) //add port

// Inouts

);

endmodule仿真代码也非常简单,输入信号初始化,NSYSRESET在10个时钟周期之后拉低,100个时钟周期之后拉高。

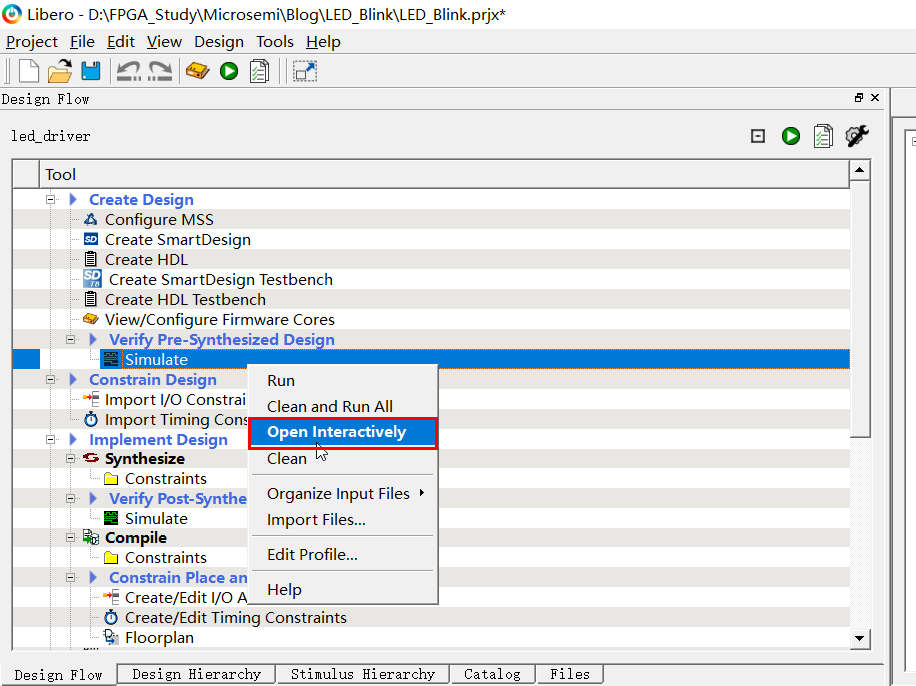

仿真代码语法检查无误后,可以进行ModelSim自动仿真,在安装Libero时,已经默认安装了ModelSim仿真软件,并和Libero进行了关联。直接双击Simulate,Libero会自动打开ModelSim。

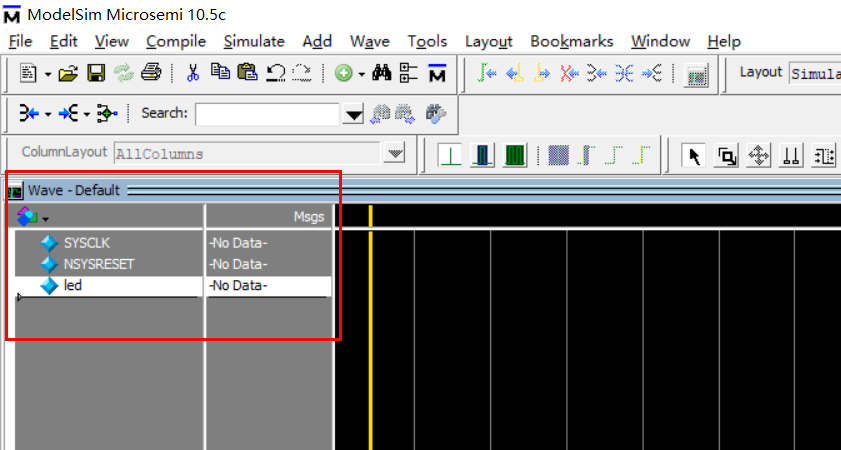

可以看到输入输出信号,已经为我们添加好了:

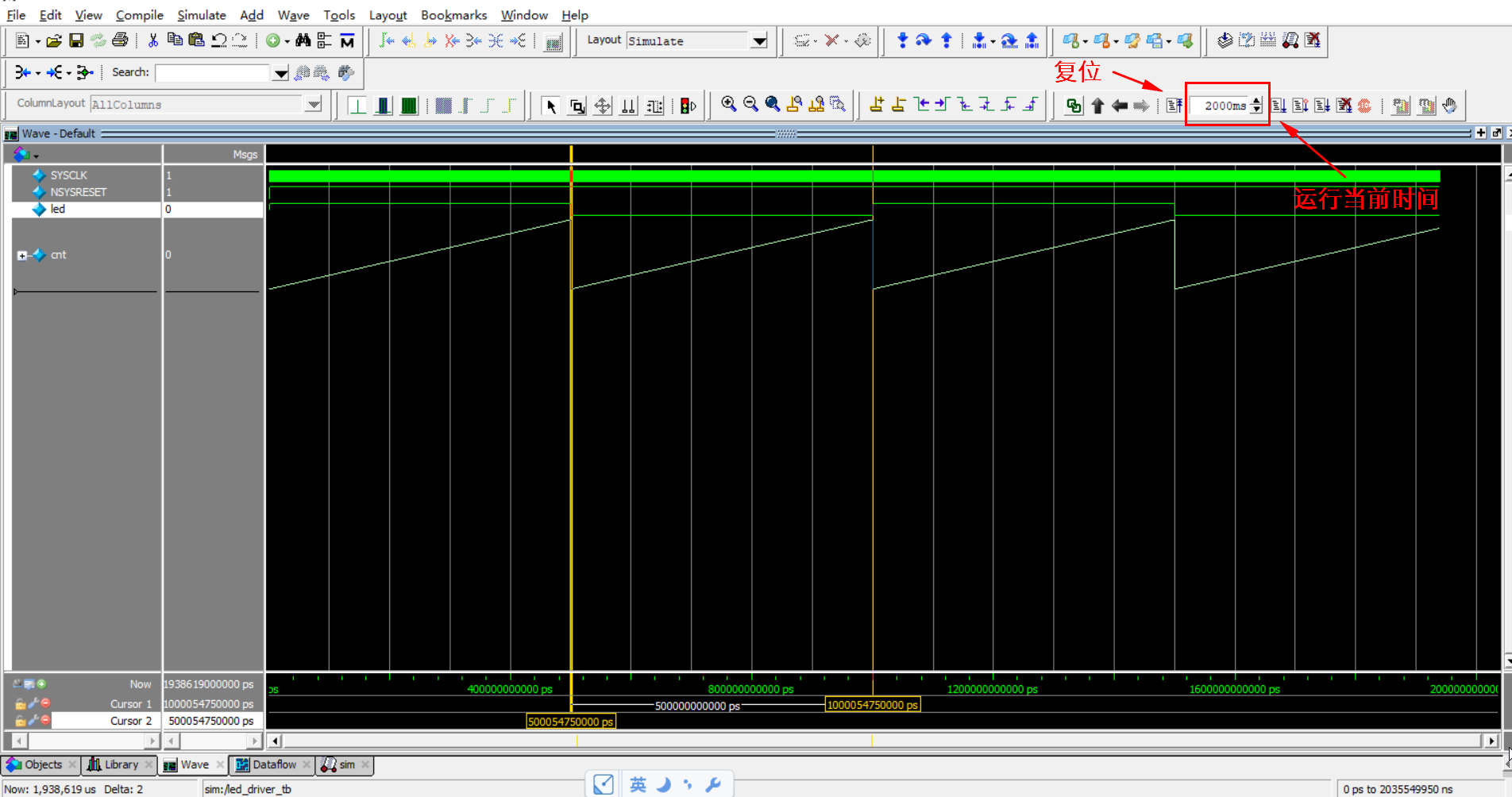

先点击复位按钮,复位系统,然后设置要运行的时间,由于设计的是500ms闪烁一次,这里我们先运行2s,即2000ms,在ModelSim中2秒已经算是很长的时间了,然后点击时间右边的运行按钮,耐心等待,停止之后就会看到led按500ms变化一次的波形了,如下图所示,可以再添加一个cnt信号到波形观察窗口,可以看到cnt周期性的变化。

使用2个光标的精确测量,可以看出,led每隔500ms翻转一次,说明程序功能是正确的。

与STM32等MCU不同,FPGA的引脚配置非常灵活,如STM32只有固定的几个引脚才能作为定时器PWM输出,而FPGA通过管脚分配可以设置任意一个IO口输出PWM,而且使用起来非常灵活,这也是FPGA和MCU的一个区别,当然其他的功能,如串口外设,SPI外设等等,都可以根据需要自己用HDL代码来实现,非常方便。

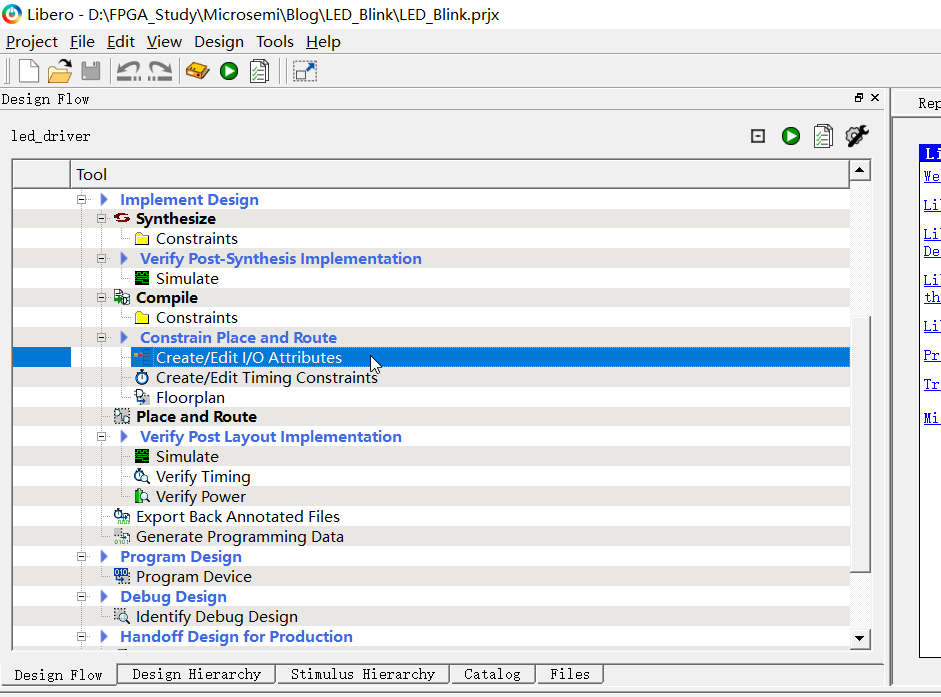

时序仿真正常之后,就可以进行管脚分配了,即把模块的输入输出端口,真正的分配到芯片实际的引脚上,毕竟我们的代码是要运行在真正的芯片上的。

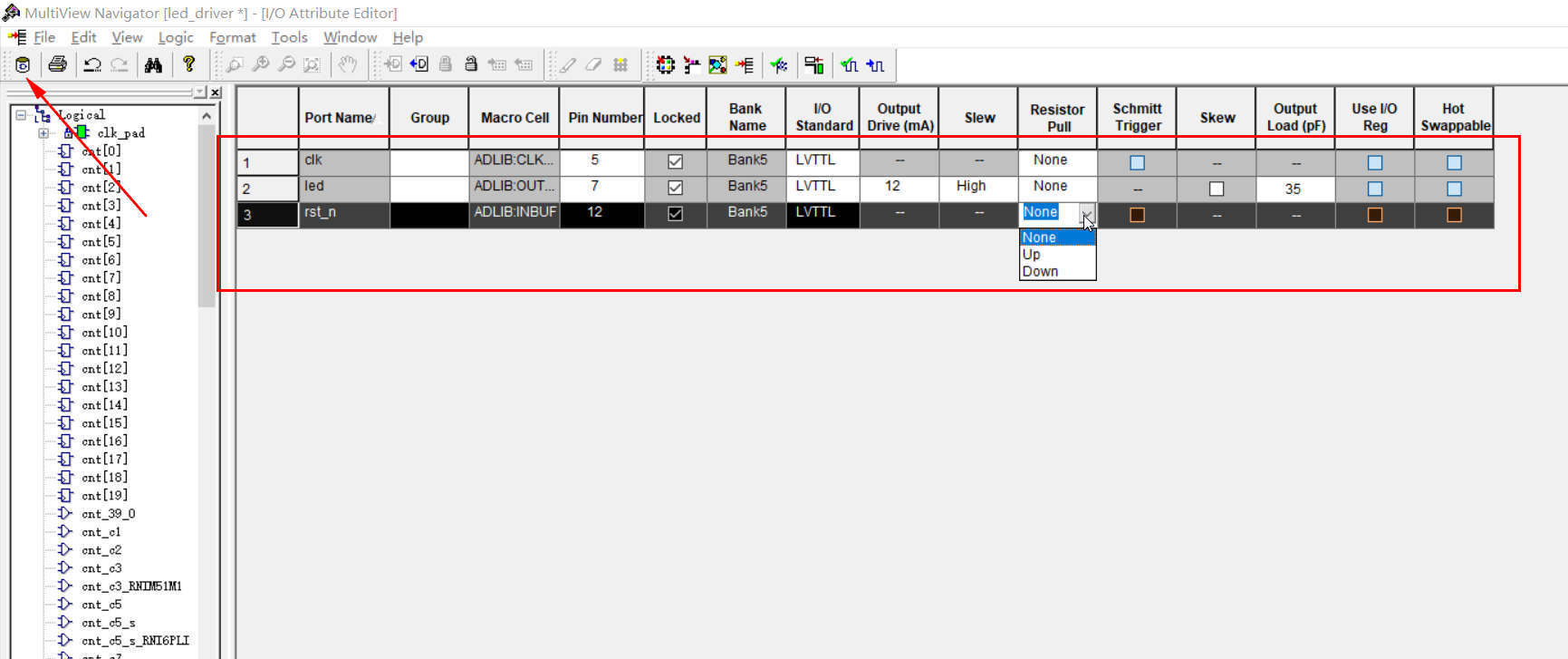

双击Create/Edit I/O Attributes,打开图形化配置界面,在打开之前,Libero会先进行综合(Synthesize)、编译(Complie),当都运行通过时,才会打开配置界面。

管脚可视化配置工具使用起来非常简单:引脚号指定、IO的电平标准,内部上下拉等等,非常直观。把时钟、复位、LED这些管脚分配到开发板原理图中对应的引脚,在分配完成之后,可以点击左上角的commit and check进行检查。

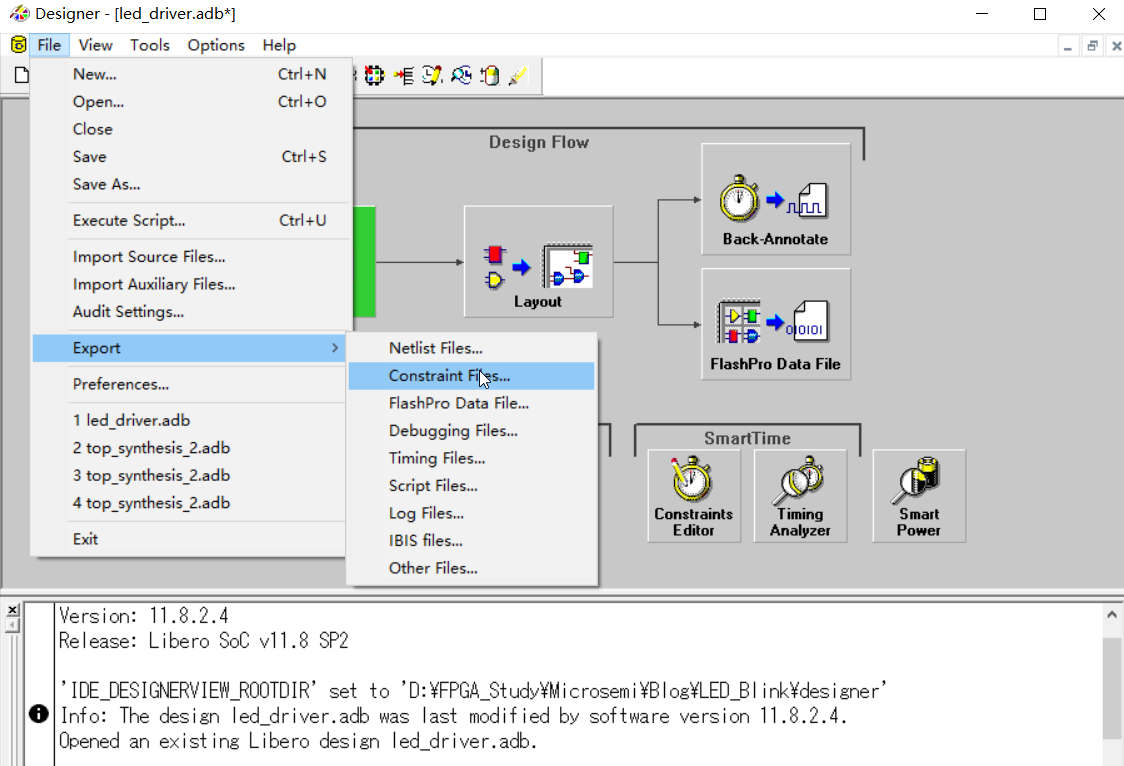

在分配完成之后,为了以后方便查看已经分配的引脚,可以导出一个pdc引脚约束文件,选择Designer窗口下的File->Export->Constraint File,会导出一个led_driver.pdc文件,保存在工程目录下的constraint文件夹。

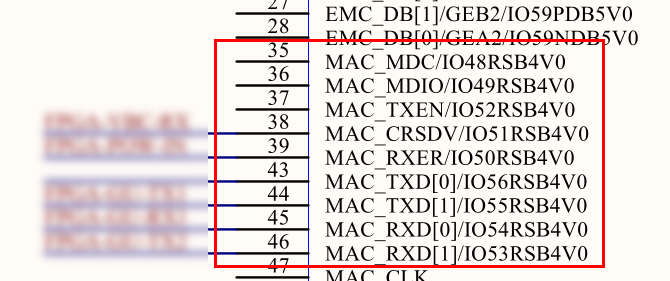

SmartFusion系列的FPGA芯片,在分配个别引脚,如35-39、43-47这些引脚时,直接不能分配,这些引脚属于MSS_FIO特殊引脚,具体怎么配置为通用IO,可以查看下一篇文章。而新一代的SmartFusion 2系列的FPGA芯片则没有这种情况。

管脚分配完成之后,连接FlashPro下载器和开发板的JTAG接口,关闭Designer窗口,选择Program Device,耐心等待几分钟,如果连接正常,会在右侧输出编程信息:擦除、验证、编程等操作,下载完成之后,就会看到板子上的LED闪烁起来了。

和Altera、Xilinx不同,Microsemi FPGA在下载程序时,并不是下载程序到SPI Flash,而是直接下载到FPGA内部的。目前,FPGA 市场占有率最高的两大公司Xilinx和Altera 生产的 FPGA 都是基于 SRAM 工艺的,需要在使用时外接一个片外存储器以保存程序。上电时,FPGA 将外部存储器中的数据读入片内 RAM,完成配置后,进入工作状态;掉电后 FPGA 恢复为白片,内部逻辑消失。这样 FPGA 不仅能反复使用,还无需专门的 FPGA编程器,只需通用的 EPROM、PROM 编程器即可。而Microsemi的SmartFusion、SmartFusion2、ProASICS3、ProASIC3E系列基于Flash结构,具备反复擦写和掉电后内容非易失性, 因此基于Flash结构的FPGA同时具备了SRAM结构的灵活性和反熔丝结构的可靠性,这种技术是最近几年发展起来的新型FPGA实现工艺,目前实现的成本还偏高,没有得到大规模的应用。

欢迎大家关注我的个人博客:www.wangchaochao.top

或微信扫码关注我的公众号

Microsemi Libero系列教程(二)——新建点灯工程

标签:复位 闪烁 自动 应用 Edito ttl UNC 后缀名 vtt

原文地址:https://www.cnblogs.com/whik/p/11609965.html