标签:枚举 架构 寄存器 mic set idt sea res pcie

对新手来说,第一步了解PCIE的相关基本概念,第二步了解PCIE配置空间,第三步深入研究PCIE设备枚举方式。本章主要总结第二步的PCIE配置空间

按照国际惯例,先提问题:

1. 什么是PCIE的配置空间?

2. PCIE设备的配置空间有多大? PCI和PCIE的配置空间有何区别与联系?

3. 如何访问PCIE设备的配置空间?

4. 有几种类型,都包含什么内容?

带着上述问题,来进行该部分的总结:

什么是PCIE的配置空间?

每个PCIE设备都有自己的独立的一段配置空间,该部分空间是这个设备的(可能是一段e2prom),系统会给这个设备分配一段内存空间,CPU访问这段内存空间即访问对此设备的配置空间。设备在出厂时,配置空间是有默认初始值的。

PCIE设备的配置空间有多大? PCI和PCIE的配置空间有何区别联系?

早期的PCI时期,系统为每个PCI设备分配的内存大小仅有256个Bytes。到后来的PCIE时期,随着设备性能增强,PCIE设备的配置空间扩展至4K个Bytes。在这里需要注意:

PCIE一共支持256条Bus,32个Dev,8个Fun。因此在满负载的情况下,共需内存大小 = 4k * 256 *32*8 = 256K Bytes = 256M 这个256M的内存空间是为PCIE设备准备的空间系统不可用,这也是你的内存条,实际给你用的总是会小于标称的主要原因之一。

PCIE设备发展向前兼容PCI,每个设备的配置空间的前256个Byte是PCI访问空间,后4k-256个Byte的空间是PCIE扩展空间。这是二者的主要区别,另外一个区别就要引出下面的一个问题

PCI/PCIE设备配置空间的访问方式----IO访问 内存访问

X86系统中,对PCIE设备配置空间的地址映射一般有两种方式:内存映射和IO映射。因此开发者也可以通过内存访问或者IO访问来访问其配置空间

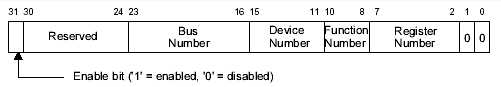

PCIE设备的访问离不开其Bus,Dev,Fun的编号方式,如下图寄存器所示,Bit[23:16]用来存放Bus号,共8Bit,因此解释了上述表述为何一共有256条Bus,Bit[15:11]存放Dev,共5bit可存32个Dev,Bit[10:8]存放Bus,共3Bit可存8个Fun。

无论是采用IO还是内存的方式来访问配置空间,都离不开上面的图,下面具体介绍:

1. IO访问

IO应该是Intel X86架构的独有产物了,简单可理解为一段存储空间,用户通过IN/OUT指令来访问(内存的话,需要用MOVE指令来进行访问),部分设备可以映射到IO空间中,开发者通过IO端口访问这个设备,比如现在介绍的这个:CF8 / CFC。Intel可以通过这组端口来对PCIE的前256个Byte进行访问,一个指定地址,一个指定数据。代码如下:

1 /*Writer date to cf8*/

2 Address = BIT31|((BUS & 0XFF)<< 16)|((DEV & 0x1F)<<11)|((Fun & 0x7) << 8);

3 IoWrite32(0xCF8, address); //将要读取的地址写入到CF8

4 Date32 = IoRead32(0xcfc); //从CFC端口读出address的数据

注: IO访问仅能读取到前256个Byte,256Byte后的空间需要用内存访问

2. 内存访问

这个其实与IO访问大同小异,配置空间全部映射到内存中,用户在确定设备地址后,即可通过内存读写的方式进行访问,如下代码:

1 /*Write date*/ 2 MmioWrite32(PcieBaseAdd + Bus<<16 + Dev<<11 + Fun<<8 + offset, date); //PcieBaseAdd为PCIE在内存中的基地址 3 4 /*Read date*/ 5 Value = MmioRead32(PcieBaseAdd + Bus<<16 + Dev<<11 + Fun<<8 + offset);

PCIE配置空间集中类型,都包含什么内容

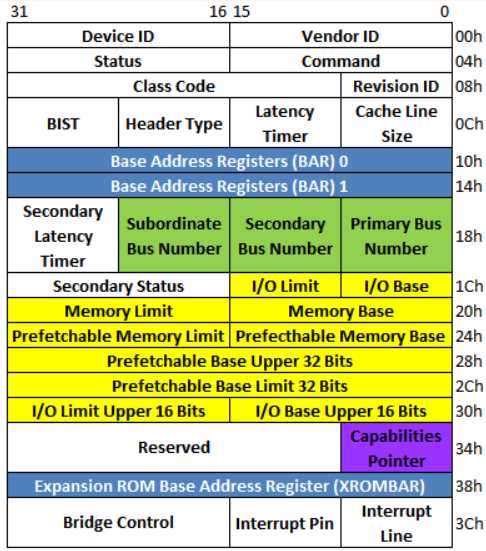

配置空间主要有两种,开发者也是搞清楚这两种即可,一是Type0:设备空间 二是Type1: Bridge空间

设备空间如上图所示:下面介绍其中主要内容以及作用:

DID&VID: 设备及厂商ID,出场固定且每个设备都不应,枚举设备时通常判断此ID来判断设备是否存在。

Class Code:

HeaderType:

BAR0 & BAR1: 设备空间的基地址

Subordinate Bus Number: 从属Bus号即该Bus这颗树下最大的Bus号。

Secondary Bus Number: 该Bridge下接的Bus号

Primary Bus Number: 该Bridge上接的Bus号

Memory Limit: 此设备所分配的内存大小?

Memroy Base: 此设备在内从中分配的基地址?

标签:枚举 架构 寄存器 mic set idt sea res pcie

原文地址:https://www.cnblogs.com/szhb-5251/p/11620019.html