标签:device 安装 序号 package splay ips 元器件 http text

一:焊盘篇

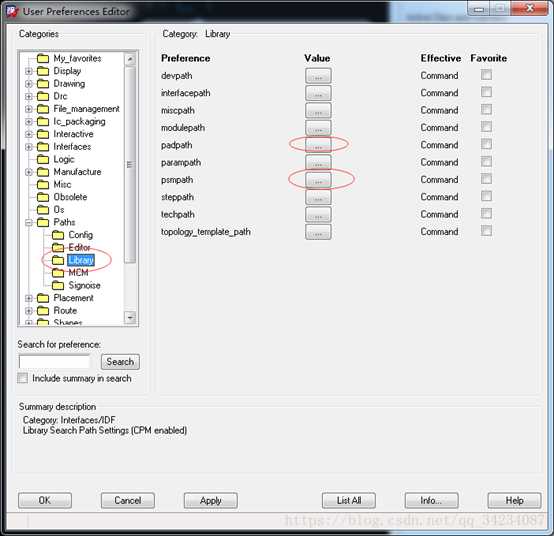

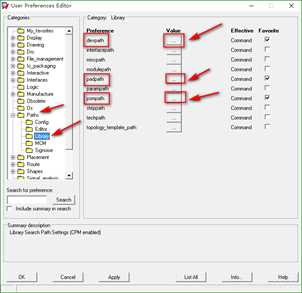

解决办法:在Pcb editor中选择set→user preference→paths→Library→分别在padpath和psmpath中加入焊盘的路径(选中所对应的上层文件夹即可)

二:网表导入篇(Cadence中生成netlist失败的原因)

错误原因:allegro.cfg文件找不到或allegro.cfg文件不能打开,这个问题的根源是,有可能每台电脑上安装Allegro的位置不一样,allegro.cfg文件找不到是理所当然的。

解决办法:点生成netlist,点setup,修改路径为capture\allegro.cfa所在路径,把allegro.cfg文件的位置选择你现在安装目录的文件位置。(示例:D:\Cadence\SPB_16.5\tools\capture\allegro.cfg)

2.问题二:#1 ERROR(ORCAP-36055):Illegal character in \hi-am13-mb-v.ooo(a10)

#2 ERROR(ORCAP-36055):Illegal character in \hi-am13-mb-v.ooo(a10)\

#3 ERROR(ORCAP-36055):Illegal character in \hi-am13-mb-v.ooo(a10)\

…….

错误原因:首先确认了是非法字符,ORCAD包含的非法字符有:”/”、”<”、”>”、”#”、”$”、”(”、”)”。

解决办法:懒得写,自己上网查。提醒自己以后在使用ORCAD和ALLEGRO时不要使用中文路径、且文件名和路径名中均不能有非法字符,否则将无法导出网表。

3.问题三:netlister failed.please refer to session log or netlist.log for details.

错误原因:检查或者重新排列(Annotate)元器件的标号,防止出现多个元器件重复命名;检查每个元器件是否有拥有自己的封装,封装名是否正确,名称要保持完全一致。(Tips:这只是其中几个小原因,更多的原因需探索)

解决办法:挨个试…(这种原因最可怕,没有具体提醒)

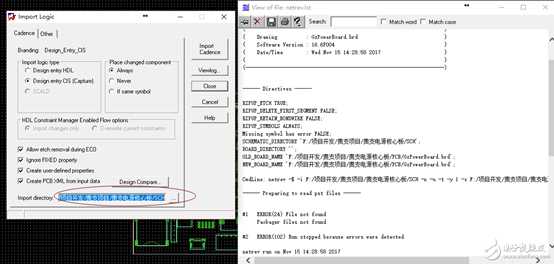

4.问题四:#ERROR(24)File not found

Packager files not found

错误原因:导入网络表的路径没有设置正确,选择网表路径时,要双击打开网表所在文件夹,再点击OK。如果不双击打开网表文件夹,cadence导入的路径为上一级文件路径。

解决办法:选择路径时直到进入网络表文件夹里。(同一原理图的pcb文件和网表放在一个文件夹下)

5.问题五:Name is too long

错误原因:名称尺寸设置太小。

解决办法:改大

6.问题六:Symbol ‘CS2-100-70X60‘ for device ‘CAP NP_CS2-100-70X60_1000PF‘ not found in PSMPATH or must be "dbdoctor"ed.

错误原因:此类错误和没有PCB封装有关。

解决办法:在pcb中打开setup→User preferences→paths→Library→对preference项进行添加→根据consen公司的共享库,找到lib-pcb文件夹→打开关于PCB封装库的配置说明文件.docx→根据操作步骤进行添加即可 。

三:Allegro PCB篇

错误原因:原来软件默认原点在(0,0),所以画到负数那边属于区域外就不能画了,必须设置原点到新的位置,如下图。

解决办法:Setup→Design parameter Editor→Design→在Move origin位置将坐标改为(10000,8000),上面的Extent坐标会对应发生变化(-10000,-8000),此时即可画图。

2.问题三:Allegro 在使用过程中options不小心被关掉了怎么重新调出来?

解决办法:View→windows→在前面选中即可。

3.问题四:Allegro如何将十字设置成大光标?

解决办法:Set→User preferences→Display→Cursor→若pcb_cursor复选框中是cross,则是小十字光标,若是infinite则为大光标。

4.问题五:如何将Allegro中的元器件锁定不再移动?(在画PCB的时候,有一些关键元器件无需再移动,为了防止其移动,可以将这个元器件固定。)

解决办法:在pcb下面的command命令栏输入控制命令:fix锁定元器件;unfix解锁元器件。方法二:也可以点击图中两个符号,左边的为锁定,右边的为解锁。

5.问题六:在Allegro中布局时,如何快速通过选择原理图中的元器件直接进行布局?

解决办法:在原理图的Options下面选择preferences会出来一个对话框,对话框里选择Miscellaneous,找到Intertool Communication选项,选中Enable Intertool Communication(允许原理图和ALLEGRO交互)选项,就可以了。

6.问题七: Allegro如何修改封装中焊盘的引脚编号?

解决办法:打开dra文件→find→仅选中text在前面打勾→点击焊盘上的序号编码→找到Edit→点击Text→弹出Text Edit框→在Enter new text中输入新的编码即可。

标签:device 安装 序号 package splay ips 元器件 http text

原文地址:https://www.cnblogs.com/shendanblogs/p/11631238.html