标签:控制器 因此 处理器 函数 表示 屏蔽 stm32 匹配 运行

学习目标:

1、了解nor flash存储芯片的概念和特性

2、掌握使用s3c2440芯片对外挂的nor flash进行读写擦除操作

1、NOR Flash的简单介绍

NOR Flash最早是由Intel公司于1988年开发出的,是现在市场上两种主要的非易失性存储器之一,它的出现彻底改变了存储器市场上由EPROM(Erasable Programmable Read-Only-Memory电可编程序只读存储器)和EEPROM(电可擦只读存储器Electrically Erasable Programmable Read - Only Memory)一统天下的局面。NOR Flash最大特点是支持XIP(Execute On Chip),既程序可以直接在NOR flash的片内执行,在NOR Flash中的代码运行时不需要重定位复制到RAM内。NOR Flash的地址线和数据线分开,数据的读取和RAM很类似,只要能够提供数据地址,数据总线就能正确给出数据。不过不能直接对它进行写操作,执行写操作之前需要先发送固定的命令序列,然后发送写操作的地址和数据。

NOR Flash存储器的最小访问单元一般分为8位和16位的,也有一些NOR Flash器件同时支持8位和16位模式,这种Flash的位宽可以在设计硬件时选择,当芯片的BYTE#引脚接为高电平,芯片工作在位宽16位模式,BYTE#引脚设为低电平时,芯片工作在位宽8位模式。

NOR Flash一般有多个扇区,扇区是NOR Flash擦除的最小单位,Nor Flash中每个扇区的大小也不是固定的,扇区的排放一般分为两种模式Top Boot part 和Bottom Boot part 。这两种形式的区别是小块的扇区在NOR Flash芯片中放置的位置不同,Bottom Boot类型的NOR Flash小块地址位于芯片0地址,而Top Boot part类型的NOR Flash小块地址位于芯片的高地址上。

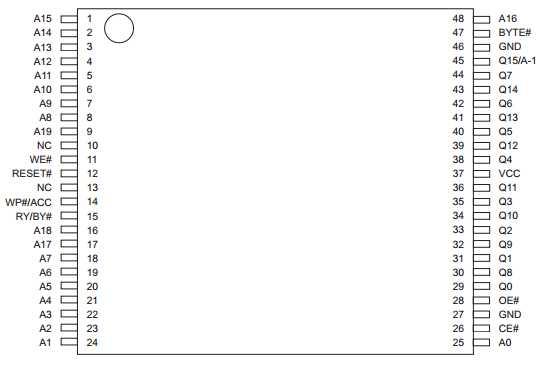

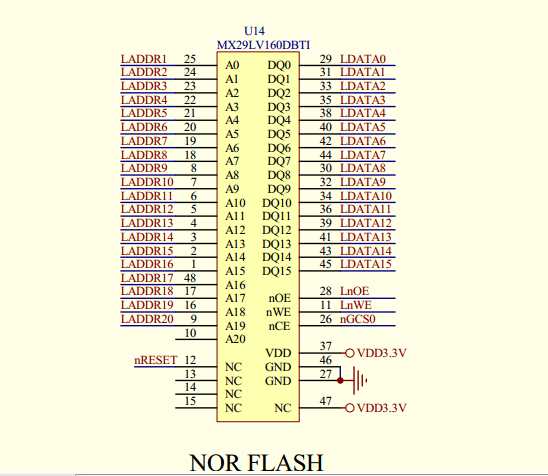

2、NOR Flash引脚介绍(以MX29LV60DBTI芯片为例)

MX29LV60DBTI是16M-BIT的NOR Flash芯片,它的引脚如下图所示:

引脚描述表

| 符号 | 管脚名 | 功能 |

| A0~A19 | 地址输入 | 地址信号,表示要读写数据的地址信息 |

| Q0~Q15 | 数据输入/输出 | 数据输入/输出引脚,读周期内输出数据,写周期内输入数据 |

| CE# | 芯片使能 | CE#为低电平时,芯片被选中,后续执行的操作才会有效 |

| WE# | 写使能 | 配合CE#和OE#以及地址引脚和数据引脚一起使用,当CE#低电平,OE#高电平,WE#为低电平时,Q0~Q15上数据被写入到A0~A19表示地址中 |

| BYTE# | 字或字节选择输入 | 当其为高电平时,数据输出为16bit模式;低电平时,数据输出为8bit模式 |

| RESET# | 硬件复位/扇区保护解锁引脚 | 硬件复位引脚,当输入信号为低电平时,芯片复位 |

| OE# | 输出使能 | 配合CE#和WE#以及地址引脚和数据引脚一起使用,当CE#低电平,WE#高电平,OE#为低电平时,将地址A0~A19内存中的数据传送到Q0~A15上 |

| RY/BY# | RY/BY#输出引脚 | 用于输出Ready和Busy信号,实际用时可以不接,可以用命令查询NOR Flash状态代替 |

| VCC | 电源供应引脚(2.7v~3.6v) | 芯片供电电源 |

| GND | 地引脚 | 芯片电源地 |

| WP#/ACC | 硬件写保护/加速引脚 | 硬件写保护引脚,低电平有效 |

| NC | 不连接内部引脚 | 不用连接 |

3、NOR Flash于S3C2440连接图

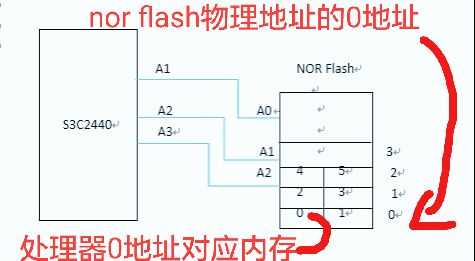

NOR Flash的数据宽度是16位的,与2440处理器的连接时,地址线必须错位进行连接。s3c2440的地址线A0悬空,A1连接NOR Flash的地址线A0,A2连接NOR Flash的地址线A1,依次排序。需要错位连接的原因是:2440处理器的每个地址对应的是一个BYTE 的数据单元,而 16-BIT 的 NOR FLASH 的每个地址对应的是一个HALF-WORD(16-BIT)的数据单元。为了保持匹配,所以必须错位连接。这样,从2440处理器发送出来的地址信号的最低位A0对16-BIT FLASH来说就被屏蔽掉了。

上面的描述过程太过抽象了,下面通过画图来解释错位连接的原因:

①、ARM处理器需要从地址0x0读取一个BYTE

②、ARM处理器需要从地址0x1读取一个BYTE

注意:有些ARM处理器内部可以设置地址的错位。对于支持软件选择地址错位的处理器,在连接16-BIT FLASH的时候,硬件上不需要把地址线错位。在设计的时候,应该参考芯片的数据手册,以手册为准,以免造成不必要的麻烦(如stm32连接是A0~A0)。

4、S3C2440驱动NOR Flash时序配置

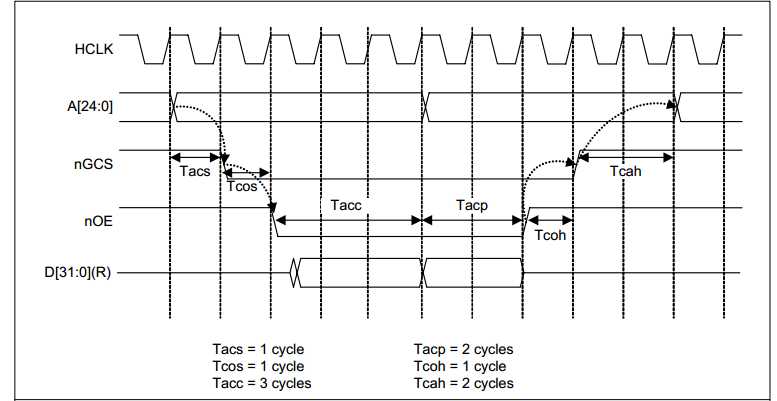

s2c2440内存控制器接读NOR Flash时序图

上图为s3c2440操作NOR Flash的读时序,Tacs表示片选使能前地址信号的设置时间(既地址信号需要设置多久,才能使能片选信号),Tcos表示OE#信号使能前片选使能的设置时间,Tacc表示数据的访问周期,Tcoh表示OE#信号释放后片选信号的保持时间,Tcah表示片选信号释放后地址信号的保持时间。由于s3c2440为通用性能的处理器,他的外部可能接不同公司生成的不同型号的NOR Flash,所以这些参数值要根据所接型号的NOR Flash的时序图进行设置。

下面根据NOR Flash芯片MX29LV60DBTI时序图来配置上述参数,MX29LV60DBTI的时序图如下图所示:

NOR Flash芯片MX29LV60DBTI读操作内部时序图

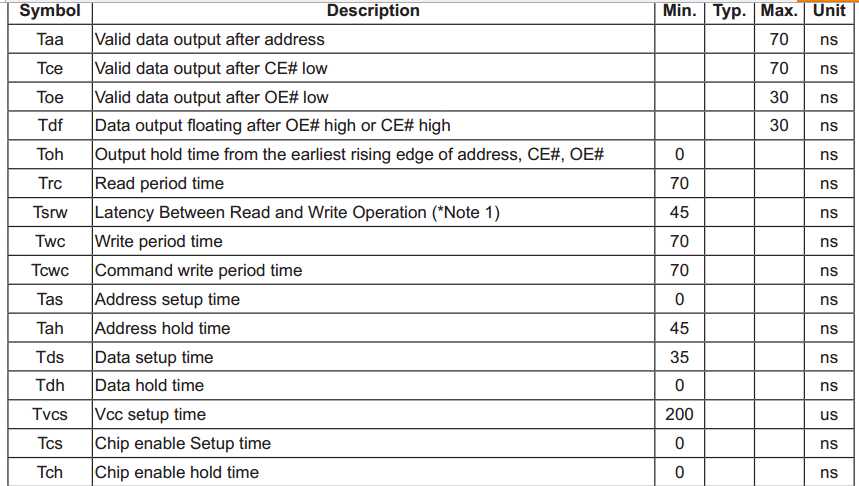

NOR Flash芯片MX29LV60DBTI时序图各参数具体值

Tce:片选信号使能后多久输出数据有效,最大值为70ns

Toe:读信号发出后多久输出数据有效,最大值为30ns

Taa:地址信号发出后数据有效,最大值为70ns

Trc:读周期时间,最小70ns

Tdf:OE#或CE#高时,数据引脚浮空时间,最大30ns(可以忽略设置,当读取数据结束后,新的读取信号发出,要过70ns,数据线上数据有效,这段引脚浮空时间无影响)

上述最大值表示发出该信号后,间隔最大值的时间后,数据引脚的信号一定是有效的,在这个范围之内,数据信号的引脚可能有效。

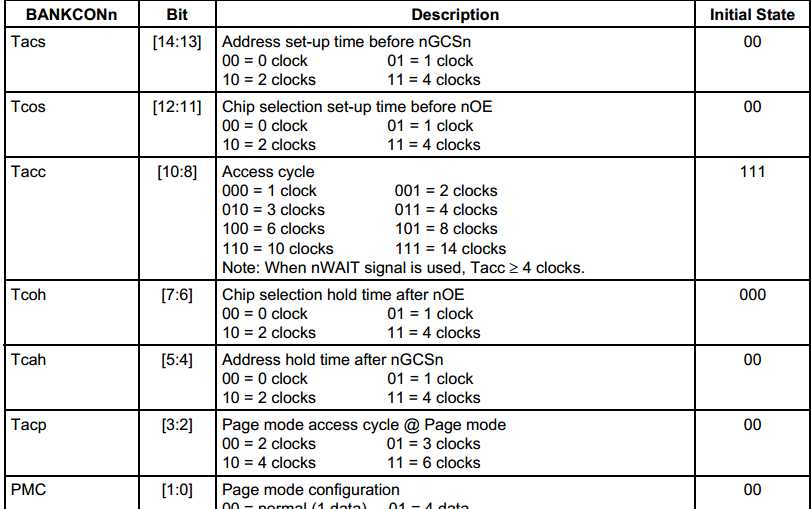

为简单,我们一般设置2440的CE#、OE#、ADD控制信号同时发出,保持70ns后进行读取数据引脚的数据。NOR Flash连接s3c2440的Bank0地址,配置时序的寄存器为BANKCON0,该寄存器的各个位如下图所示:

内存控制器的时钟信号由HCLK时钟信号提供,假设设置的HCLK的值为100M,1clock = 10ns。根据前面分析,Tacs、Tcos寄存器位设置为0,Tacc寄存器的为设置为101 = 8clocks。

5、NOR Flash的读操作

NOR Flash是类似于内存类的接口,读操作和内存的读取一样,直接发送相应的地址便能获取相应数据

unsigned int nor_read_word(unsigned int base, unsigned int offset)

{

volatile unsigned short *p = (volatile unsigned short *)(base + offset);

return *p;

}

unsigned int nor_dat(unsigned int offset)

{

return nor_read_word(NOR_FLASH_BASE, offset);

}

6、NOR Flash的扇区擦除

擦除NOR Flash扇区时,应先发送相应的命令,发送命令的顺序如下:

第1个总线周期:往555地址中写入AA

第2个总线周期:往2AA地址中写入55

第3个总线周期:往555地址中写入80

第4个总线周期:往555地址中写入AA

第5个总线周期:往2AA地址中写入55

第6个总线周期:往要擦除的扇区写入30

void nor_write_word(unsigned int base, unsigned int offset, unsigned int val)

{

volatile unsigned short *p = (volatile unsigned short *)(base + offset);

*p = val;

}

/* offset是基于cpu的角度看到 */

void nor_cmd(unsigned int offset, unsigned int cmd)

{

nor_write_word(NOR_FLASH_BASE, offset, cmd);

}

/* 等待烧写完成 : 读数据, Q6无变化时表示结束 */

void wait_ready(unsigned int addr)

{

unsigned int val;

unsigned int pre;

pre = nor_dat(addr);

val = nor_dat(addr);

while ((val & (1<<6)) != (pre & (1<<6)))

{

pre = val;

val = nor_dat(addr);

}

}

void erase_nor_flash_sector(unsigned int addr)

{

printf("erasing ...\n\r");

nor_cmd(0x555<<1, 0xaa); /* 解锁 */

nor_cmd(0x2aa<<1, 0x55);

nor_cmd(0x555<<1, 0x80); /* erase sector */

nor_cmd(0x555<<1, 0xaa); /* 解锁 */

nor_cmd(0x2aa<<1, 0x55);

nor_cmd(addr, 0x30); /* 发出扇区地址 */

wait_ready(addr); /* 等待操作完成 */

}

CPU外接NOR Flash,实际上就是将NOR Flash地址映射为CPU的统一编址。由于nor_cmd函数的offset是基于CPU的角度看到地址,而芯片手册上NOR Flash写入命令的地址从NOR Flash的实际物理地址,NOR Flash是16位的,它的0地址应该对应CPU的0地址和1地址。因此,NOR Flash的物理地址从CPU的角度来看,地址值应该是NOR Flash角度来看的两倍,所以在向某地址写入命令时,要将NOR Flash角度来看的地址右移一位。

7、NOR Flash的写操作

向NOR Flash地址中写入数据时,也应先发送相应的命令,发送命令的顺序如下:

第1个总线周期:往555地址中写入AA

第2个总线周期:往2AA地址中写入55

第3个总线周期:往555地址中写入A0

第4个总线周期:往要目标地址写入数据

void write_nor_flash(unsigned int addr,unsigned int val)

{

/* 烧写 */

nor_cmd(0x555<<1, 0xaa); /* 解锁 */

nor_cmd(0x2aa<<1, 0x55);

nor_cmd(0x555<<1, 0xa0); /* program */

nor_cmd(addr, val);

/* 等待烧写完成 : 读数据, Q6无变化时表示结束 */

wait_ready(addr);

}

写操作时值得注意的是,只有写入的目标的地址内容为0xff时,数据才能正确的写入,因此,一般情况下NOR Flash在写入时要对扇区进行擦除操作。NOR Flash在写入数据时只能将地址中的某位由1变0,而不能将某位由0变1。

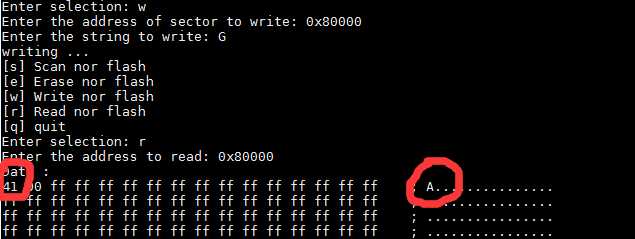

假设NOR Flash某地址中存放字符a(0x61),如果未进行擦除前向该地址中写入字符G(0x47),最后该地址内容为A(0x41)。原因如下:

字符a化为二进制--->1100001

字符G化为二进制--->1000111

由于写入时数据位只能由0变为1,最终结果100001,相当于执行原始数据和新写入数据进行&操作

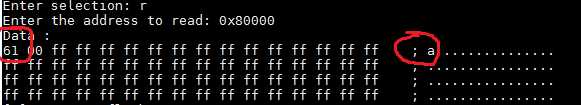

向NOR Flash执行上述步骤,验证上述过程

①、向0x80000地址写入a字符

②、未进行擦除扇区向0x80000地址写入G字符,接着读取这个地址里的数据,实际读取内容为0x41,不是0x47,结果符合上面描述。

使用s3c2440芯片对外挂的nor flash进行读写擦除操作

标签:控制器 因此 处理器 函数 表示 屏蔽 stm32 匹配 运行

原文地址:https://www.cnblogs.com/cjhk/p/11665104.html