标签:完成后 能力 alt 参与 实现 编程 ted 处理 cut

| ARM | MIPS | |

| 安全性总览 |

基于trust zone构建,区分为一个安全世界与一个正常世界,正常世界不可以访问安全世界的存储空间等部件,正常世界信任安全世界,安全世界中的指令互相信任。 |

基于虚拟化CPU的硬件,允许存在多个域,并且每个域都是独立被保护的,互相不信任其他域中的软件或是数据,MIPS-VZ最多允许255个独立域。这些域运用于不同的模式下:内核模式以及用户模式。 |

| ARMv8-M和MIPS-VZ都使用了额外的执行执行模式给与most trusted code以更多权限,同时减少less trusted code的权限 | ||

| 存储管理中的安全性 | ARMv8-M使用了两个模块解决存储单元访问问题,分别是SAU(安全属性单元)以及MPU(存储保护单元)。SAU检查安全/不安全模式,然后MPU在不同模式下利用不同的权限访问,这两个单元基于地址比较器 |

是用了有如下两个特点的MMU:1.大系统区分为客人TLB和根TLB的两层TLB系统,分别给客户OS与内核软件使用。2.小系统区分为两级MMU,客人部分可以是一个完整的TLB也可以是一个固定映射转换单元,根部分将TLB拆成没有物理地址的部分,成为根保护单元(RPU). 这种MMU基于CAM(?),较好地提供了应用软件与操作系统之间的绝缘。 |

| 不同安全域之间的例程调用 | ARMv8-M拥有一种不使用SMC(secure monitor call)指令就可以从正常世界调用安全世界特定例程的能力。这种能力使用到了SG(secure gateway)指令,用于标记进入安全世界的地址(不可以从例程的中部进入),安全性不高。 |

在不同客人/域之间分享例程的能力是等价的,会被MMU的根部分(root portion)编程并产生,而这些被分享的部分只可以被执行(不可读或写,这些权限是被MMU所监控的)。 在这种比较中,MIPS相较于ARM会更加快速,因为MIPS不需要使用SG指令和SC指令后的跳转指令去进入被调用的例程。 此外,根环境下的软件和安全码用于推行MIPS虚拟化模型提供的保护,这意味着这种保护对于应用来说大部分都是透明的。根环境中的软件不以牺牲对于操作环境的控制为代价完全监控着客人的活动。 |

| 中断处理中的安全性 | ARMv8-M在安全执行模式下(secure execution mode)支持更快的ARM中断方案。 |

MIPS-VZ支持所有快速MIPS中断方案,可以被直接执行于各个客人或是根部,从而不会影响到内核软件或是安全性。 |

| SOC安全性 | ARMv8-M支持传统的TZ HNONSEC fabric signal以及HPROT memory attribute signal以便通知IO设备是正常世界或是安全世界的访问。 | MIPS-VZ支持multi-bit GuestID signals以通知IO设备是哪一个客人发出的存储请求。 |

| 不同域的转换 | 正常世界和安全世界之间的转换需要保存/载入通用寄存器(GPRs)以及浮点数寄存器(FPRs)。 |

在客人与根域之间转换的时候不需要保存/载入COP0(MIPS结构中保存特权控制/状态寄存器、MMU、异常逻辑寄存器exception logic register的结构),因为所有域中都有COP0的备份,但GPR以及FPR都需要保存/载入。然而有些时候Shadow register set特性可以与CPU虚拟化结合使用,如GPR shadow set让我们不需要保存/载入GPR。 在客人域之间转换的时候COP0、GPRs、FPRs都要保存/载入。 |

| 应用与市场 | 目前ARMv8有两个主要功能,ARMv8-R用于工业控制设备中的嵌入式应用,ARMv8-A则主要用于移动端。此外,ARM也在开发不同的扩展部分,例如有些支持java加速,也包括Jazelle、TrustZone、SIMD等应用。 | MIPS优势之一就是有很多开源工具,且对新手较为友好。目前MIPS管理部门希望减少CPU资源的消耗以降低系统资源的使用,这种方式也使得MIPS不易出现错误;MIPS也因其低功耗被集成于移动设备中,但事实上在这一方面MIPS落后于ARM,目前MIPS的复兴主要依托于中国市场的支持以及更多核CPU的开发。 |

| 架构 | ARM最特殊的一点就是它采用了高密度的16-bit压缩指令集Thumb,并可以在ARM与Thumb之间相互转换,这使得ARM在保持高密度的同时也有了较好的灵活性。 | 相对来说较为简单,可以用较少的指令完成一系列复杂任务,同时也使得MIPS功耗较低。此外,MIPS拥有存储管理单元(MMU)以更高效使用存储单元,减少不必要的损失,这也使得MIPS功耗进一步降低。 |

| 寻址方式 |

前变址寻址(pre-index adressing) 带回写的前变址寻址(Pre-indexed Addressing with Write Back) 后变址寻址(post-index addressing) 程序指针相对寻址(Program Counter Relative Addressing) |

寄存器寻址 立即数寻址 PC相对寻址 伪直接寻址(pseudo-direct addressing存在于J型指令中,指令中地址26bits,可以通过如下操作转换成32bits地址:PC[31:27]+26bits+00) 基地址寻址 |

|

操作模式 |

ARM具有七个基本操作模式:用户模式,特权模式(privileged mode),异常模式(exception mode,包括SVC, SWI, ABT, UND, IRQ),以及快速中断模式(Fast Interrupt mode) | MIPS具有两个操作模式:kernel(内核)模式以及用户模式,内核模式的状态位为0,可以访问或更改任意寄存器,改模式可以用于处理异常、错误、中断或开机时。用户模式时状态位为1,相较于内核模式其权限较低,同时也保证了用户之间不会干扰。 |

| 异常处理 | ARM在ARM模式下进行异常处理。当中断出现时,当前状态寄存器CPSR会将当前值存储到存储状态寄存器SPSR,然后修改CPSR中的值并处理异常。PC在异常处理结束后跳转回原地址。 |

MIPS异常处理是通过coprocessor0实现的,当中断出现时,异常程序指针(EPC)会储存PC的值,然后PC跳转到中断处理指令,接着,运行模式会从用户模式跳转到内核模式。当异常处理完成后,PC会回到原PC+4的地方。 共有4个主要寄存器参与异常处理:reg8(储存中断开始时的存储地址),reg12(状态位),reg13(存储异常类型),reg14(EPC) |

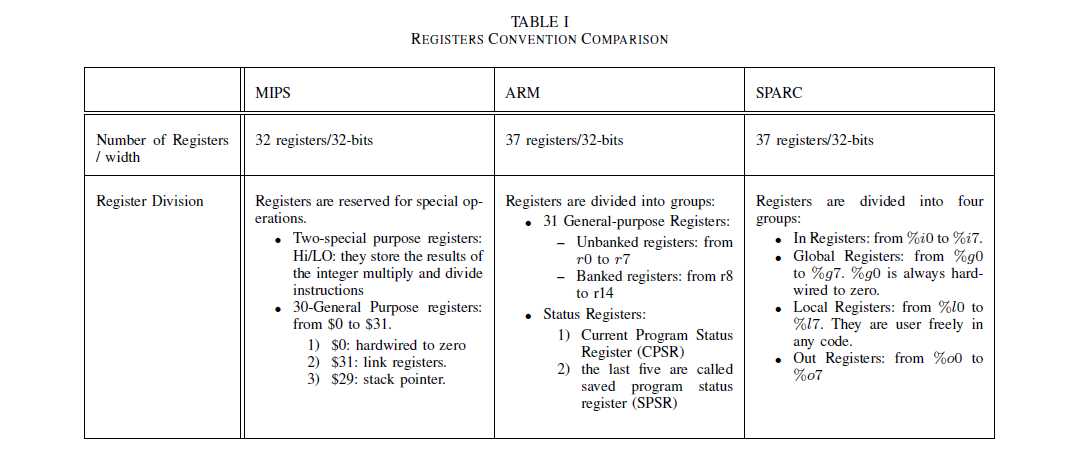

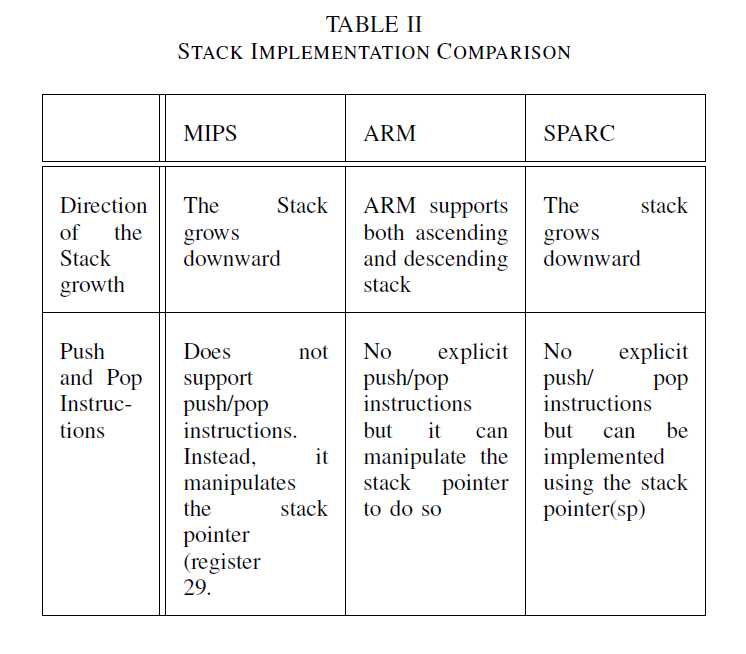

此外,在寄存器以及堆栈方面,ARM与MIPS也有不同,具体见TABLE I 和 TABLE II(来源:El Kady, S., Khater, M., Alhafnawi, M.: MIPS, ARM and SPARC-an architecture comparison. In: Proceedings of the World Congress on Engineering, vol. 1 (2014))。

本文来源:

1.El Kady, S., Khater, M., Alhafnawi, M.: MIPS, ARM and SPARC-an architecture comparison. In: Proceedings of the World Congress on Engineering, vol. 1 (2014)

2.MIPS,https://www.mips.com/

标签:完成后 能力 alt 参与 实现 编程 ted 处理 cut

原文地址:https://www.cnblogs.com/AAgnosticEngineer/p/11668975.html