标签:控制 复位 采集 bank 图片 http 速度 知识 基础知识

1、前言

DDR的全称为Double Data Rate SDRAM,也就是双倍速率的SDRAM,SDRAM在一个CLK周期传输一次数据,而DDR在一个CLK周期传输两次数据,分别在上升沿和下降沿各传输一次数据,该概念称为预取,在描述DDR速度的时候一般使用MT/s单位,也就是每秒多少兆次数据传输。

2、DDR结构框图

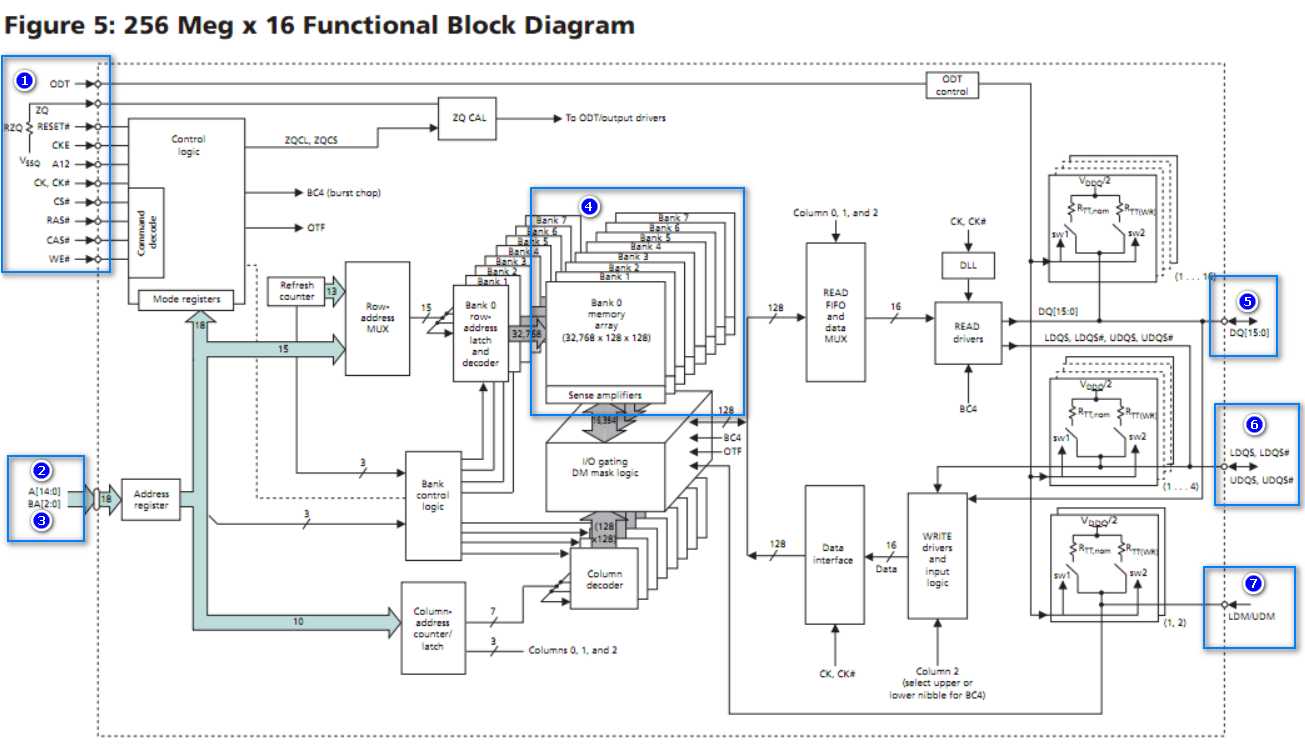

接下来将以Micro的DDR3L芯片MT41K256M16进行结构框图的介绍,该芯片是一款512MB的DDR3L内存芯片,框图如下所示:

接下来对上面给出的框架图各个标号进行简单介绍:

(1)控制线

ODT:片上终端使能,ODT使能和禁止片内终端电阻;

ZQ:输出驱动较准的外部参考引脚,应外接一个RZQ电阻到VSSQ,一般接到地;

RESET:芯片复位引脚,低电平有效;

CKE:时钟使能引脚;

A12:A12为地址引脚,也叫做BC引脚,有另外一个功能,A12会在READ和WRITE命令期间被采样,以决定burst chop是否会被执行;

CK,CK#:时钟信号线,DDR3的时钟线是差分时钟线,所以的控制信号和地址信号都会在CK的上升沿和CK#的下降沿交叉处采集;

CS#:片选信号,低电平有效;

RAS#:行地址选通信号;

CAS#:列地址选通信号;

WE#:写使能信号。

(2)地址线

A[14:0]:

(3)Bank选择线

BA[2:0]:

(4)Bank区域

(5)数据线

DQ[15:0]:

(6)数据选通引脚

LDQS,LDQS#:

UDQS,UDQS#:

(7)数据输入屏蔽引脚

LDM/UDM:

标签:控制 复位 采集 bank 图片 http 速度 知识 基础知识

原文地址:https://www.cnblogs.com/Cqlismy/p/11965334.html