标签:event until nal wait eve arch src image variable

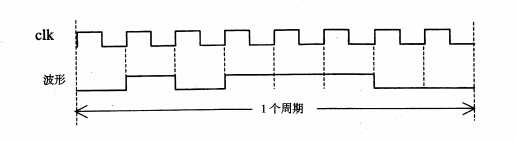

信号发生器要求:

信号发生器程序:

library ieee;

use ieee.std_logic_1164.all;

entity signal_gen1 is

port(

clk:in bit;

wave:out bit

);

end signal_gen1;

architecture bhv of signal_gen1 is

begin

process

variable count: integer range 0 to 7;

begin

wait until clk‘event and clk=‘1‘;

case count is

when 0 => wave <=‘0‘;

when 1 => wave <=‘1‘;

when 2 => wave <=‘0‘;

when 3 => wave <=‘1‘;

when 4 => wave <=‘1‘;

when 5 => wave <=‘1‘;

when 6 => wave <=‘0‘;

when 7 => wave <=‘0‘;

end case;

count := count+1;

end process;

end bhv;

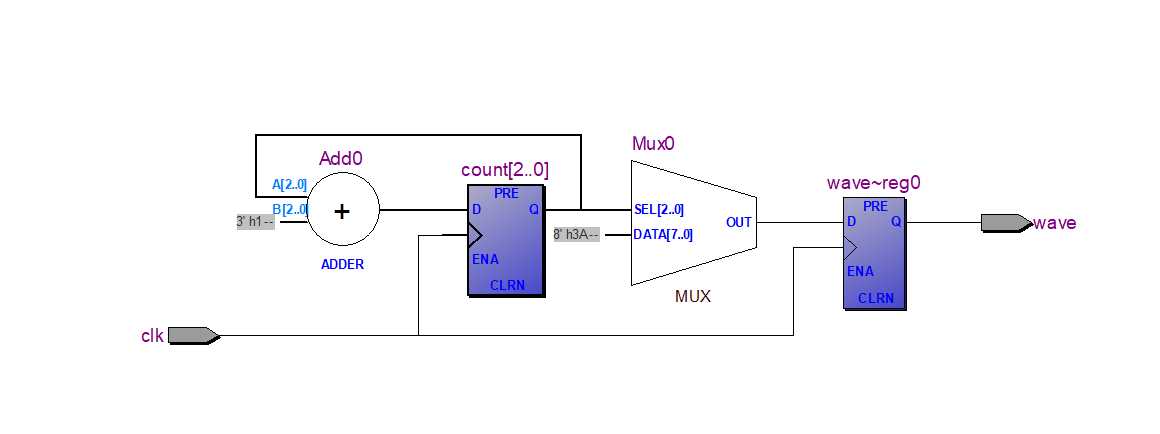

RTL原图:

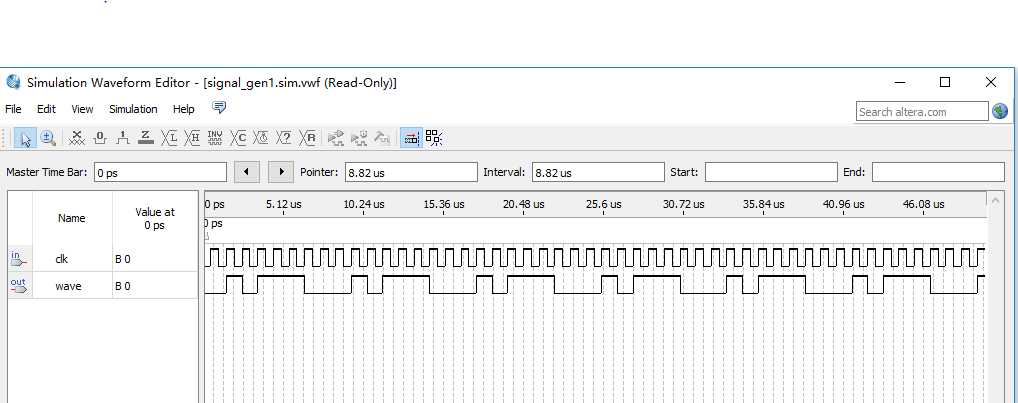

仿真图:

标签:event until nal wait eve arch src image variable

原文地址:https://www.cnblogs.com/lhkhhk/p/11966788.html