标签:NPU altera roc file 转换器 map int http eve

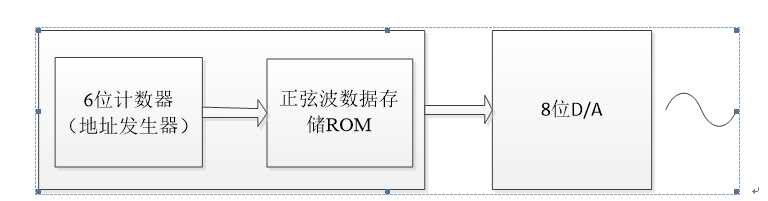

正弦信号发生器的结构由3部分组成:

1、计数器或地址信号发生器,要根据ROM大小来确定地址发生器宽度。(其实验选择6位地址信号发生器给ROM)

2、正弦信号数据存储ROM(地址宽度6位,数据宽度8位),包含64个字的完整正弦波数据(1个完整周期)

3、8位D/A模块(采用TLC5602超高频数模转换器),实现数模转换,输出模拟正弦波信号。

结构图

在正弦信号发生器结构图中,地址信号发生器的时钟信号有clk提供,假设其频率为f0,正弦波数据ROM中存放每周期64个字节的波形数据,则8位

D/A转换后的正弦信号频率为:f=f0/64.

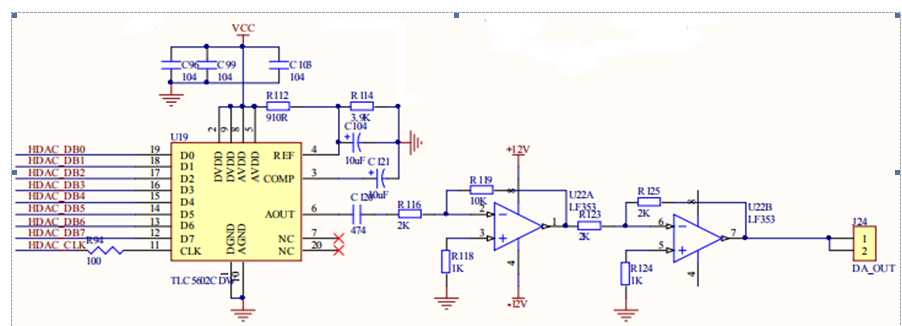

TLC5602X电路图:

并行DAC电路原理图

1、产生6位计数器(地址发生器)

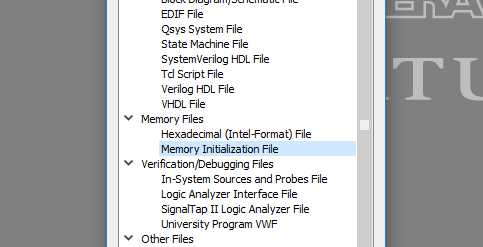

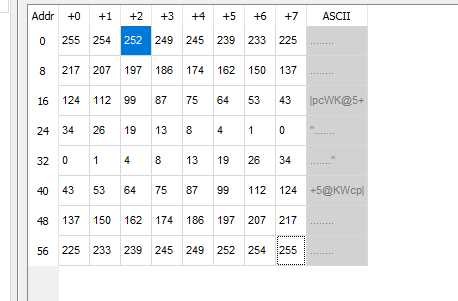

(1)、生成mif文件

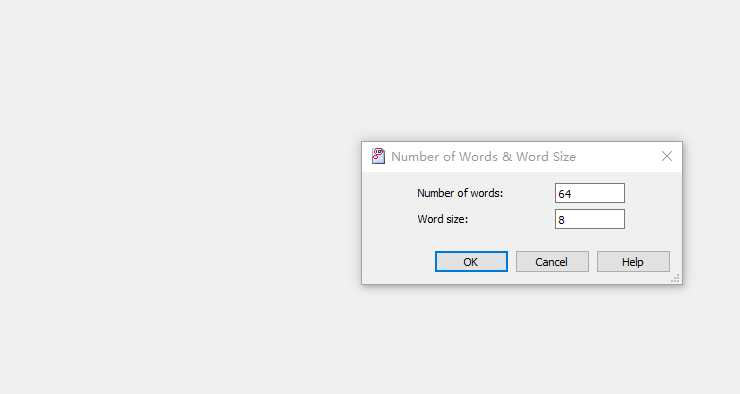

(2)、6位地址,64个字,8位宽。

(3)、生成包含完整周期的正弦波数据

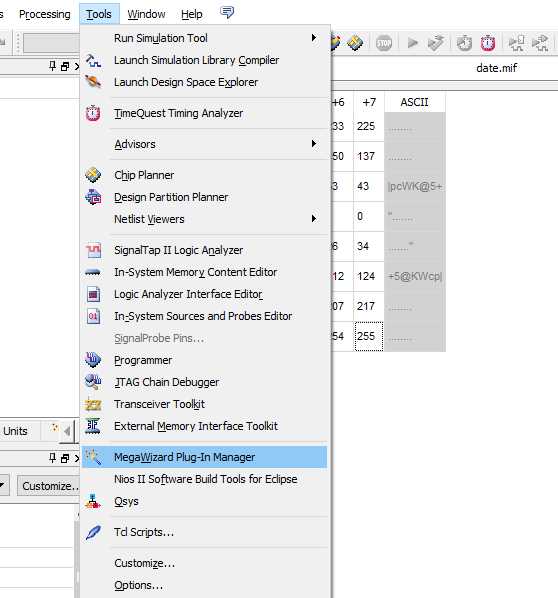

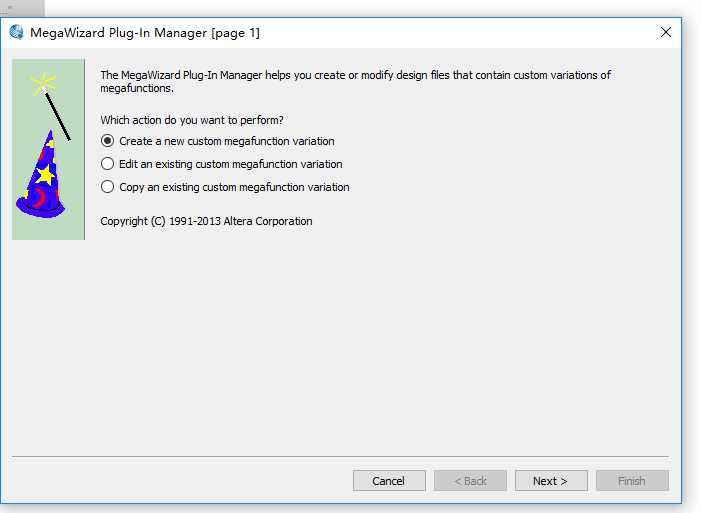

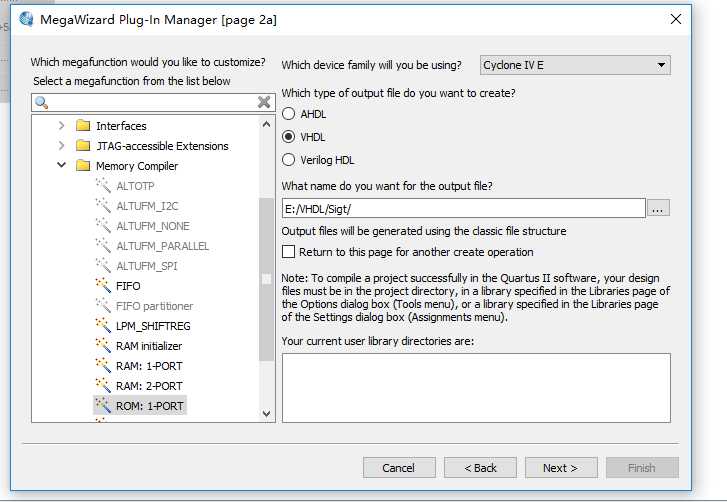

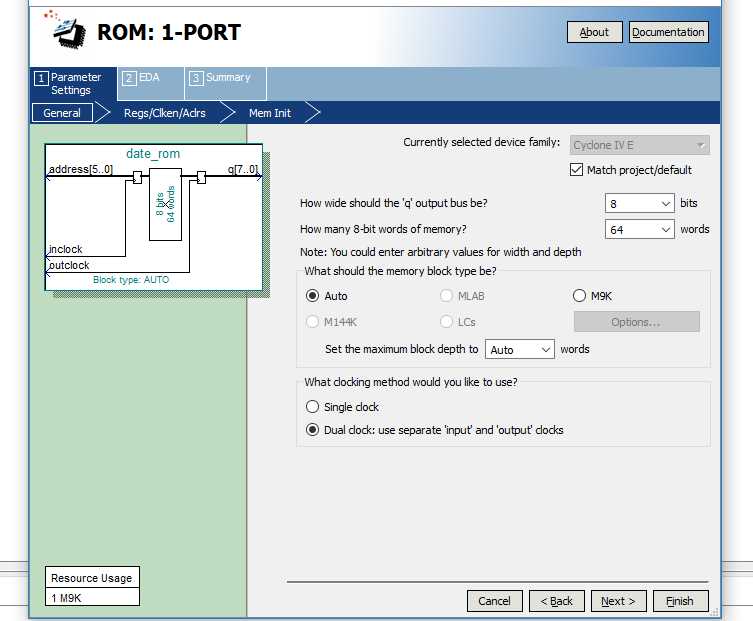

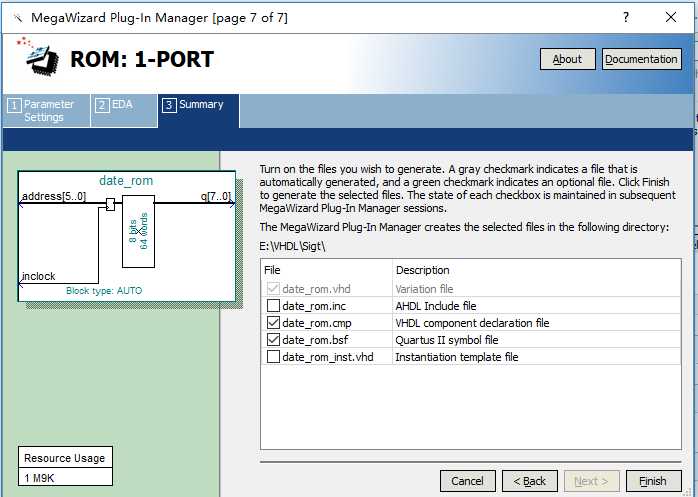

2、创建正弦波数据存储ROM

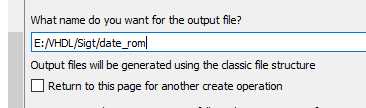

(1)、选择路径

(2)、创建

(3)、选择产生的rom

(4)、添加文件

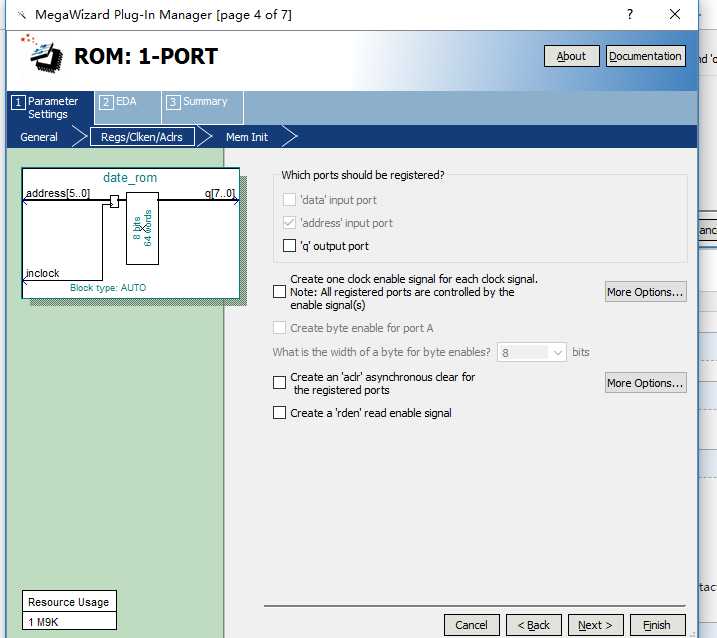

(5)、更改时钟,选择周期

(6)、去掉多余输出

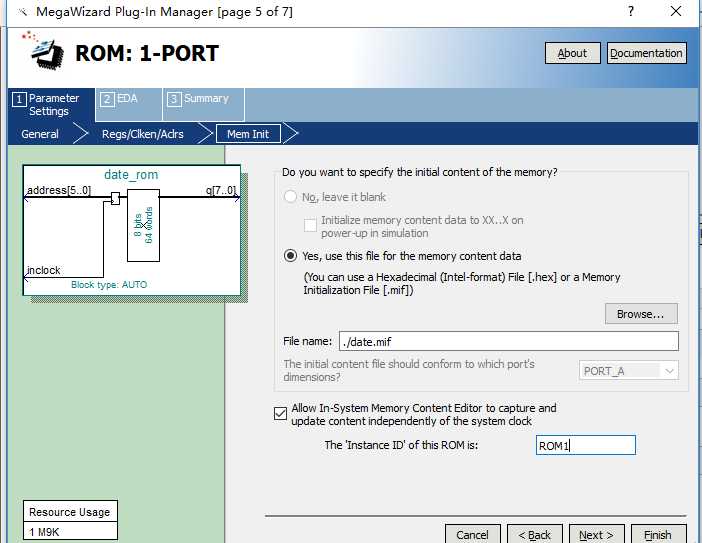

(7)、添加,fim文件

(8)、选中

产生文件程序:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY altera_mf;

USE altera_mf.all;

ENTITY date_rom IS

PORT

(

address : IN STD_LOGIC_VECTOR (5 DOWNTO 0);

inclock : IN STD_LOGIC := ‘1‘;

q : OUT STD_LOGIC_VECTOR (7 DOWNTO 0)

);

END date_rom;

ARCHITECTURE SYN OF date_rom IS

SIGNAL sub_wire0 : STD_LOGIC_VECTOR (7 DOWNTO 0);

COMPONENT altsyncram

GENERIC (

address_aclr_a : STRING;

clock_enable_input_a : STRING;

clock_enable_output_a : STRING;

init_file : STRING;

intended_device_family : STRING;

lpm_hint : STRING;

lpm_type : STRING;

numwords_a : NATURAL;

operation_mode : STRING;

outdata_aclr_a : STRING;

outdata_reg_a : STRING;

widthad_a : NATURAL;

width_a : NATURAL;

width_byteena_a : NATURAL

);

PORT (

address_a : IN STD_LOGIC_VECTOR (5 DOWNTO 0);

clock0 : IN STD_LOGIC ;

q_a : OUT STD_LOGIC_VECTOR (7 DOWNTO 0)

);

END COMPONENT;

BEGIN

q <= sub_wire0(7 DOWNTO 0);

altsyncram_component : altsyncram

GENERIC MAP (

address_aclr_a => "NONE",

clock_enable_input_a => "BYPASS",

clock_enable_output_a => "BYPASS",

init_file => "date.mif",

intended_device_family => "Cyclone IV E",

lpm_hint => "ENABLE_RUNTIME_MOD=YES,INSTANCE_NAME=ROM1",

lpm_type => "altsyncram",

numwords_a => 64,

operation_mode => "ROM",

outdata_aclr_a => "NONE",

outdata_reg_a => "UNREGISTERED",

widthad_a => 6,

width_a => 8,

width_byteena_a => 1

)

PORT MAP (

address_a => address,

clock0 => inclock,

q_a => sub_wire0

);

END SYN;

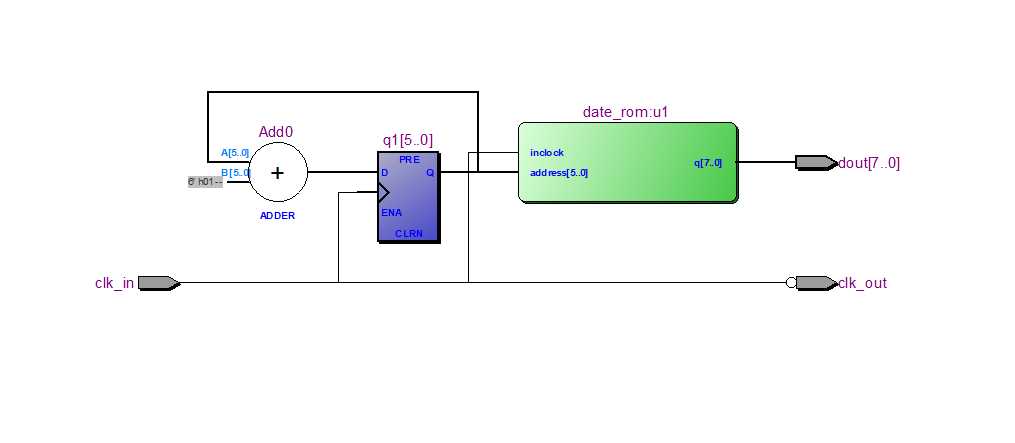

3、正弦信号发生器顶层设计

程序:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity signt is

port(

clk_in:in std_logic;

dout:out std_logic_vector(7 downto 0);

clk_out:out std_logic

);

end;

architecture bhv of signt is

component date_rom

port(

address : IN STD_LOGIC_VECTOR (5 DOWNTO 0);

inclock : IN STD_LOGIC := ‘1‘;

q : OUT STD_LOGIC_VECTOR (7 DOWNTO 0)

);

end component;

signal q1:std_LOGIC_VECTOR(5 downto 0);

begin

process(clk_in)

begin

if clk_in‘event and clk_in=‘1‘ then

q1<=q1+1;

end if;

end process;

u1:date_rom port map(address=>q1,q=>dout,inclock=>clk_in);

clk_out<=not clk_in;

end;

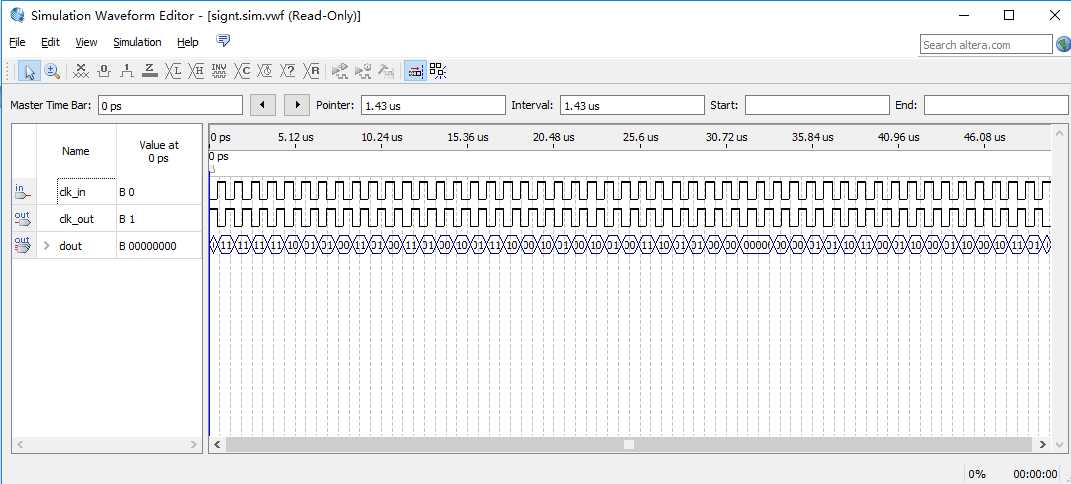

仿真图:

rtl原图:

标签:NPU altera roc file 转换器 map int http eve

原文地址:https://www.cnblogs.com/lhkhhk/p/11972432.html