标签:显示 上传 log 检查 波形 png none one fpga

Xilinx Vivado 提供了上板后的FPGA逻辑分析,信号视图显示等功能。

需要注意,上板后查看信号需要重新综合,并且需要耗费一定的片上布局布线资源。

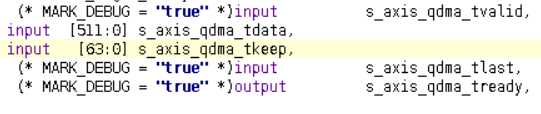

1. 添加debug信号

可以对模块端口或者wire 变量进行debug信号提取,只要在verilog代码前面添加:(* MARK_DEBUG = "true" *) 即可:例如,

此时需要跑综合,检查错误并分析语义。并且通过vivado综合,进行下一步。

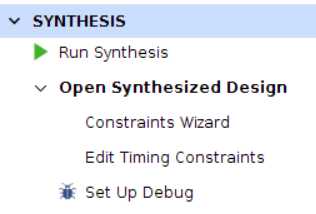

2. 配置debug信号

配置debug信号,用于挑选需要进行真正查看的信号名称。在写代码时可以添加很多debug标签,但是debug耗费片上资源,看哪一部分,实现哪一部分。

点击SYNTHESIS -> Set Up Debug。

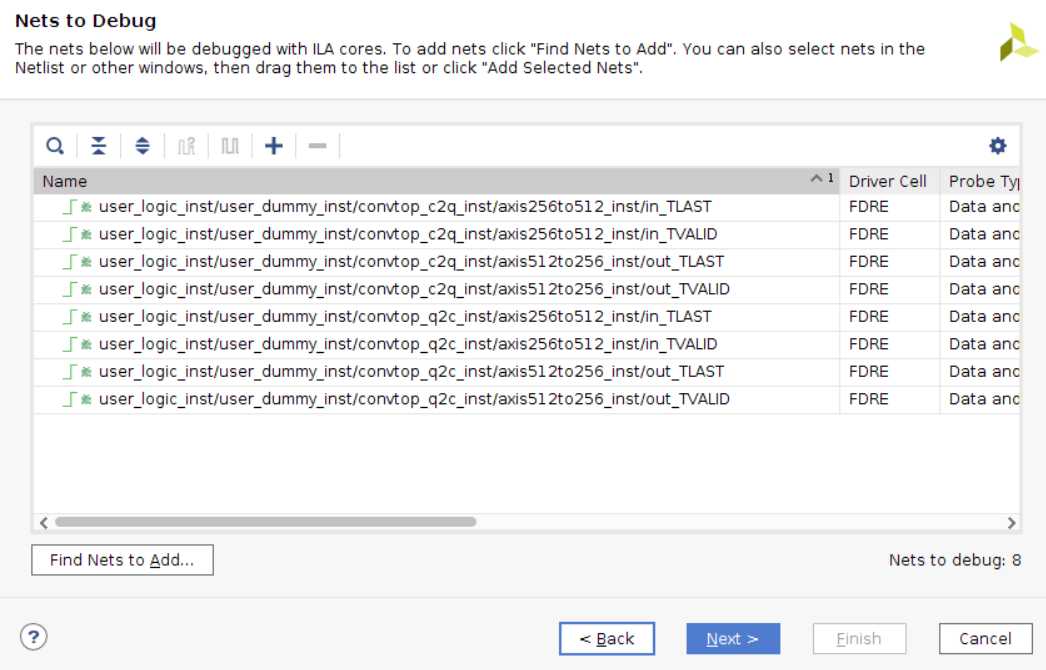

选好需要debug的信号后:

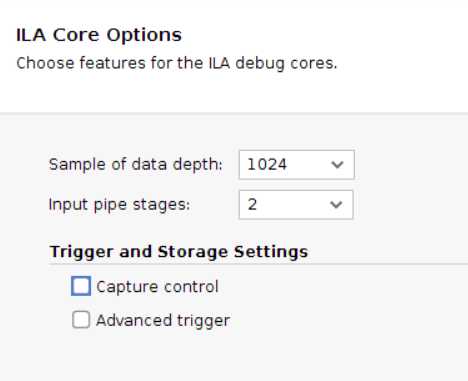

选择信号的缓存深度。由于片上信号速率大,我们不可能实时捕捉并上传,只能首先储存到片上逻辑分析core中,所以我们需要选择core的存储容量,一个深度对应为一个时钟周期,也就是我们存储多少时钟周期的debug信号值,之后会选择debug信号的记录触发条件,当满足何条件之后才开始缓存,帮助我们抓取特定时间窗口内的所有信号的波形图,一般我们先设定深度1024,输入节拍数为2:

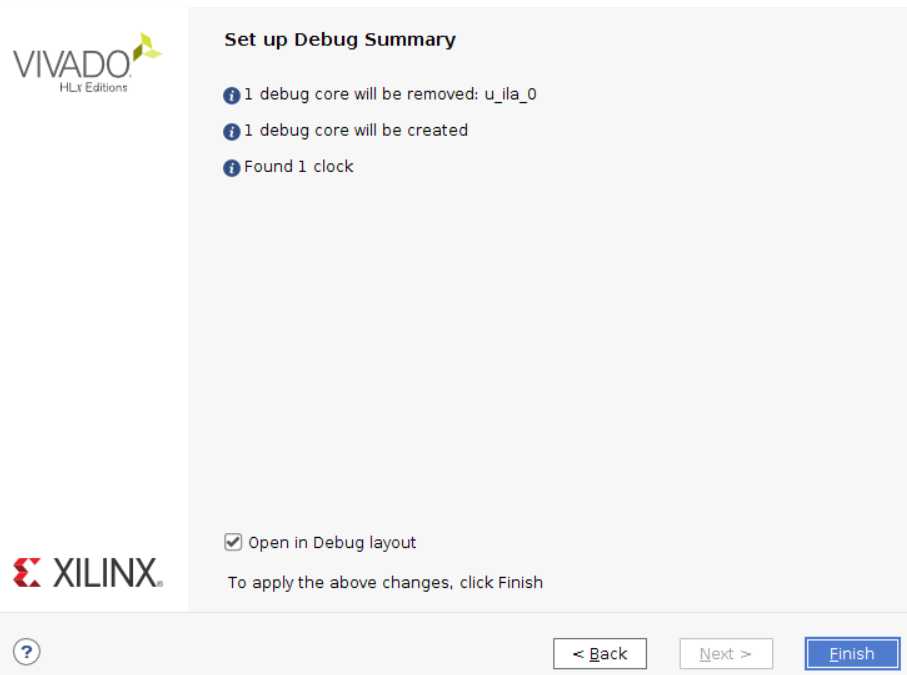

完成:

之后vivado会修改工程的约束文件,进而我们需要重新再综合一次工程。之后再布局布线,timing保证没错误的前提下,即可生成bit文件并下载入FPGA,最后搭建测试场景并开始运行。

3. 使用JTAG仿真器在线仿真

首先,打开硬件管理器

未完待续。。。

20点39分12月6日2019年

Xilinx FGPA 上板调试 集成逻辑分析工具 Integrated Logic Analyzer(ILA) 简单配置

标签:显示 上传 log 检查 波形 png none one fpga

原文地址:https://www.cnblogs.com/pandaroll/p/11997589.html