标签:amp 计数 img 计算器 信号 out 相同 接下来 define

------------恢复内容开始------------

------------恢复内容开始------------

蜂鸣器分无源和有源蜂鸣器

信号名 FPGA管脚

CLK E1

RESET M1

KEY0 E16

BEEP D12

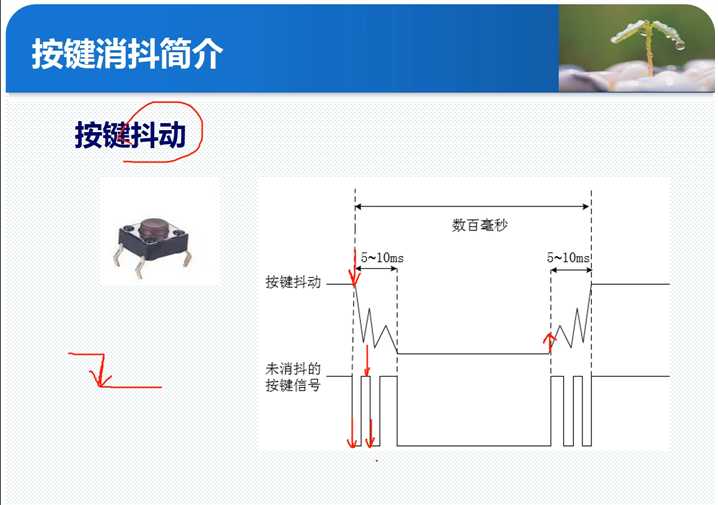

一、按键消抖

在按键按下时会产生延时 因此我们需要进行消抖,像在51单片机中我们是通过延时函数进行消抖,其两者的原理也大致相同

产生20ms 的方法

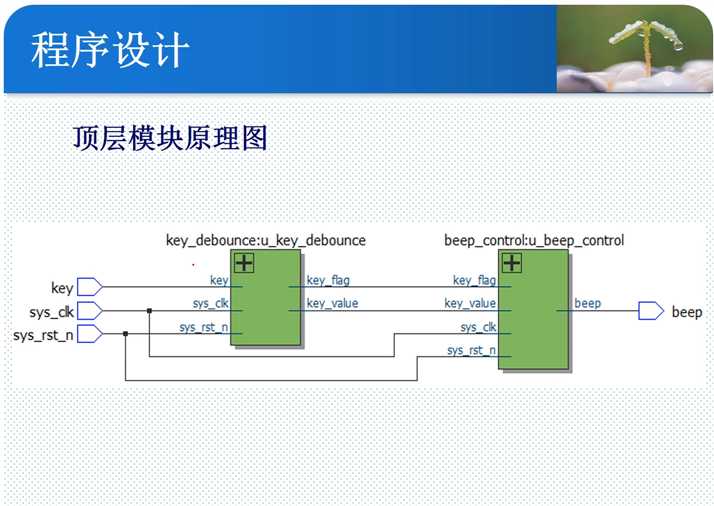

二、顶层模块原理图

首先顶层模块例化了两个模块 key_debounce 和beep_control

这其中涉及到了数电知识

从图中有三个输入端 和一个输出端

代码分为三个模块

key_debounce.v

module key_debounce(

input sys_clk, //外部时钟

input sys_rst_n, //外部复位信号,低有效

input key,

output reg key_flage,//按键数据有效信号

output reg key_value //按键消抖

);

reg [19:0] delay_cnt; //延时计数器

reg key_reg;

//延时计数器的功能

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)begin //如果复位信号为低电平时

key_reg <= 1‘b1; //给这个key_reg赋初值,为什么1,因为按键没有按下时是高电平,因此要保持按键状态是1

delay_cnt <=20‘d0;

end

else begin //复位结束后,把key的值寄存到key_reg里面去

key_reg <= key;

if(key!= key_reg)//一旦key发生改变,我们需要给delay_cnt赋初值

delay_cnt <= 20‘d1000_000;

else begin //说明key的值不变,计数器递减

if(delay_cnt > 20‘d0)

delay_cnt <= delay_cnt - 1‘b1;

else

delay_cnt <= 20‘d0;

end

end

end

//在延时计数器写完之后,接下来我们需要判断计数器的值,来输出我们按键消抖之后的结果

//此为按键消抖模块

always @(posedge sys_clk or negedge sys_rst_n )begin

if(!sys_rst_n)begin

key_value <= 1‘b1;

key_flage <= 1‘b0;

end

else begin

if(delay_cnt == 20‘d1)begin //当计数器递减到1时,说明按键稳定状态维持了20ms

key_flage <= 1‘b1; //此时消抖过程结束,给出一个时钟周期的标志信号

key_value <= key; //并寄存此时按键的值

end

else begin

key_flage <= 1‘b0; //将标志信号拉低

key_value <= key_value;//保持值不变

end

end

end

endmodule

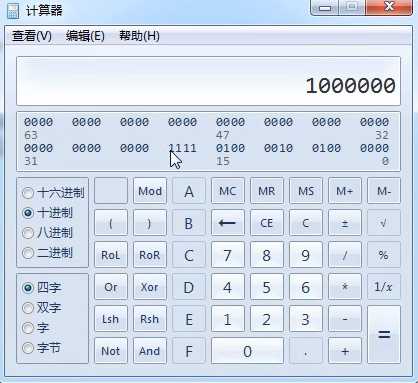

延时20ms 就是20*10的6次方nm,系统时钟为50MHz,就是说时钟周期为20nm,20mm÷20nm = 10的六次方,从计算器可以看到十进制数对应的二进制数的位宽为20

因此定义成[19:0] delay_cnt 计数器 表示计数器的位宽为20位。

接下来是蜂鸣器模块

module beep_control( input sys_clk, //外部时钟 input sys_rst_n, //外部复位信号,低有效 output reg key_flage,//按键数据有效信号 output reg key_value, //按键消抖 output reg beep ); always @(posedge sys_clk or negedge sys_rst_n )begin if(!sys_rst_n) beep <= 1‘b1; else if(key_flage & (~key_value)) // 如果判断flag为1,那么消抖结束于此同时还要判断value的值 beep <= ~beep; else beep <= beep; end endmodule

最后是顶层文件

module top_key_beep( input sys_clk, //时钟信号50Mhz input sys_rst_n, //复位信号 input key, //按键信号 output beep //蜂鸣器控制信号 ); //wire define //线网类型变量 wire key_value; wire key_flage; //***************************************************** //** main code //***************************************************** //例化按键消抖模块 key_debounce u_key_debounce( .sys_clk (sys_clk), .sys_rst_n (sys_rst_n), .key (key), .key_flage (key_flage), .key_value (key_value) ); //蜂鸣器控制模块 beep_control u_beep_control( .sys_clk (sys_clk), .sys_rst_n (sys_rst_n), .key_flage (key_flage), .key_value (key_value), .beep (beep) ); endmodule

拓展实验

------------恢复内容结束------------

------------恢复内容结束------------

标签:amp 计数 img 计算器 信号 out 相同 接下来 define

原文地址:https://www.cnblogs.com/fanxiaohao/p/12172910.html