标签:col 过程 不能 延时 放大 丢失 读写 bank ram

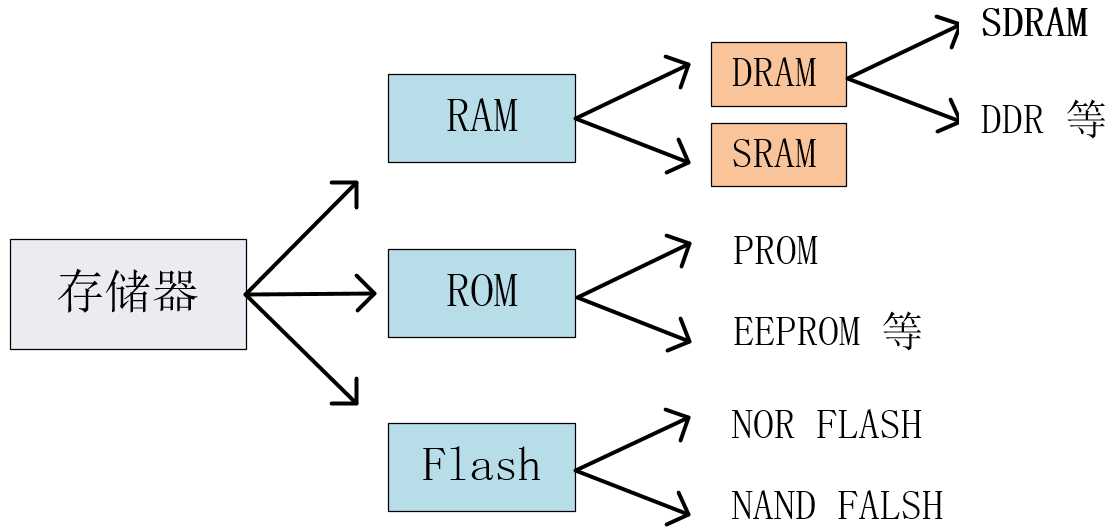

一、存储器类型

1、RAM,随机存取存储器(Random Access Memory),也叫主存,是与 CPU 直接交换数据的内部存储器。可按地址进行读写,掉电后数据会丢失。

(1)DRAM:动态RAM,使用电容的电量来表示逻辑 0 和 1,电容充放电的特性导致其需要不断的刷新来保证数据不丢失。存储容量较大,多用于数据存储。常见的有 SDRAM 和 DDR。

(2)SRAM:静态RAM,使用触发器的两个稳定状态来表示逻辑 0 和 1,不需要刷新操作。存储容量一般较小,但读写速度快。

2、ROM,只读存储器(Read Only Memory),数据只能读出而不能写入,掉电后数据不丢失。数据写入需要特定条件,数据存取慢。

(1)PROM:可编程ROM,出厂后可修改内部数据,但只能修改一次。多用于存储不修改的数据,如设备ID,制造厂商编码。

(2)EEPROM:电子可擦除的ROM,内部数据可以反复进行修改。多用于掉电后扔需存储的数据。

3、Flash,快闪存储器(Flash Memory),可读可写,掉电后数据不丢失,数据存取快。

(1)NOR FLASH:容量小,读写速度快,程序可以在里面直接运行。

(2)NAND FLASH:容量大,读写速度慢,数据以块的形式读写,一般为 512 Byte,不能对单独的字节进行操作。

二、SDRAM简介

SDRAM 全程是 Synchronous Dynamic Random Access Memory,即同步动态随机存储器,同步指内存工作需要同步时钟,动态指需要不停地刷新来保证数据不丢失,随机指数据读写可以制定地址进行操作。SDRAM 存储数据是利用了电容能够保持电荷以及其充放电的特性。SDRAM具有空间存储量大、读写速度快、价格相对便宜等优点。然而由于 SDRAM 内部利用电容来存储数据,为保证数据不丢失,需要持续对各存储电容进行刷新操作;同时在读写过程中需要考虑行列管理、各种操作延时等,由此导致了其控制逻辑复杂的特点。

1、SDRAM内存计算

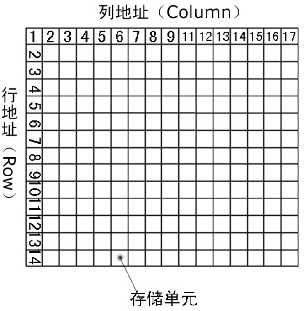

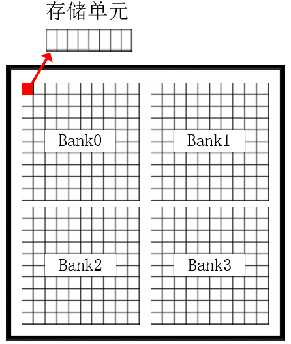

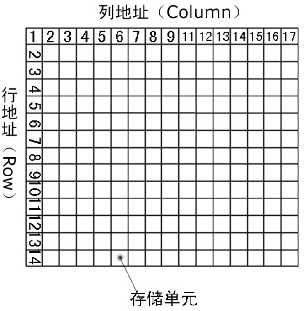

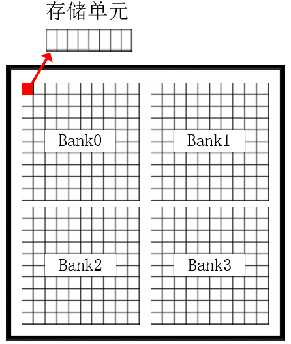

SDRAM 的内部是一个存储阵列,就像一张表格,我们在向这个表格中写入数据的时候,需要先指定一个行(Row),再指定一个列(Column),就可以准确地找到所需要的“单元格”,这就是 SDRAM 寻址的基本原理。图中的“单元格”就是 SDRAM 存储芯片中的存储单元,而这个“表格”(存储阵列)我们称之为 L-Bank。

通常 SDRAM 的存储空间被划分为 4 个 L-Bank,在寻址时需要先指定其中一个 L-Bank,然后在这个选定的 L-Bank 中选择相应的行与列进行寻址(寻址就是指定存储单元地址的过程)。对 SDRAM 的读写是针对存储单元进行的,对 SDRAM 来说一个存储单元的容量等于数据总线的位宽,单位是 bit。那么 SDRAM 芯片的总存储容量我们就可以通过下面的公式计算出来:SDRAM总存储容量 = 行数 × 列数 × L-Bank的数量 × 存储单元的容量

本次设计采用的 SDRAM 芯片为 Winbond W9812G6KH - 6,查询数据手册发现其容量为:2M × 4 banks × 16 bits = 128 Mbit,其中 2M 为“行数×列数”,4为 L-Bank 数量,16 为单个存储单元的容量,即数据位宽。因此每个 Bank 能存储 32 Mbit(33554432 bit)的数据,这些数据组成 4096行 x 512列,每个存储单元存储 16bit 的数据。

2、SDRAM存取原理

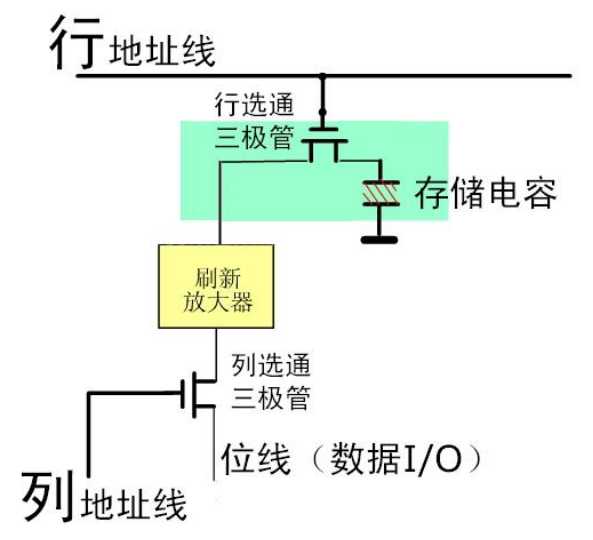

SDRAM存储数据是利用了电容的充放电特性以及能够保持电荷的能力。一个 1bit 的存储单元的结构如下图所示,它主要由行列选通三极管,存储电容,刷新放大器组成。行地址与列地址选通使得存储电容与数据线导通,从而可进行放电(读取)与充电(写入)操作。

SDRAM 存储数据是利用了电容能够保持电荷以及其充放电的特性。对于这 1 bit 的的数据,首先需要打开行地址线,然后打开列地址线,选中存储单元。接着打开行选通三极管,再打开列选通三极管,对存储电容进行放电,电容的电平状态就能呈现在位线上,即实现了数据读取。当位线的的电平值送到存储电容上,对存储电容进行充电,就实现了数据写入。刷新放大器的作用是将电容放大,便于传输。

三、SDRAM器件引脚

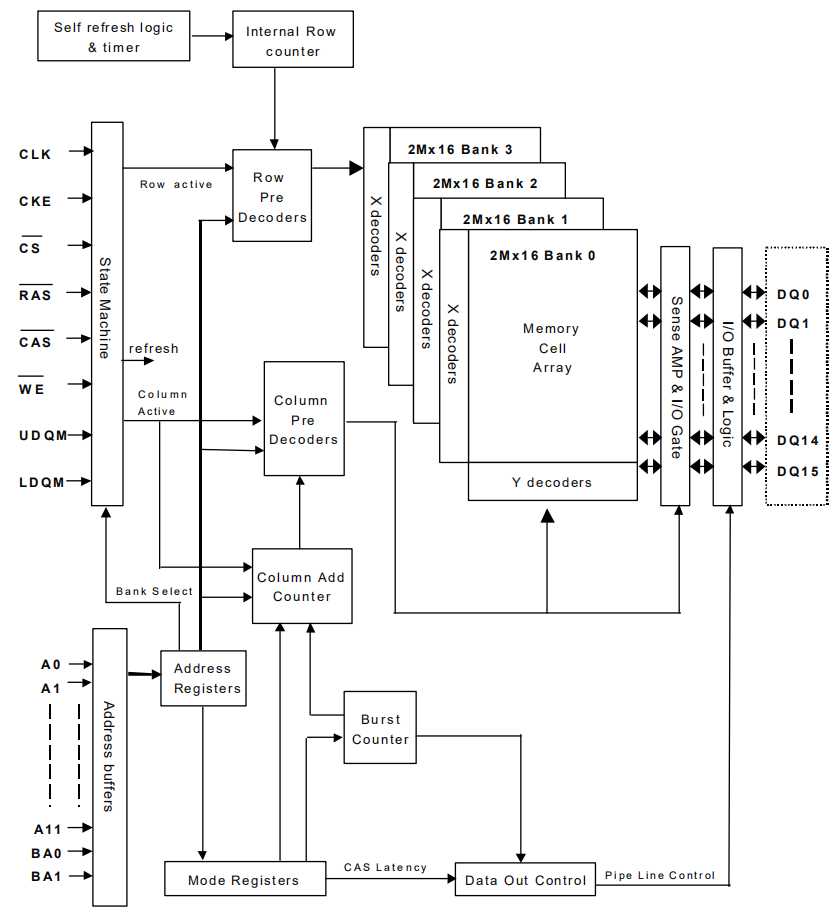

SDRAM 功能框图如下所示:

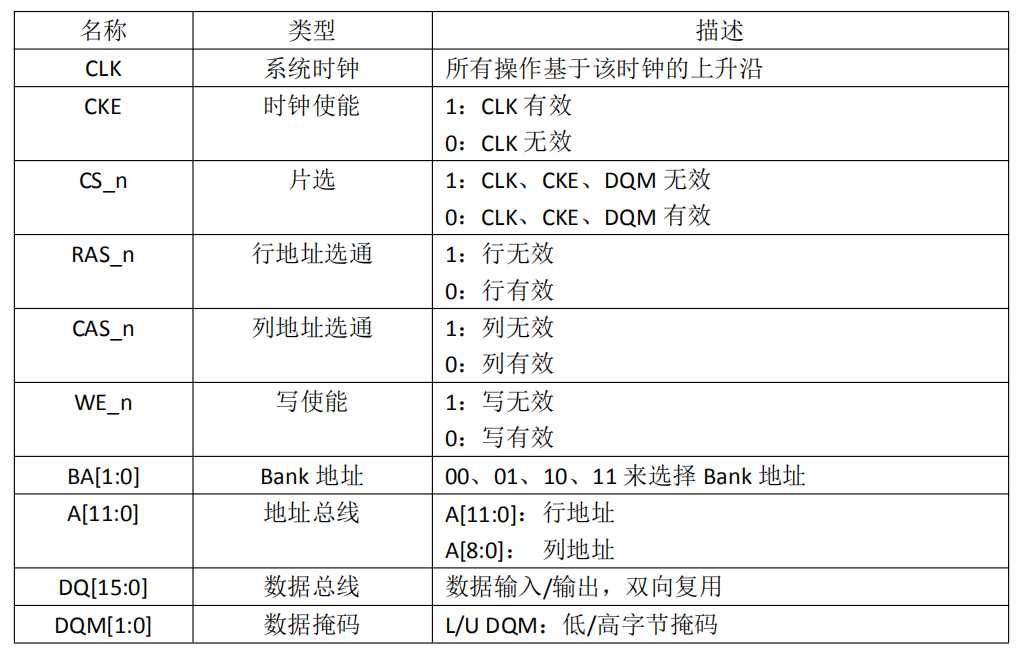

其引脚功能如下表所示:

四、操作命令

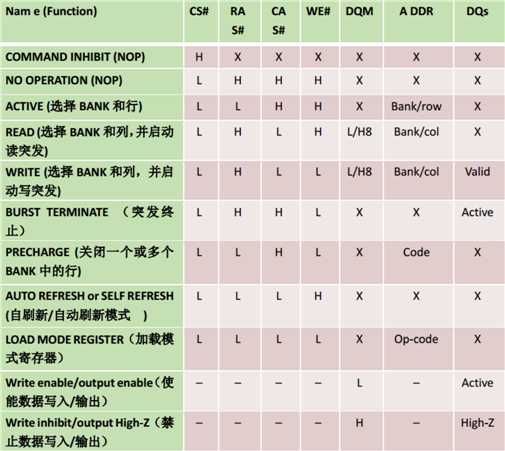

对 SDRAM 的操作是通过命令来控制的,这些命令由 CS_n、RAS_n、CAS_n、WE_n 组合而成。同时,A 和 DQM 作为辅助信号,共同组成 SDRAM 的操作命令。

并非所有命令都会用到,后面用到某些命令时,我们再详细讲解。

参考资料:[1]威三学院FPGA教程

[2]正点原子FPGA教程

[3]袁玉卓, 曾凯锋, 梅雪松. FPGA自学笔记:设计与验证[M]. 北京航空航天出版社, 2017.

SDRAM(1):基本介绍和操作时序

标签:col 过程 不能 延时 放大 丢失 读写 bank ram

原文地址:https://www.cnblogs.com/xianyufpga/p/12232931.html