标签:pre 速度 特性 前端 混合 成本 输入 状态 作用

主要涵盖了设计者在设计模块或者知识产权(Intellectual Preoperty)时所要用到的一些建议。

由单个主时钟和主置位/复位信号驱动设计中所有的时序器件。

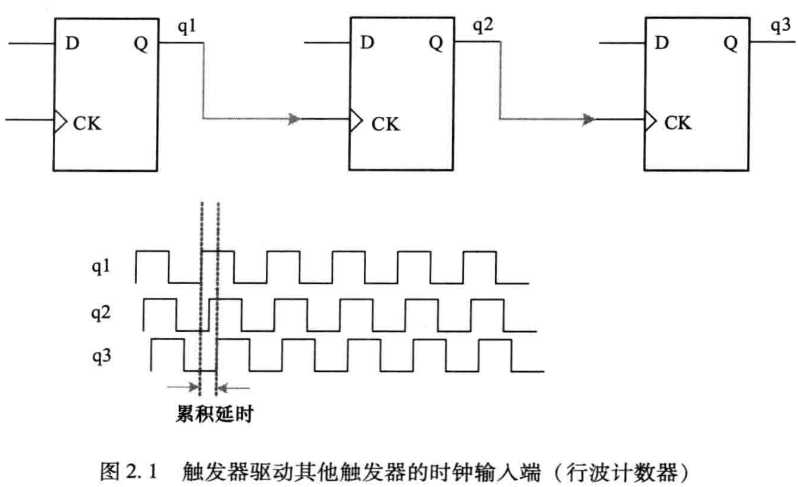

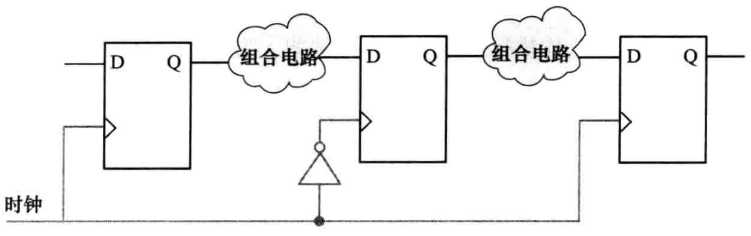

含义:即使用触发器输出作为下一级触发器的时钟输入端

缺点:

优点:能够减少电路的漏电流并降低电路的功耗,在低功耗设计中会取得很好的效果;

前端设计注意:含门控时钟的设计在仿真过程中可能工作正常,但是综合时会出现问题;

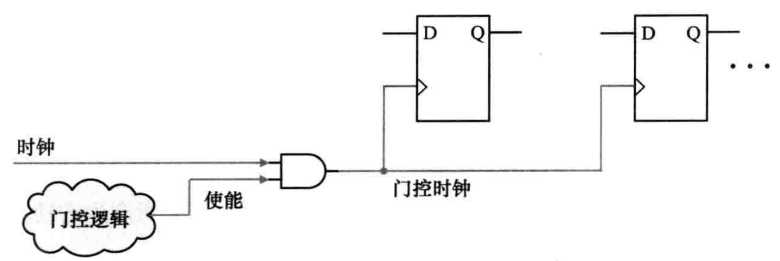

含义:在时钟线上使用门控单元,使用门控逻辑使能信号开关时钟;

优点:能够有效减少功耗,当时钟被门控电路关闭后,门控时钟在根部将时钟关闭,该时钟网络和其中的寄存器都会停止翻转,从而减少功耗;

同步设计中的功耗来源:

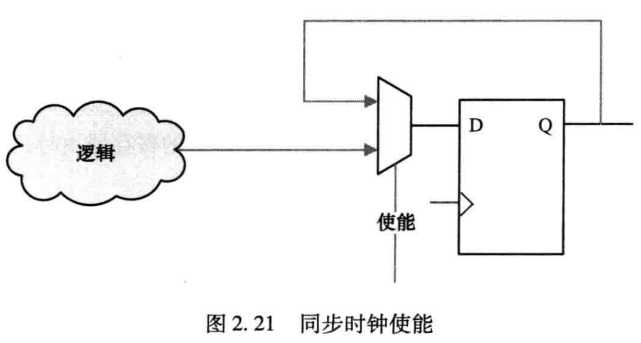

图2.21为同步时钟使能,通过mux可以实现纯同步方式关闭时钟域,使用该方法时钟树始终保持翻转,寄存器内部电路保持活跃,功耗高;

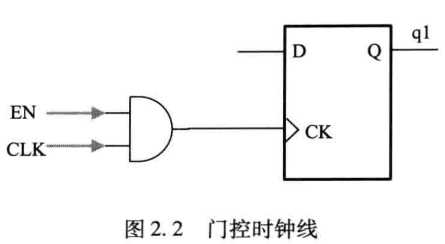

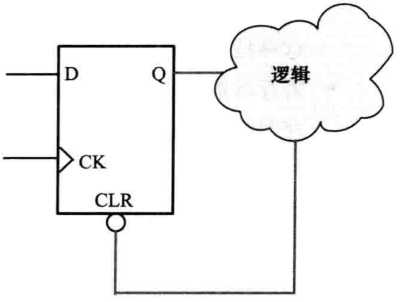

图2.2为门控时钟,使用门控时钟使能能在时钟树根部关闭时钟信号,时钟信号驱动的寄存器由于无时钟输入,保持原来的值,同事还能避免同步时钟设计中输入端的多路选择器,在实现大的寄存器块时节省面积。

缺点:

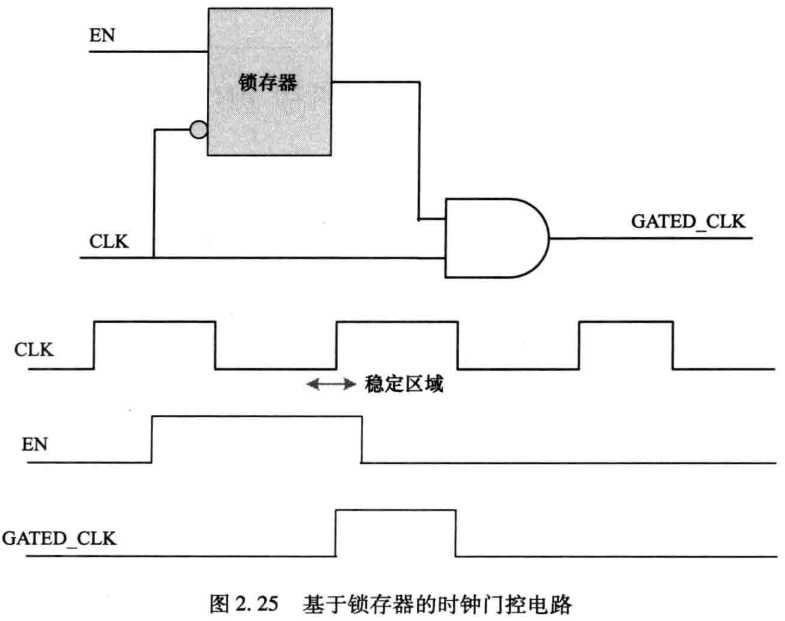

分类:不含锁存器的门控时钟和基于锁存器的门控时钟

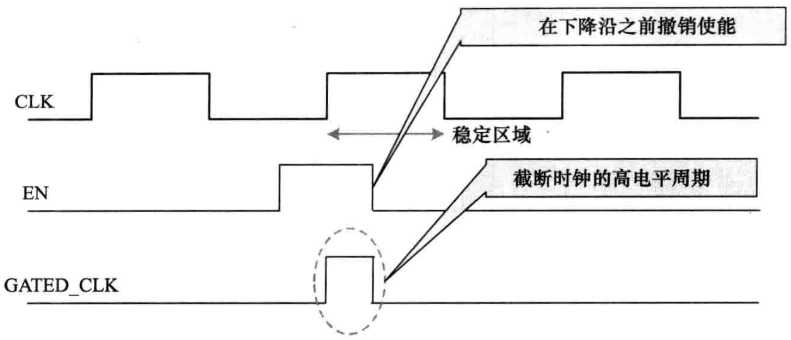

不含锁存器的门控时钟电路:如图2.2,使用and gate 或 or gate实现

要求:使能信号从时钟活跃沿到时钟不活跃沿保持常量(避免过过早阶段时钟脉冲或误产生多个时钟脉冲,即,门控电路输出的时钟频率增加从而导致错误)

基于锁存器的时钟门控电路:通过锁存器来实现使能信号在时钟活跃沿到不活跃沿保持常量的要求;

下降沿为有效沿时,使用正沿触发的锁存器,并使用or gate进行控制;

使用这种电路每次仅需改变门的一个输入就能开关时钟,保证电路输出不包含任何毛刺或尖峰脉冲;

Caution:需要注意时钟占空比和产生使能信号逻辑的延迟。

含义:使用如下图所示的相位相反的时钟信号控制两个触发器,在时钟的上升沿和下降沿都传输数据;

优点:

缺点:

Caution:尽量避免使用双沿时钟,除非对性能/速度要求很高,并无法承受使用等效同步电路在DFT和验证带来的额外开支。

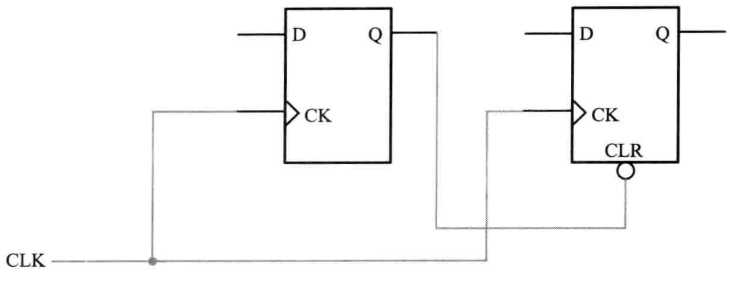

含义:使用第一级触发器的输出作为第二级触发器的复位信号;

缺点:违反同步设计原理,还为导致第二级触发器时钟信号与复位信号产生潜在的竞争关系;

含义:组合环路中的信号之间存在直接反馈回路,反馈回路中不包含寄存器,

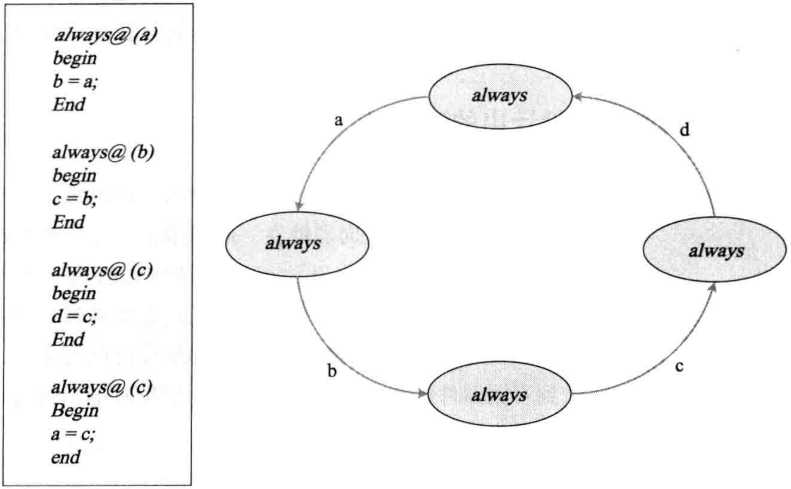

如下图,always块之间存在直接相连,a信号通过d信号与自身直接相连;

缺点:组合环路的行为与所有逻辑的传播延迟相关,而传播延迟会根据条件的变化而发生改变,从而导致电路行为的变化;

解决方法:改变其中某个信号的生成方式,以消除信号之间的依赖性;

Caution:组合环路不可综合

延迟链:使用多个带有单扇入和单扇出的连续节点产生延迟(通常使用多个反相器链增加延迟),通常出现在异步设计中,有时用于解决其他组合逻辑导致的竞争条件。

问题:会增加设计对操作环境的敏感性,降低设计的可靠度,增加将设计移植到不同器件结构上的难度。

方法:在设计中使用同步技术取代异步技术。

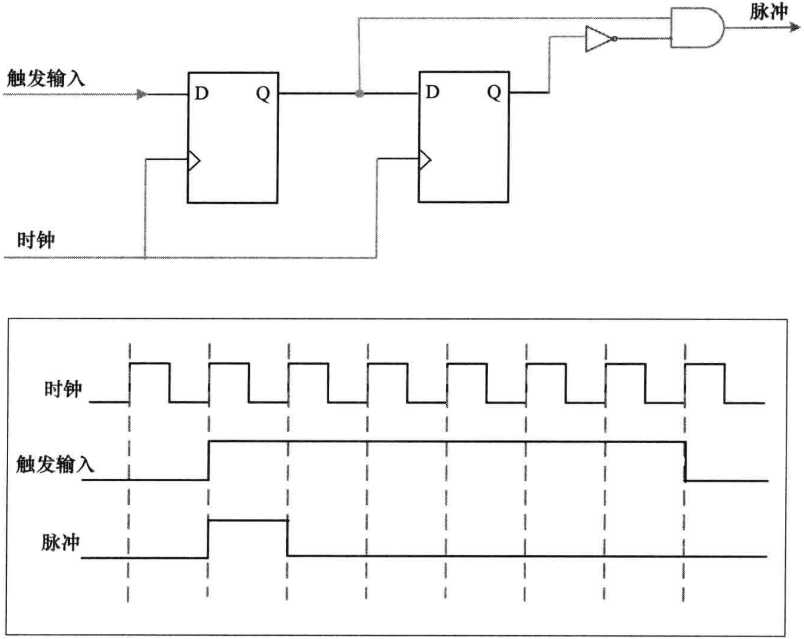

脉冲类型:单个脉冲(脉冲产生器) & 一系列脉冲(多振子):

Caution:上述方法为纯异步,尽可能避免;

问题:

解决方法:

使用如下图的同步脉冲产生器,产生的脉冲宽度与时钟周期宽度相同,宽度可预测,可以使用时序分析进行验证,独立于具体工艺易于移植。

标签:pre 速度 特性 前端 混合 成本 输入 状态 作用

原文地址:https://www.cnblogs.com/lizhiqing/p/12230629.html