标签:常见 参考 sim pos 那些事 电源 保险 avd str

OV5640 是一款还不错的摄像头,现在来记录一下它的开发过程。

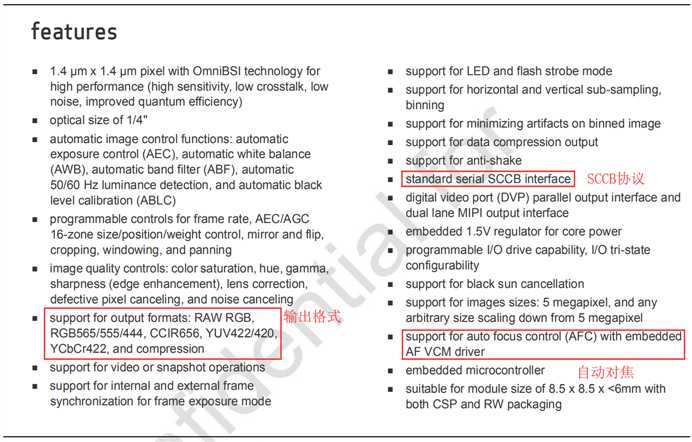

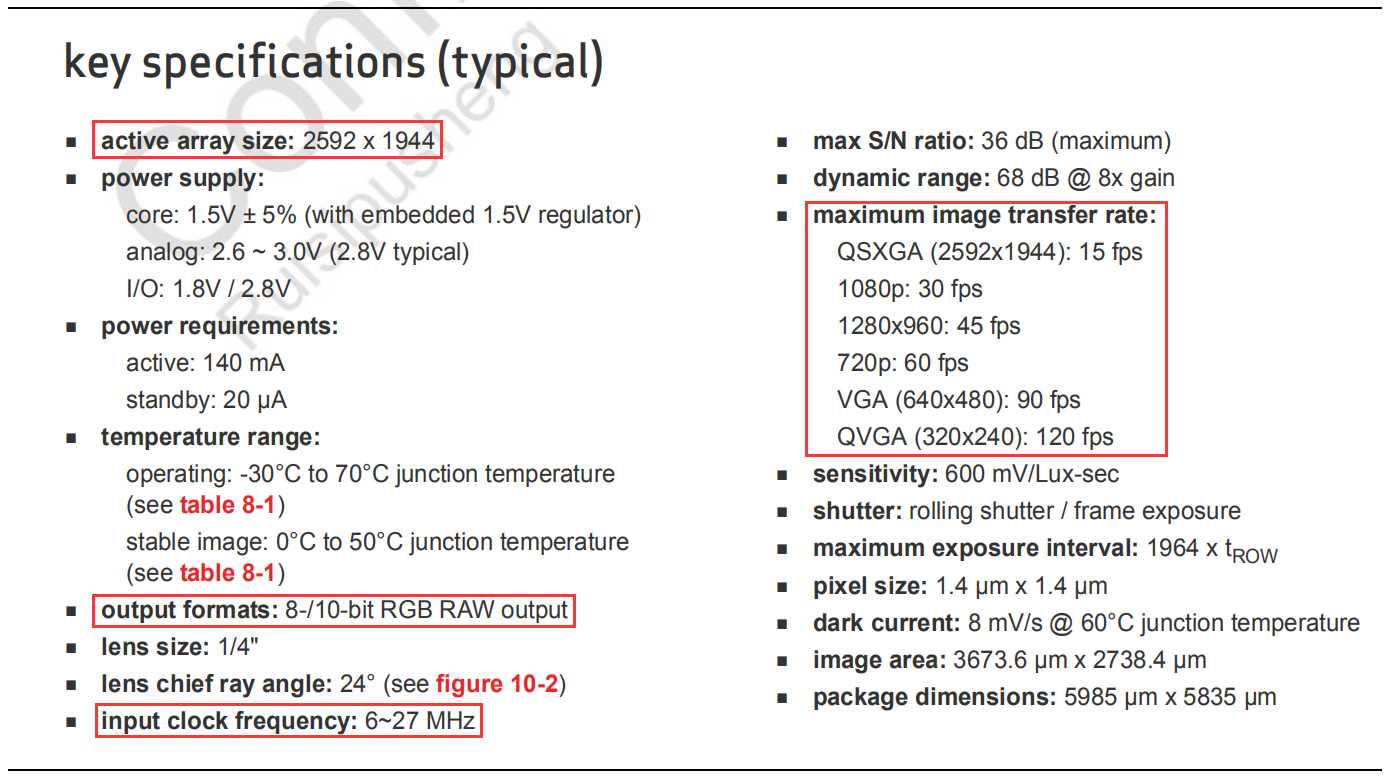

一、OV5640性能概况

打开它的数据手册,可以看到如下几个信息。

OV5640和其他常见的OV7725、OV7670比,其分辨率更高,此外支持自动对焦功能。

二、结构和引脚

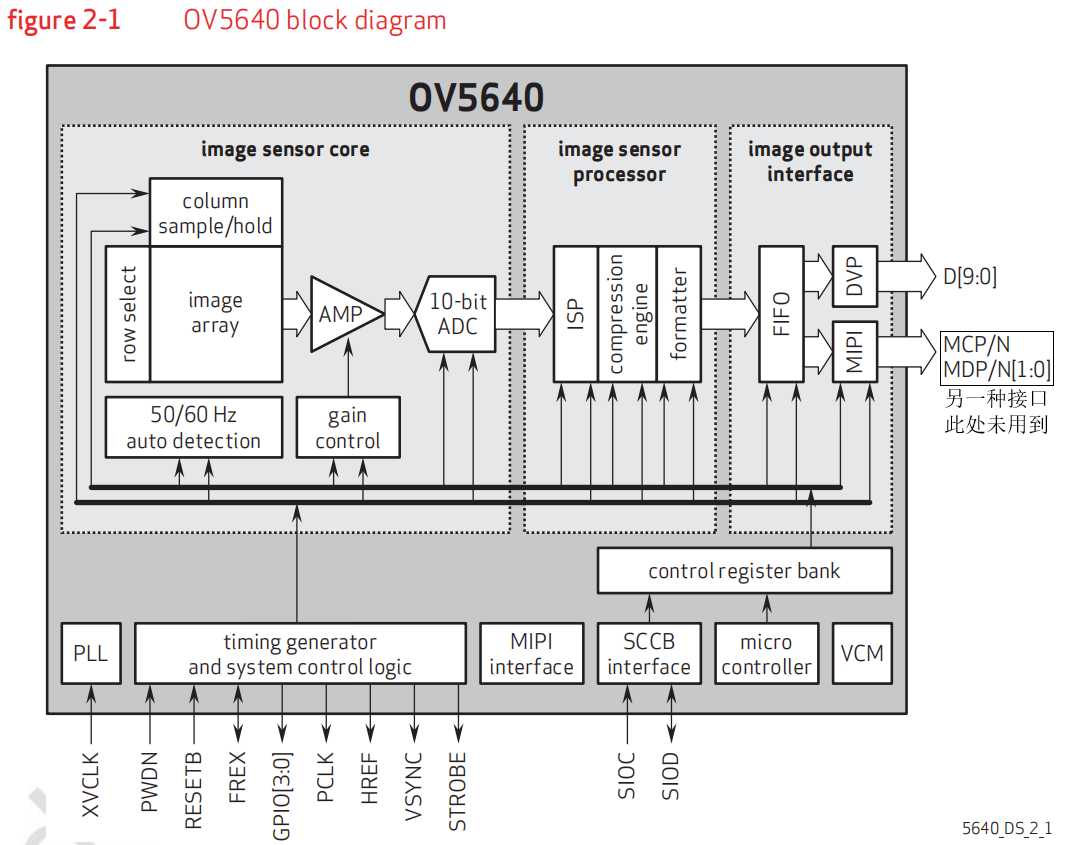

1、结构

OV5640内部结构如下所示。注意 MCP/N MDP/N 接口是其他设备使用的,此次设计我们只使用 D[9:0]即可。有些 OV5640 模块支持 10bit 的数据端口(D9~D0),有些只支持 8bit 的数据端口(D7~D0),是因为其只取了(D9~D2),即舍掉了 D1~D0 这低 2 位的数据端口。

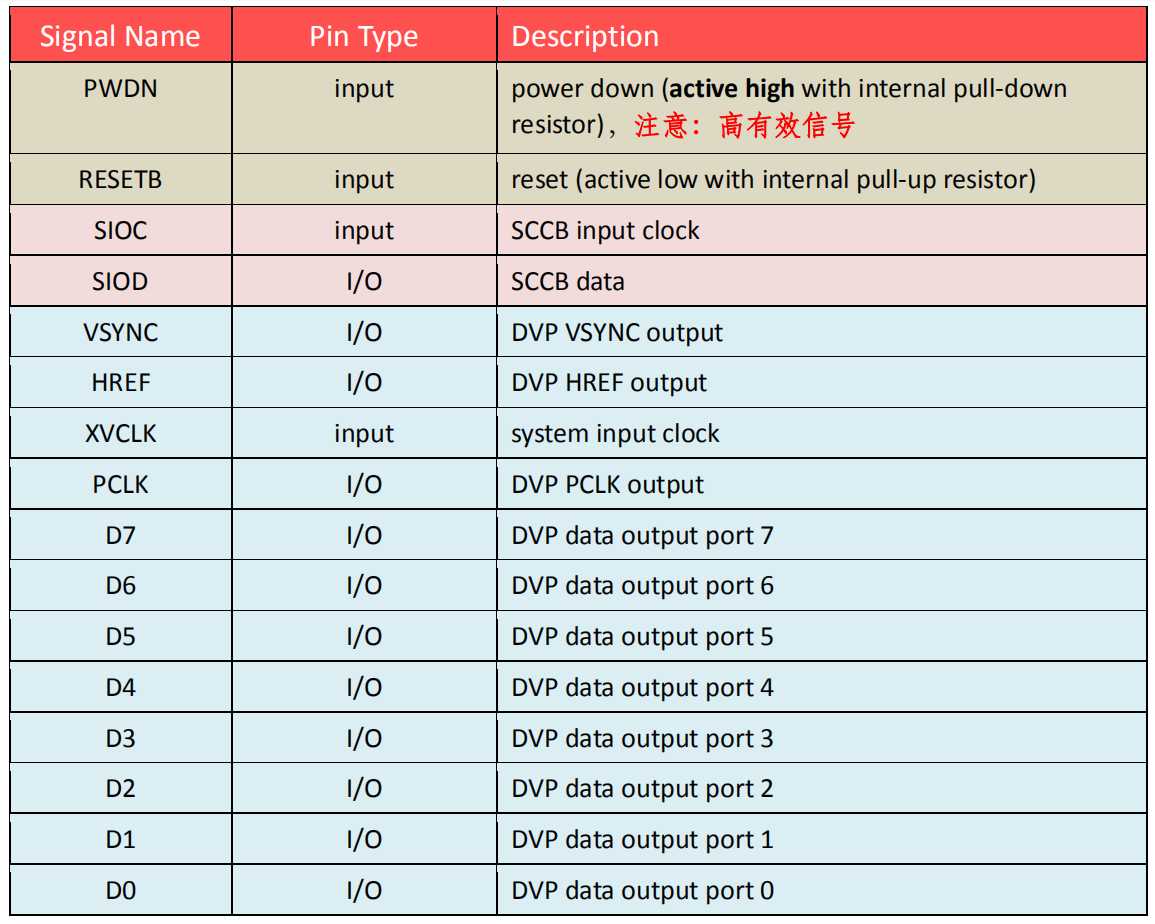

2、引脚

OV5640有很多的引脚,但我们只需要关心外部引出来的,用于编程的部分。如下所示:

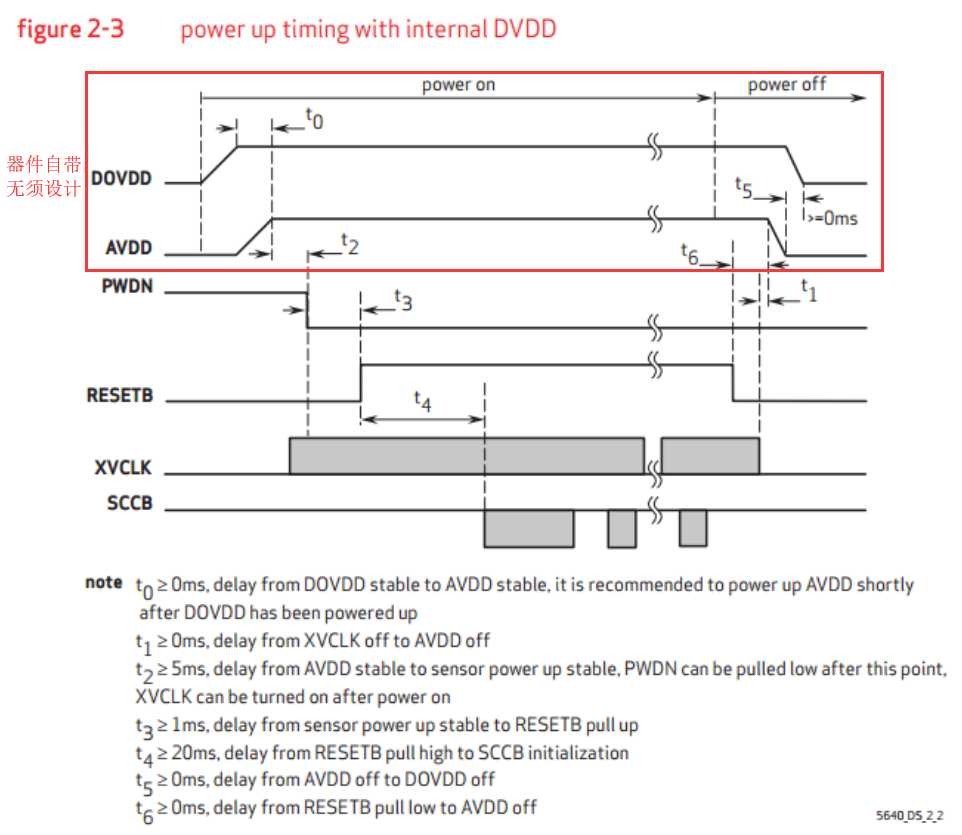

三、上电配置时序分析

OV5640不是说接通电源就直接工作,而是有一段上电时序的,如下所示:

注意 DOVDD 和 AVDD 是 OV5640 器件内部就已经设计好的,不用自己设计。

四、上电控制代码编写

这部分代码编写实在简单,不需要自行设计时序,直接照着上面数据手册的时序图设计即可。为了保险点,时间上都比时序图上标的时间多了1ms。

1 module power_ctrl 2 //========================< 端口 >========================================== 3 ( 4 //system -------------------------------------------- 5 input wire clk , // 50MHz 6 input wire rst_n , 7 //ov5640 -------------------------------------------- 8 output wire ov5640_pwdn , // ov5640上电 9 output wire ov5640_rst_n , // ov5640复位 10 output wire power_done // power_ctrl全面有效,SCCB可以开始工作 11 ); 12 //========================< 参数 >========================================== 13 localparam T2_6MS = 30_0000 ; // T2>5ms 14 localparam T3_2MS = 10_0000 ; // T3>1ms 15 localparam T4_21MS = 105_0000 ; // T4>20ms 16 //========================< 信号 >========================================== 17 reg [18:0] cnt_6ms ; 18 reg [16:0] cnt_2ms ; 19 reg [20:0] cnt_21ms ; 20 21 //========================================================================== 22 //== ov5640_pwdn 23 //========================================================================== 24 always @(posedge clk or negedge rst_n) begin 25 if(!rst_n) begin 26 cnt_6ms <= ‘d0; 27 end 28 else if(ov5640_pwdn == 1‘b1) begin 29 cnt_6ms <= cnt_6ms + 1‘b1; 30 end 31 end 32 33 assign ov5640_pwdn = (cnt_6ms >= T2_6MS) ? 1‘b0 : 1‘b1; 34 35 //========================================================================== 36 //== ov5640_rst_n 37 //========================================================================== 38 always @(posedge clk or negedge rst_n) begin 39 if(!rst_n) begin 40 cnt_2ms <= ‘d0; 41 end 42 else if(ov5640_rst_n == 1‘b0 && ov5640_pwdn == 1‘b0) begin 43 cnt_2ms <= cnt_2ms + 1‘b1; 44 end 45 end 46 47 assign ov5640_rst_n = (cnt_2ms >= T3_2MS) ? 1‘b1 : 1‘b0; 48 49 //========================================================================== 50 //== power_done 51 //========================================================================== 52 always @(posedge clk or negedge rst_n) begin 53 if(!rst_n) begin 54 cnt_21ms <= ‘d0; 55 end 56 else if(power_done == 1‘b1) begin 57 cnt_21ms <= cnt_21ms; 58 end 59 else if(ov5640_rst_n == 1‘b1) begin 60 cnt_21ms <= cnt_21ms + 1‘b1; 61 end 62 end 63 64 assign power_done = (cnt_21ms >= T4_21MS) ? 1‘b1 : 1‘b0; 65 66 67 68 endmodule

这段代码出自开源骚客《SDRAM那些事儿》,这里面的计数方式还是我第一次见,感觉就是很简洁且很神奇,值得学习并掌握。

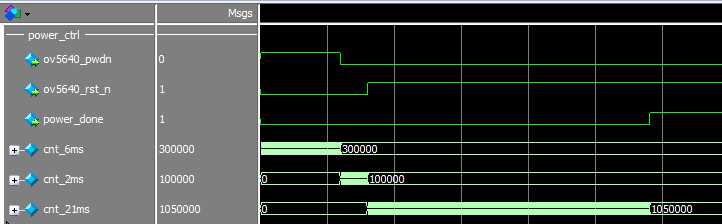

五、仿真验证

仿真部分,直接提供时钟和复位即可,Modelsim 仿真结果如下所示:

仿真结果的时序图和上面数据手册时序图别无二致,此模块设计成功!

参考资料:[1]开源骚客《SDRAM那些事儿》

标签:常见 参考 sim pos 那些事 电源 保险 avd str

原文地址:https://www.cnblogs.com/xianyufpga/p/12267675.html