标签:完整 html 完整性 缓冲区 其他 管线 实现 寻址 包含

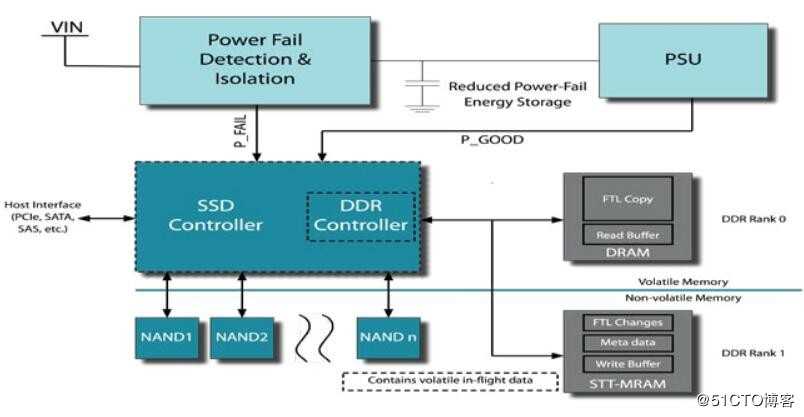

作为克服现有基于NAND闪存的SSD的解决方案,everspin提供具有ST-DDR3和ST-DDR4接口的STT-MRAM,可通过提供高速非易失性存储来提高SSD的系统性能和可靠性。机上数据。通过添加STT-MRAM来补充或替换SSD控制器的DDR总线上的易失性DRAM(图1),SSD控制器现在可以将该高速非易失性存储器用于写缓冲区和之前运行的任何其他关键数据易挥发的。

图1具有电源故障保护功能的混合DDR / STT-MRAM SSD架构

对于企业级固态硬盘,电源管理系统的设计很重要。系统必须检测电源故障,将驱动器与主机隔离,并用足够的能量存储来支撑驱动器,以允许将任何运行中的数据提交到非易失性存储器中,以确保数据完整性。完成此操作所需的保持能量与飞行中的数据量,非易失性存储器的速度和系统的功耗成正比。可以将这种保持能量存储提供的时间量视为电源故障窗口或在耗尽保持能量之前可用于存储不受保护的数据的时间。

为了支持由不同等级的不同内存类型组成的异构DDR架构,理想情况下,SSD控制器中包含的DDR控制器需要支持处理STT-MRAM的不同时序和寻址要求,以实现最佳性能。 SSD控制器还必须采用其他逻辑来正确管理DDR控制器缓冲区中正在传输的少量常驻数据,以确保在断电之前将管线刷新到STT-MRAM并关闭STT-MRAM中的所有打开页面。

标签:完整 html 完整性 缓冲区 其他 管线 实现 寻址 包含

原文地址:https://blog.51cto.com/14618340/2469948