标签:pos 工程 des 窗口 技术 ilog png 单击 remove

本文基于 Altera 官方原版文档《SignalTap II with Verilog Designs》改编而成,原文可在百度文库中下载:https://wenku.baidu.com/view/3931a1edaeaad1f346933fe3.html?from=search

一、Verilog案例

我们将使用下面 Verilog 中实现的 key 按键控制 led 灯的电路,此电路将开发板(小梅哥AC620开发板)上的前2个 key 按键连接到板上的前2个led灯上。工作原理:在时钟(clk)的上升沿读取 key 按键的值,赋给 led灯的对应寄存器。

module test ( input clk, input [1:0] key, output reg [1:0] led ); always @(posedge clk) begin led[1:0] <= key[1:0]; end endmodule

建工程、添引脚等都会了,就不记录了。

二、SignalTap II 的使用

1、编译工程,生成 .sof 文件。

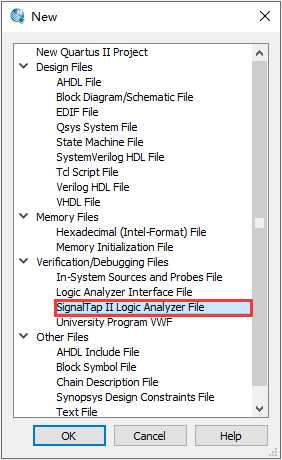

2、选择 File > New 打开 SignalTap II 窗口,选择 SignalTapII Logic Analyzer File 并单击OK。

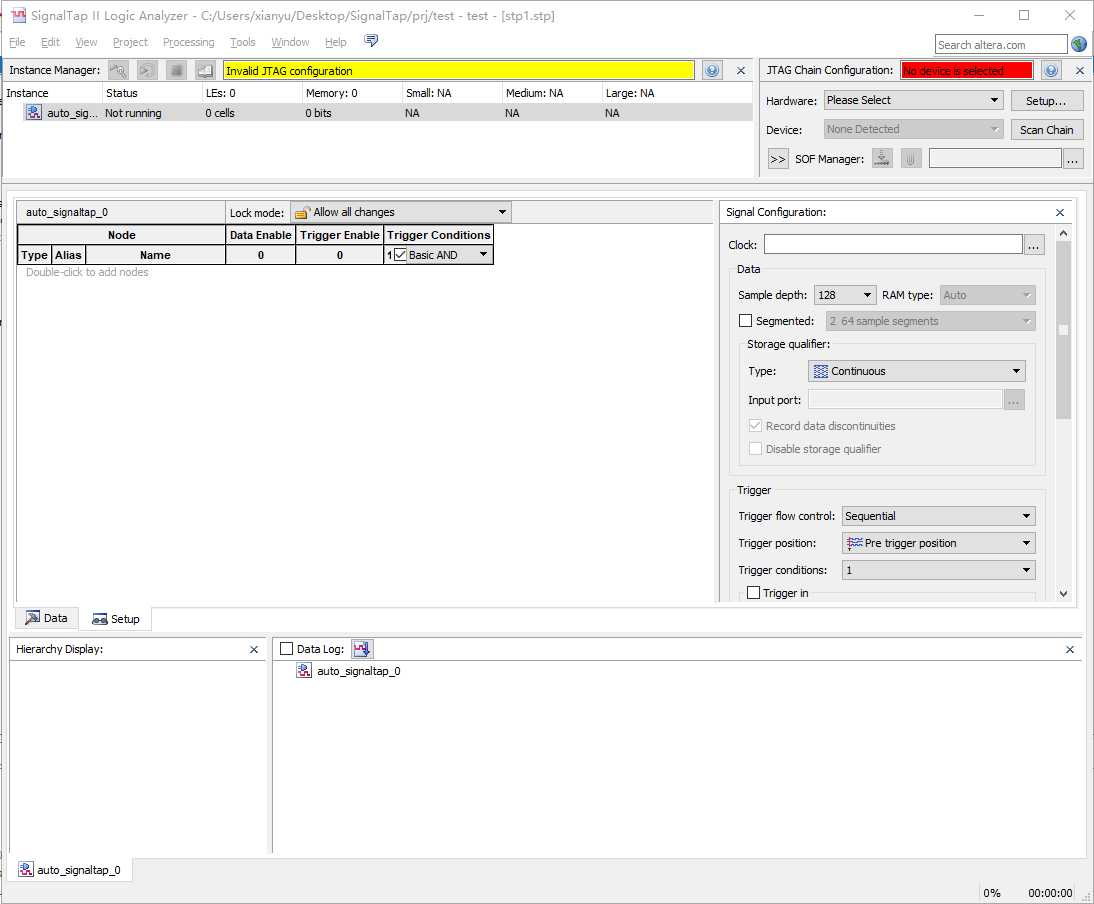

3、SignalTap II界面如下图所示,保存文件并命名为 test.stp,接下来弹出的两个对话框分别点击 OK 和 Yes。

九、补充:

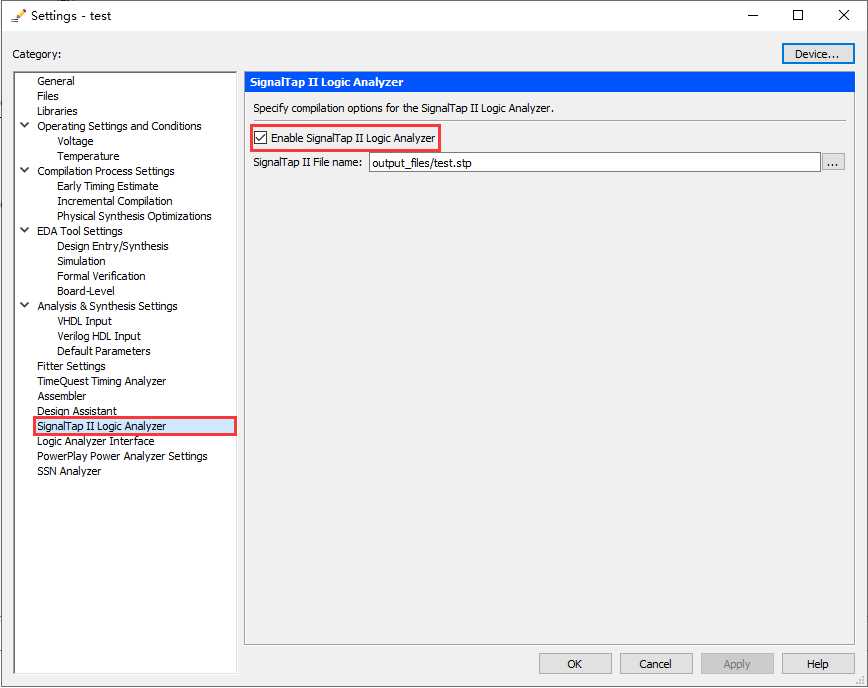

1、去除 Signaltap II

方法1:在Quartus II界面中选择 Assignments > Settings > SignalTap II Logic Analyzer,把 Enable SignalTap II Logic Analyzer前面的勾去掉。

方法2:在 Quartus II 界面的 Files 点击 .stp 右键选择 Remove File from Project。

标签:pos 工程 des 窗口 技术 ilog png 单击 remove

原文地址:https://www.cnblogs.com/xianyufpga/p/12323021.html