标签:否则 系统 idt 时序 状态 根据 and ilo str

时序逻辑对于数字电路设计十分重要,本文针对数字电路中的时序逻辑部分进行了系统的回顾。

由于时序逻辑的输出不但受当前输入影响,还受之前的输入的影响,所以需要有存储单元对以前的输入进行存储。

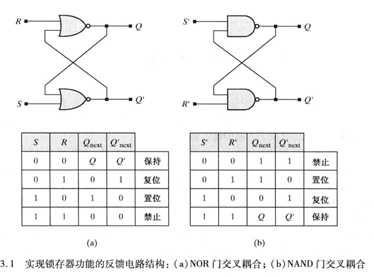

SR锁存器(set-reset)---电平敏感器件

实际在Verilog中,很多情况应该避免使用锁存器,也应该避免无意中被综合成锁存器。

NOR门交叉耦合的锁存器,一方面输入11时,输出逻辑不是互反的;另一方面逻辑从11->00引发竞争,会导致输出无法预测所以避免11;

NAND门交叉耦合的苏存取,输入00时,输出逻辑不是互反的,而且从00->11引发竞争,所以避免00。

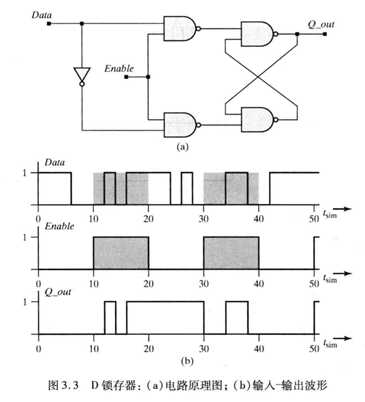

透明锁存器

透明锁存器也成为D锁存器,通过增加一级带使能的与非门电路,实现了输入是否影响到输出的控制。

D锁存器输入反向后连接到另一端,避免了禁止的输入和不稳定的输出

边沿敏感器件,数据的动作通过某个信号的边沿进行同步。

D触发器

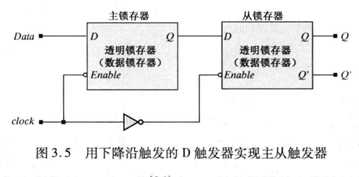

主从触发器

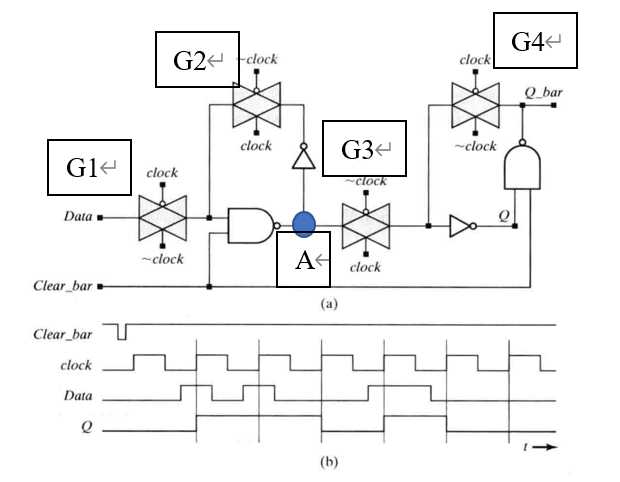

可通过两个透明锁存器实现。当clock变为低电平时,Data通过主锁存器到达Q1;clock由低电平变为高电平时,主锁存器锁存,Data通过从锁存器到达输出。

主从触发器还可以通过CMOS工艺中的传输门(TG Gate)实现

分析:

1、清零状态,A点为1,Q_bar为1,Q为0

2、Clock低电平时,G1开,G2关,G3关,G4开,Data信号输入到主锁存器输入端。Clock上升沿来临,G1关,G2开实现触发和锁存。

3、G2开的同时G3开,A点信号穿过G3,取反后到达Q;G4实现输出锁存。

其他触发器

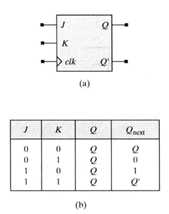

JK触发器,00保持,11翻转,10置数,01清零。

T触发器,将JK触发器的JK端连接在一起,实现输入0保持,输入1翻转。

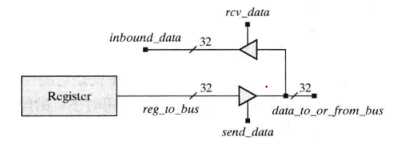

总线:连接系统中多个功能单元多条连线的信号通道。大大减小系统物理资源和板级空间。

三态器件:硬件上实现了总线和电路中的动态接口,使能时作为数据通路,否则开路(Hi-Z)。

三态器件用于电路与总线隔离,如图。send_data为高时,电路向总线输出数据;rcv_data为高时,从总线接收数据。

时序机

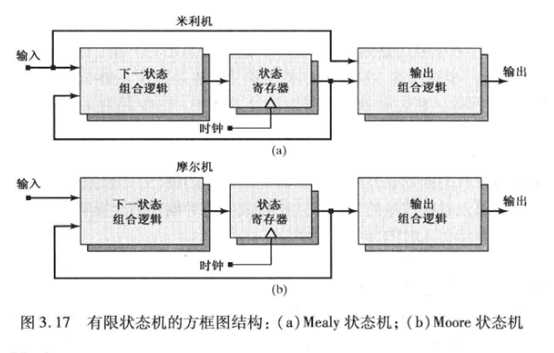

时序机的下一步行为或动作由当前输入和当前状态描述。

Mealy状态机下一状态取决于当前输入和当前状态。

Moore状态机下一状态取决于当前输入和当前状态,但输出仅取决与当前状态。

比较

1、Moore机比Mealy机多出一个延迟周期(Mealy机能够对输入进行实时监测),但输入信号的噪声可能对输出的信号产生一定影响。

2、一般来说,Moore型状态机状态多一些。

状态转移图(个人觉得这一部分很关键,但自己也没有十分掌握好,后面通过理解加深逐渐来补充这部分内容吧)

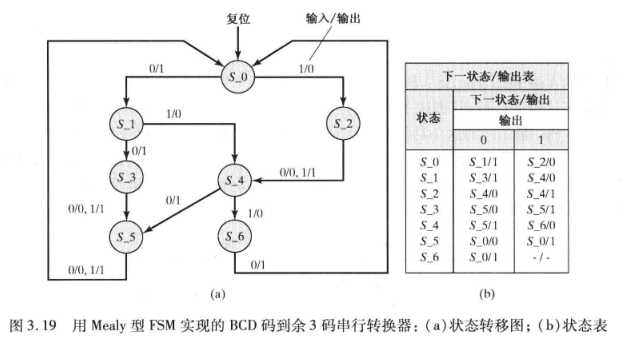

这里以一个例子来说明手工方法来设计状态机的步骤:

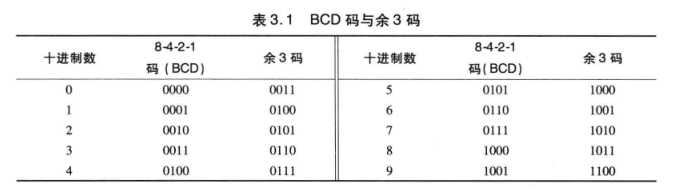

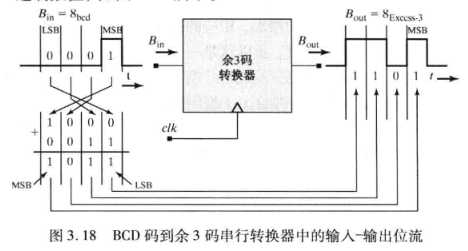

例:BCD码到余3码的转换(余3码是在BCD码的基础上加3,得到的自补码)

在设计时需要注意的是,位流先从最低位输入和输出。

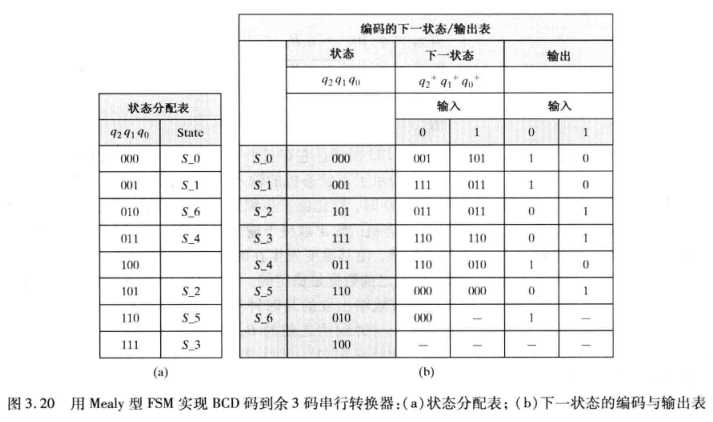

根据表得到状态转移图(这部分自己做的也不够好)。需要列出状态和状态转移关系,合并等价状态,根据以下原则分配对应码字代表状态。

状态编码分配原则:

1、 某个特定的输入,两个状态跳到同一个状态,则分配相邻码字

2、 相邻状态分配相邻码字

3、 某个特定输入,有相同的输出,分配相邻码字

根据状态转移图并分配状态后,得到“当前状态-不同输入下下一状态-不同输入下输出”的表格。

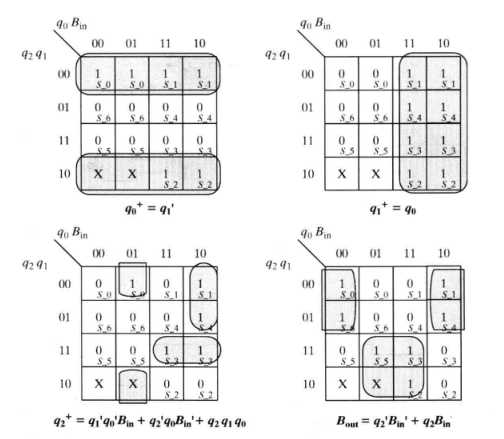

根据上表,分别画出“下q2q1q0Bout的下一状态-q2q1q0qin的当前状态”卡诺图,得到q2q1q0qin的布尔表达式。

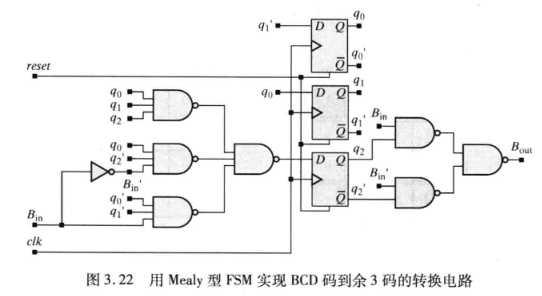

根据卡诺图得到的四个表达式,画出对应的硬件实现。利用三个触发器,分别存储三个状态位。其余利用组合逻辑实现。

状态化简和等价状态

等价状态:时序机两个状态对所有可能的输入都有相同的输出和下一状态(即状态表两个状态有关的行是完全相同的),则称为两个状态等价。

删除并保留仅一个等价状态可使得状态转移图得到化简。但两个状态行不完全相同也可能是等价状态(即需要某些等价消除后才能看出该两个状态行等价)。

本文介绍了数字电路中时序逻辑部分的基础内容,但很大一部分仍需要练习和补充。如果有看客发现错误希望大家能够指出,大家共同进步!

标签:否则 系统 idt 时序 状态 根据 and ilo str

原文地址:https://www.cnblogs.com/wt2110/p/12408625.html