标签:ilo col lock ble 合并 info width display strong

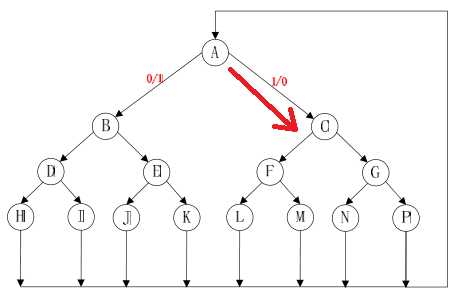

接着上节8421BCD转余3码Verilog HDL的设计(1),分析另一条路径A-C分支

(1)在C状态,t1时刻Bin输入的值可能为0或者1:当bin输入0时,进入F状态;当bin输入1时,进入G状态,比特流Bin二进制为t3t2t1t0的可能性如下:

|

C状态(t1时刻,Bin=0),Bout=0 |

C状态(t1时刻,Bin=1),Bout=1 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一状态为F状态 | t3t2t1t0 | T3T2T1T0 | 下一状态为G状态 |

| 0001 | 0100 | 0011 | 0110 | ||

| 0101 | 1000 | 0111 | 1010 | ||

| 1001 | 1100 | 1011 | 1110 | ||

| 1101 | (1)0000 | 1111 | (1)010 | ||

(2)在F状态,t2时刻Bin输入的值可能为0或者1:当bin输入0时,进入L状态;当bin输入1时,进入M状态,比特流Bin二进制为t3t2t1t0的可能性如下:

|

F状态(t2时刻,Bin=0),Bout=1 |

F状态(t2时刻,Bin=1),Bout=0 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一状态为L状态 | t3t2t1t0 | T3T2T1T0 | 下一状态为M状态 |

| 0001 | 0100 | 0101 | 1000 | ||

| 1001 | 1100 | 1101 | (1)0000 | ||

(3)在L状态,t3时刻Bin输入的值可能为0或者1:当bin输入0时,进入A状态;当bin输入1时,进入A状态,比特流Bin二进制为t3t2t1t0的可能性如下:

|

L状态(t3时刻,Bin=0),Bout=0 |

L状态(t3时刻,Bin=1),Bout=1 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一状态为A状态 | t3t2t1t0 | T3T2T1T0 | 下一状态为A状态 |

| 0001 | 0100 | 1001 | 1100 | ||

(4)在M状态,t3时刻Bin输入的值可能为0或者1:当bin输入0时,进入A状态;当bin输入1时,进入A状态,比特流Bin二进制为t3t2t1t0的可能性如下:

|

M状态(t3时刻,Bin=0),Bout=1 |

M状态(t1时刻,Bin=3),Bout=0 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一状态为A状态 | t3t2t1t0 | T3T2T1T0 | 下一状态为A状态 |

| 0101 | 1000 | 1101 | (1)0000 | ||

(5)在G状态,t2时刻Bin输入的值可能为0或者1:当bin输入0时,进入N状态;当bin输入1时,进入P状态,比特流Bin二进制为t3t2t1t0的可能性如下:

|

G状态(t2时刻,Bin=0),Bout=1 |

G状态(t2时刻,Bin=1),Bout=0 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一状态为N状态 | t3t2t1t0 | T3T2T1T0 | 下一状态为P状态 |

| 0011 | 0110 | 0111 | 1010 | ||

| 1011 | 1110 | 1111 | (1)0010 | ||

(6)在N状态,t3时刻Bin输入的值可能为0或者1:当bin输入0时,进入A状态;当bin输入1时,进入A状态,比特流Bin二进制为t3t2t1t0的可能性如下:

|

N状态(t3时刻,Bin=0),Bout=0 |

N状态(t3时刻,Bin=1),Bout=1 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一状态为A状态 | t3t2t1t0 | T3T2T1T0 | 下一状态为A状态 |

| 0011 | 0110 | 1011 | 1110 | ||

(7)在P状态,t3时刻Bin输入的值可能为0或者1:当bin输入0时,进入A状态;当bin输入1时,进入A状态,比特流Bin二进制为t3t2t1t0的可能性如下:

|

P状态(t3时刻,Bin=0),Bout=1 |

P状态(t3时刻,Bin=1),Bout=0 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一状态为A状态 | t3t2t1t0 | T3T2T1T0 | 下一状态为A状态 |

| 0111 | 1010 | 1111 | (1)0010 | ||

综上,整理得到状态转换表如下:

| 状态转移 | 输入0 | 输入1 | 输入0 | 输入1 |

| 当前状态 | 下一个状态 | 输出Bout | ||

| A | B | C | 1 | 0 |

| B | D | E | 1 | 0 |

| C | F | G | 0 | 1 |

| D | H | I | 0 | 1 |

| E | J | K | 1 | 0 |

| F | L | M | 1 | 0 |

| G | N | P | 1 | 0 |

| H | A | A | 0 | 1 |

| I | A | A | 0 | 1 |

| J | A | A | 0 | 1 |

| K | A | A | 1 | 0 |

| L | A | A | 0 | 1 |

| M | A | A | 1 | 0 |

| N | A | A | 0 | 1 |

| P | A | A | 1 | 0 |

(1)H、I、J、L完全等价,保留H,合并I、J、L状态

| 状态转移 | 输入0 | 输入1 | 输入0 | 输入1 |

| 当前状态 | 下一个状态 | 输出Bout | ||

| A | B | C | 1 | 0 |

| B | D | E | 1 | 0 |

| C | F | G | 0 | 1 |

| D | H | H | 0 | 1 |

| E | H | K | 1 | 0 |

| F | H | M | 1 | 0 |

| G | N | P | 1 | 0 |

| H | A | A | 0 | 1 |

| K | A | A | 1 | 0 |

| M | A | A | 1 | 0 |

| N | A | A | 0 | 1 |

| P | A | A | 1 | 0 |

(2)K\M\P状态完全一样,合并M\P,保留K状态

| 状态转移 | 输入0 | 输入1 | 输入0 | 输入1 |

| 当前状态 | 下一个状态 | 输出Bout | ||

| A | B | C | 1 | 0 |

| B | D | E | 1 | 0 |

| C | F | G | 0 | 1 |

| D | H | H | 0 | 1 |

| E | H | K | 1 | 0 |

| F | H | K | 1 | 0 |

| G | N | K | 1 | 0 |

| H | A | A | 0 | 1 |

| K | A | A | 1 | 0 |

| N | A | A | 0 | 1 |

(3)H\N完全一样,合并N,保留H;

| 状态转移 | 输入0 | 输入1 | 输入0 | 输入1 |

| 当前状态 | 下一个状态 | 输出Bout | ||

| A | B | C | 1 | 0 |

| B | D | E | 1 | 0 |

| C | F | G | 0 | 1 |

| D | H | H | 0 | 1 |

| E | H | K | 1 | 0 |

| F | H | K | 1 | 0 |

| G | H | K | 1 | 0 |

| H | A | A | 0 | 1 |

| K | A | A | 1 | 0 |

(4)E/F/G完全一样,合并EFG,保留E

| 状态转移表 | 输入0 | 输入1 | 输入0 | 输入1 |

| 当前状态 | 下一个状态 | 输出Bout | ||

| A | B | C | 1 | 0 |

| B | D | E | 1 | 0 |

| C | E | E | 0 | 1 |

| D | H | H | 0 | 1 |

| E | H | K | 1 | 0 |

| H | A | A | 0 | 1 |

| K | A | A | 1 | 0 |

得到最终的状态转移表。

标签:ilo col lock ble 合并 info width display strong

原文地址:https://www.cnblogs.com/leejiac/p/12432461.html