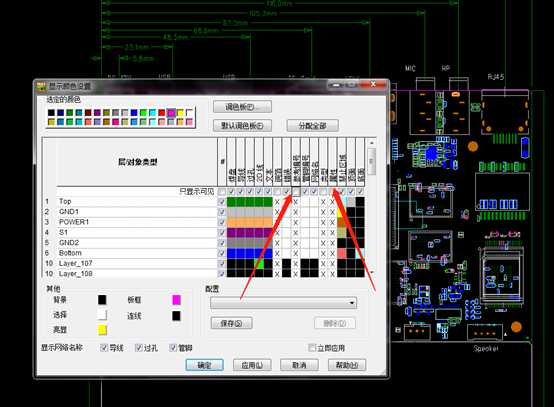

标签:没有 帮助 标示 设置 设定 bottom 如图所示 sign 电路

PADS工作中遇到的问题以及技巧

1.PADS中元器件参考编号、元件类型的设置以及摆放

在很多公司由于文件机密性的原因在进行打板的时候,都会把元器件的属性值一般也就是元器件的value值给隐藏起来不印制在电路板上,甚至是元器件的参考编号

图1

然后在出GERBER的时候,丝印层的设置,将元件编号一栏给去掉即可实现目的。

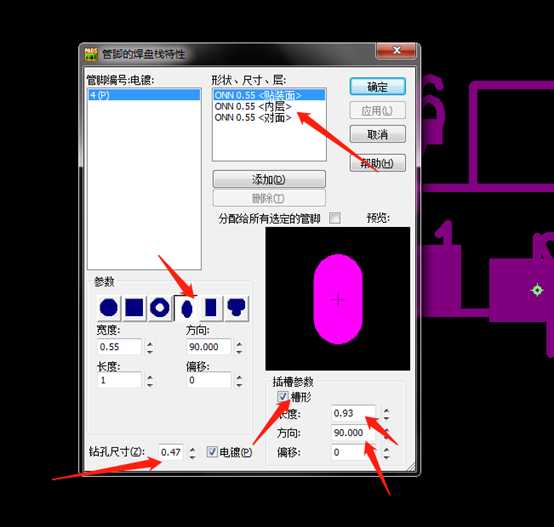

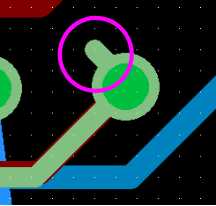

2.PADS中封装的问题,一个槽形焊盘下面有一块正方形的铜皮的焊盘的设置

首先设置出槽形的焊盘端点,如图1

图1

画出一块相应的大小的铜箔,然后进行铜箔和焊盘的关联,如图2

图2

选择端点,右键中选择关联,根据提示“选择要关联的铺铜”,点击铺铜,焊盘便与铜箔成为一体,如图3

图3

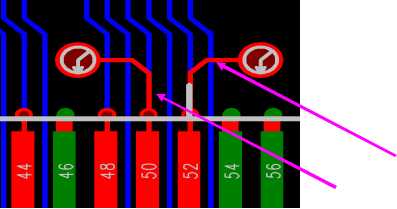

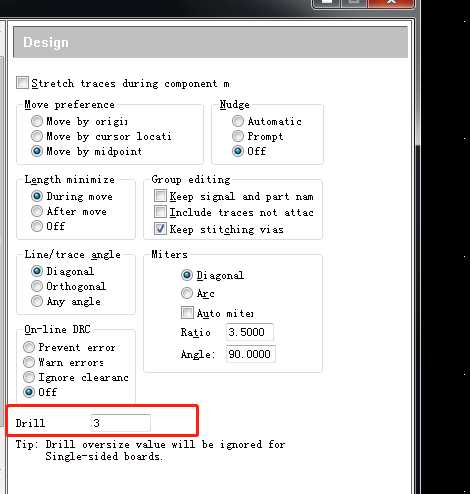

3.PADS中过孔规则与钻孔规则的问题

在平面层中,由于软件的一个BUG问题,电源分割铺铜时出现地过孔的间距特别大,(平面层设置中去掉顶层底层焊盘也没有用的情况下)通过画破铜也是不完整的铜的方式或者是在过孔中的过孔特性中设置去掉平面层焊盘的方式解决此问题,但是新生的问题就是,在平面层去掉过孔焊盘的过孔,软件默认为它就是钻孔,铺铜时按照了预先设定好的钻孔规则进行了铺铜

解决办法:在规则设置中,将钻孔的规则设置为安全间距6mil或者是8mil便解决了铺铜出现安全间距的问题。

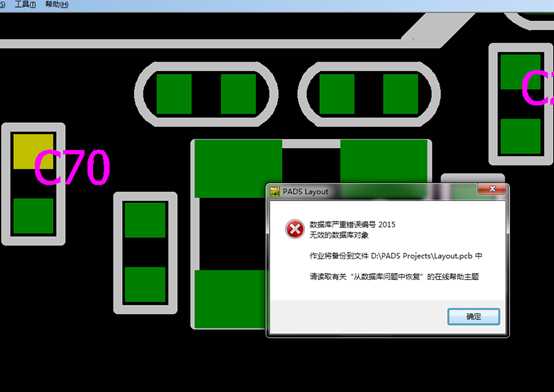

4.PADS出现在选中组合打散时出现选中不了,或者是选中了之后不能显示,右键中有相应的对组合操作的命令,但是选择打散命令时出现不能打散,出现一个报错的对话框的问题时,如图4

图4

弹出对话框并强制性关掉软件的问题。

原因:这是由于PCB文件出现了问题,出现了文件里面的一些组合信息丢失,所以不能完全的选中。

解决办法:

将PCB文件降版本,降低几个版本的ASC文件,再新建一个新的PCB文件,导入降低版本的ASC文件,便会报出文件中组合信息丢失的问题,并且软件默认的修复,修复了的文件便没有这个组合,便可以进行相应的操作。

4. PADS中如何检查STUB线

做为一名优秀的 PCB 设计师,他所设计出来的 PCB 应该是无可挑剔,包括前端的 PCB 布线和后端的 DFM(面向制造的设计,Design for manufacturability);因为设计与制造是产品生命周期中最重要的两个环节,并行工程就是在开始设 计时就要考虑产品的可制造性和可装配性等因素。

此份简明教程将以图文的形式展示如何帮助您快速和准确地进行 DFM 检查和优化 Stub 线。

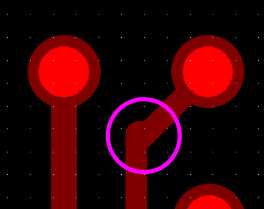

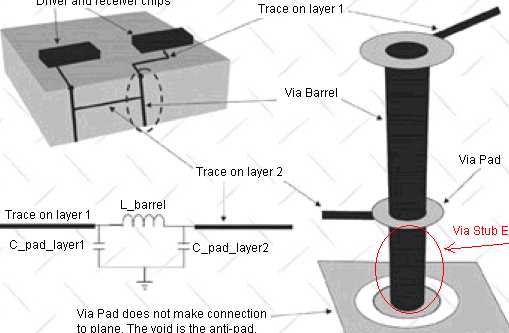

一、何谓 Stub 线

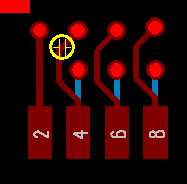

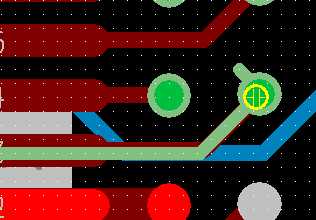

就是俗称的线头或歪线(特别在 Router 中经常出现), 或者说信号没打算经过的路径,如图所示:

但是以下两种情况是可以忽略的:

1, 在添加测试点的时候,为保证测试点的间距,不得不多拉一根线出来。

这种情况,对于 High speed signal 是完全禁止的。因为通过大量的仿真和布线经验,stub 会严重影响高速线的信号质量。

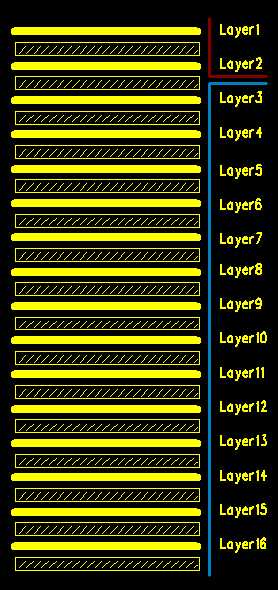

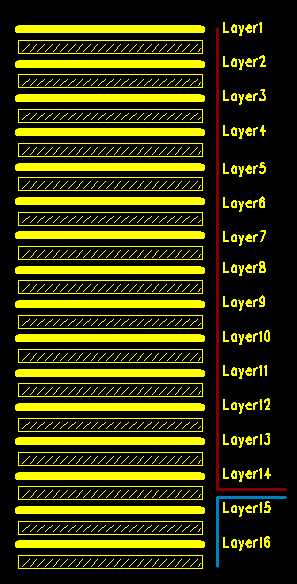

2, 对于 press fit component 而言的,当板厚在 2.1mm 以上时,并且 信号是在上半部分层面进入 press fit component ′s pin 的时候,就产生了 via stub.

比如,一个 16 层板,信号在 Layer3 进入 press fit component ′s pin,则红色路径为信号经过的路径。蓝色路径就是多出来的 Stub。

此种情况也会影响高速线的信号质量的。

方法:一是将蓝色的线切掉,就是要求 PCB 进行背钻处理。上图 背钻从 bottom 钻到lay4,但这会增加很多成本。

二是信号线尽量往下半部分层面如 press fit component ′s pin。

信号对 stub 的长度也是有限制的,这就需要根据信号的速度而定。可通过仿真或直接咨询信号完整性工程师.

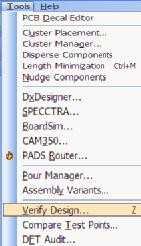

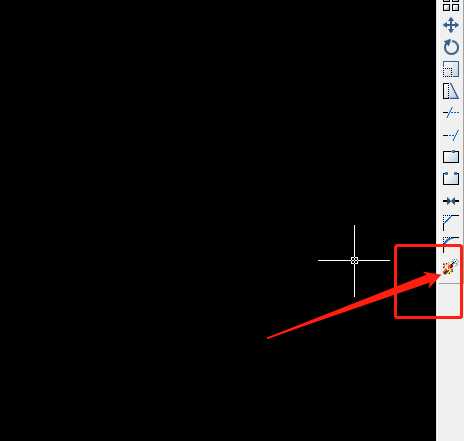

二,Stub 检查

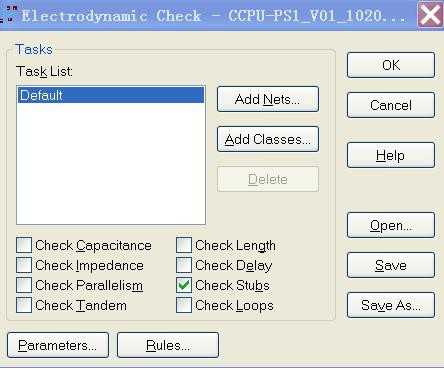

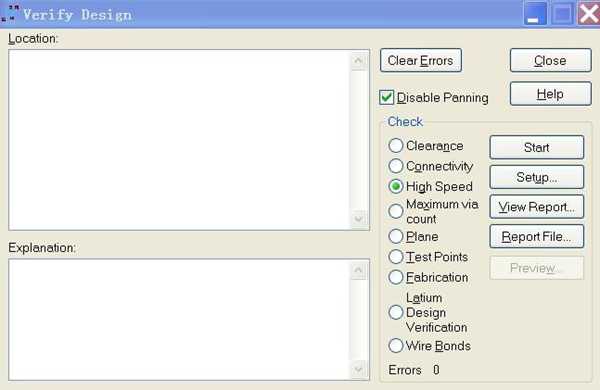

1、执行[Toosl]/[Verify Design],进入设计验证界面.

2、执行[Hign Speed],进入高速设计验证界面.

3、勾选[Check Stubs]/[OK]

4、执行[Start],进行 Stubs 验证。

4,此时,在我们的 PCB 上面,会出现警告标识,我们可根据警告标识进行布线优化.

5.PADS中输出贴片图的时候,元器件一脚的标示为什么不能输出来?(元器件的封装的丝印放置在丝印层的,放置在丝印层的时候便能够输出)

对于结构工程师发给你的结构图怎么一步做到导进PCB中无问题

在后拉板中,共模电感的放置位置

共模电感应该放置在入口处,即后拉板中芯片附近。

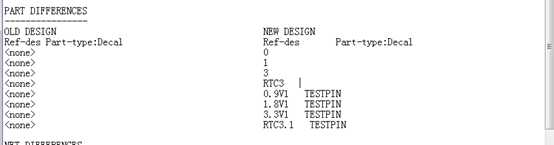

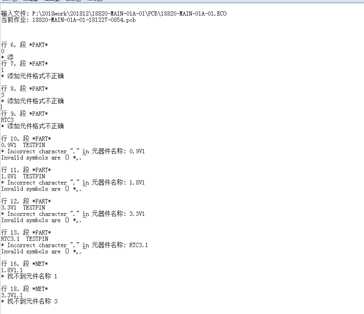

对于PCB中遇到的封装导不进去的原因

原因就是如下

由于我的ASC文件是在ORCAD中绘制的,ORCAD能够识别的字符,但是PADS中不能识别,所以造成了这些测试点导不进去的问题。

解决办法,将测试点重命名

对于pads 中封装库与ORCAD封装的参数理解

实例:一直以来以为的是原理图上面的元器件的元件类型和元器件的封装必须是与库里面的元器件的封装一致对应,但是我遇到硬件工程师导给我的原理图中出现元器件的封装与库里面的封装名一致,元器件的类型却是与库里面的封装匹配的元器件的的类型不一致,但是我的网表依旧是能够导进去的,这是为什么呢?

解决办法以及理解:我之前的理解元器件的封装名和元器件的元件类型必须与库里面的一致,其实理解是太过于局面,在ORCAD中,元器件不存在元器件的元件类型这一个参数,元器件的元件类型的参数只是在PADS的软件中存在的,所以当就算是我DSN原理图导成LOGIC原理图时的元器件类型与库里面的不一致,但是只要我的库里面存在这一个封装,并且在这个库中的封装只对应了一个元件类型,元器件就能导进去,

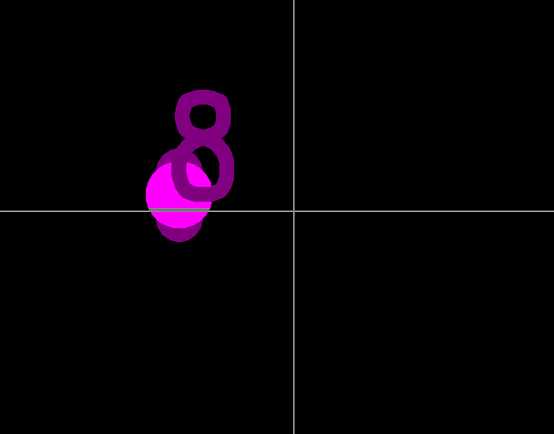

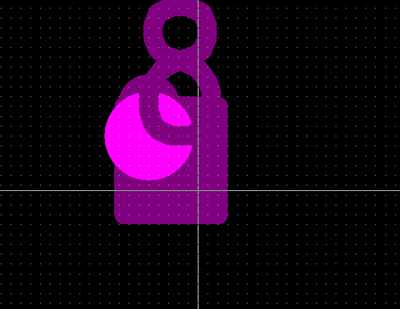

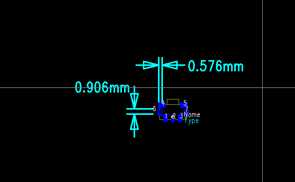

对于pads 中通孔型焊盘以及槽形焊盘的设置参数与做出的样式出现偏差的问题

实例:

问题:做出来的实际过孔的大小刚好是在参数设置的基础上偏差了0.07mm,这是为什么?

标签:没有 帮助 标示 设置 设定 bottom 如图所示 sign 电路

原文地址:https://www.cnblogs.com/xiaoqiuqiu/p/12557100.html