标签:com setup load register 方法 ola lin 应用 后端

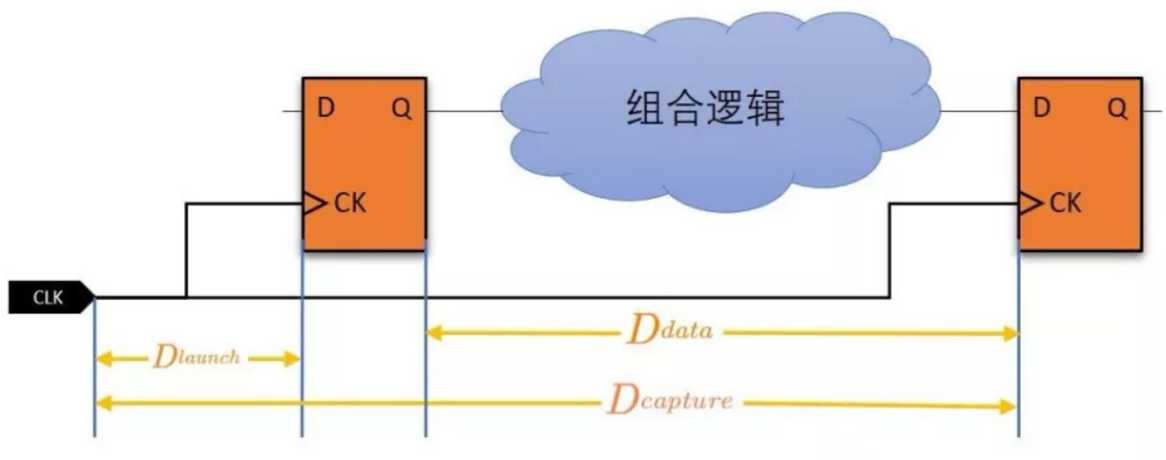

首先,我们回忆一下setup的定义。下图-1展示了一条典型的timing path以及setup的计算方法。

Setup定义:Data在clock到来之前必须要保持稳定一定时间。按照上图的timing path,setup应该满足如下条件:

1. 减少data line的delay

1) 换速度更快的cell。

对绝大多数工艺,任何一种标准单元(standardcell)都有不同种速度的Library,也就是常说的不同Vt的cell,比如HVT, RVT, LVT或者SLVT。其中HVT cell速度最慢,SLVT速度最快。而减少data line delay最常用的方法就是更换不同Vt的cell,比如HVT的cell换成RVT, LVT或者SLVT。

2)更换驱动能力更强的cell。

在某些timing path中,可能会出现因为cell的驱动能力比较弱而产生比较大的delay。这时就可以将这种cell更换成驱动能力更强的cell。比如X2倍的cell更换成X4或者X6的cell。

3)将net的layer更换成阻值更低的金属层以减小cell的load和net delay

对于金属层,一般来说越向上的层阻值越小,而阻值越小cell delay也越小,net delay也越小。

2. 减少launch clock line的delay

Clock line不同于data line的地方在于,在实际设计中,一般是要求clock line必须使用最快的cell。具体原因需要读者理解skew,latency和OCV的概念后再做解释。因此要使clock line变快,更换不同Vt的cell是行不通的。可行的办法是根据clock line的物理和逻辑情况通过减少clock line的级数来减小delay。但是这极其限制其实现的可能性,因此在实际工作中这种方法应用的并不多。

3. 增加capture clock line的delay

此方法是后端常用的所谓useful skew的方法。实际操作很简单,就是在capture register的CK pin插入buffer或者inverter以增加capture clock delay。

标签:com setup load register 方法 ola lin 应用 后端

原文地址:https://www.cnblogs.com/lelin/p/12611643.html