标签:模型 stack 处理异常 handle 必须 cti system ted cps

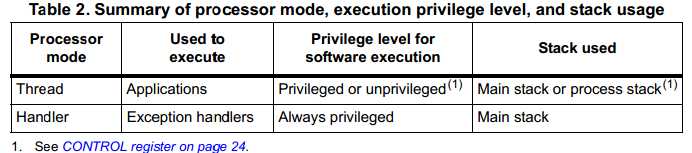

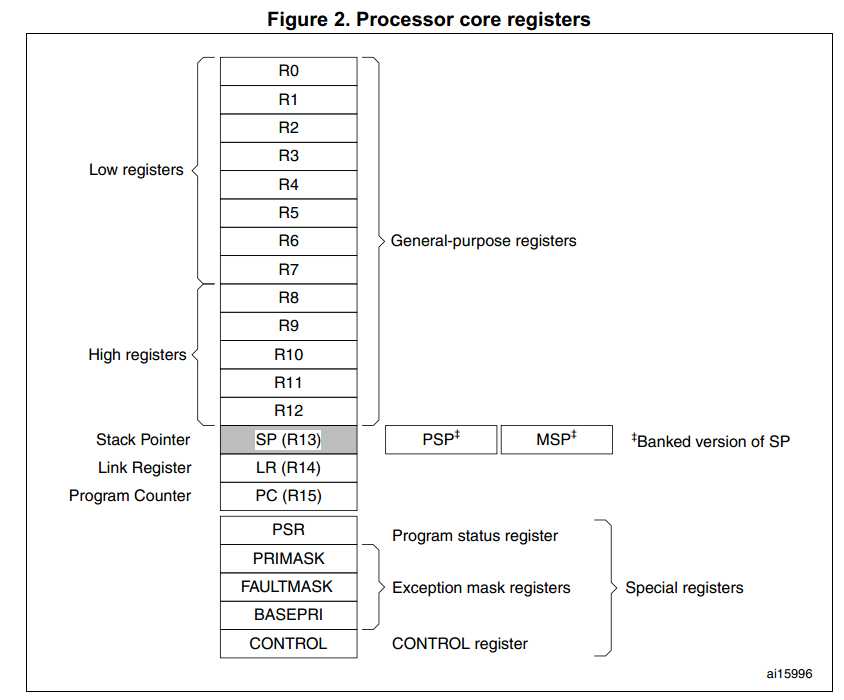

处理器使用一个完全递减的堆栈,并装配两个:main stack 和 process stack, 具有main stack指针的独立副本。

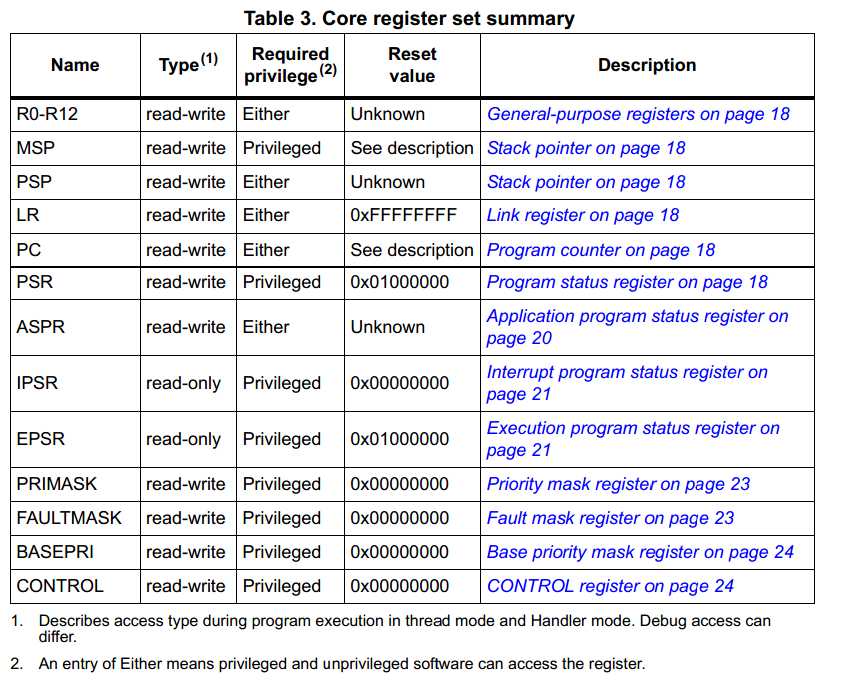

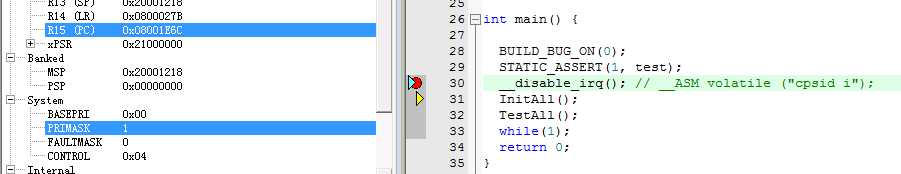

在Thread 模式下,由CONTROL控制使用哪一个堆栈;在Handler模式下,一直使用main堆栈。

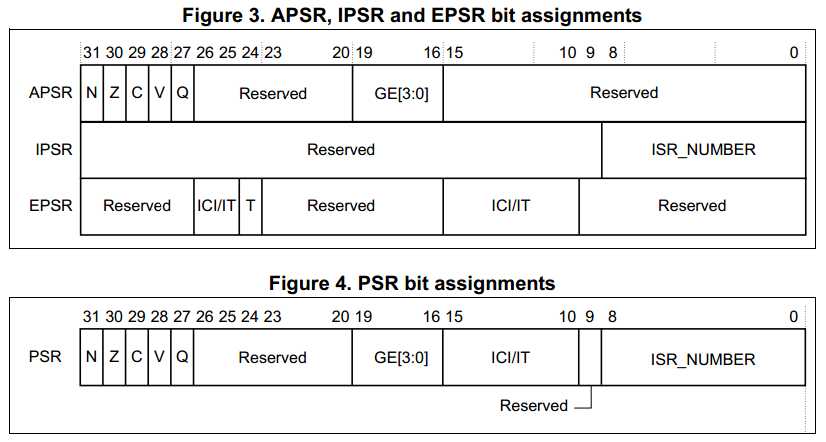

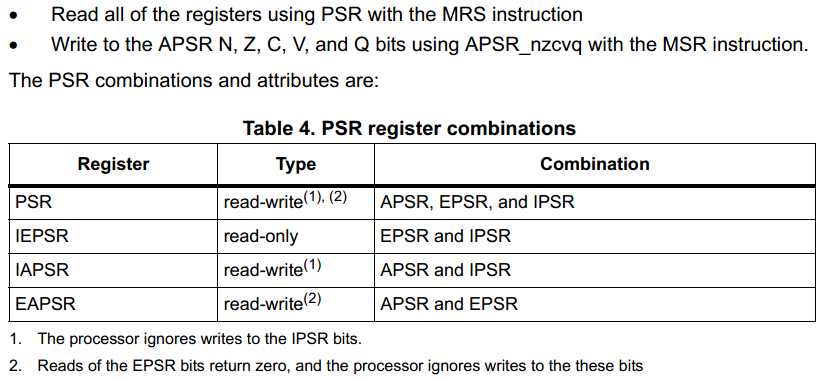

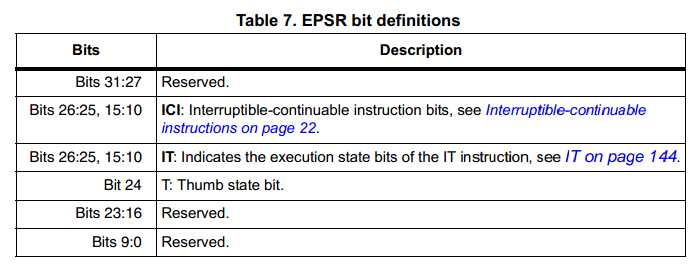

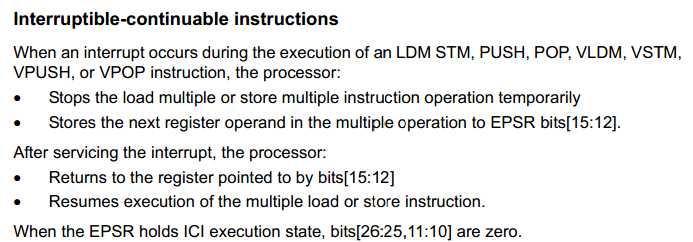

APSR, IPSR, EPSR这3个寄存器接合在PSR中,可以单独访问,也可以组合访问,比如:

标签:模型 stack 处理异常 handle 必须 cti system ted cps

原文地址:https://www.cnblogs.com/qiyuexin/p/12622460.html