标签:技术 ali 来源 block 进入 目的 logs 就是 不发送

这是美国的达拉斯半导体公司推出的一项特有的单总线(1-wire)技术。该技术与别的总线不同,它采用一根信号线,既可以传输时钟,又可以传输数据,而且数据传输是双向的。因此该总线技术具有线路简单,硬件开销少,成本低廉,便于总线扩展和维护等优点。该技术适用于单主机系统,能够控制一个或者多个从机设备。

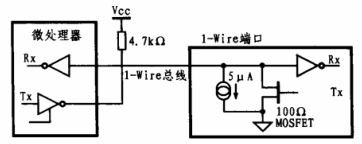

单总线(1-wire)即只使用这一根数据线进行数据交换、控制。设备(主机或从机)通过一个漏极开路或三态端口连至该数据线,以允许设备在不发送数据时能够释放总线,而让其它设备使用总线,其内部等效电路如图所示:

所有的单总线器件都要遵循严格的通信协议,其目的以保持数据的完整性。1-wire协议定义了:复位脉冲、应答脉冲、写0、读0和读1时序等信号类型。

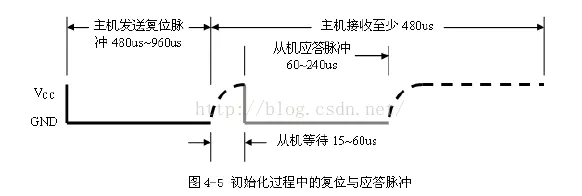

初始化时序(复位+从机应答)

主机通过拉低单总线480 ~ 960 us产生复位脉冲,然后释放总线,进入接收模式。主机释放总线时,会产生低电平跳变为高电平的上升沿,单总线器件检测到上升沿之后,延时15 ~ 60 us,单总线器件拉低总线60 ~ 240 us来产生应答脉冲。主机接收到从机的应答脉冲说明单总线器件就绪,初始化过程完成。

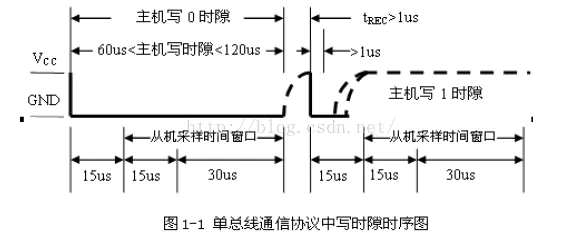

写间隙

写间隙有两种,包括写0的时间隙和写1的时间隙。

当数据线拉低后,在15 ~ 60 us的时间窗口内对数据线进行采样。如果数据线为低电平,就是写0,如果数据线为高电平,就是写1。主机要产生一个写1时间隙,就必须把数据线拉低,在写时间隙开始后的15 us内允许数据线拉高。主机要产生一个写0时间隙,就必须把数据线拉低并保持60 us。

读间隙

当主机把总线拉低是,并保持至少1 us后释放总线,必须在15 us内读取数据。

文章参考:

作者:文久_

链接:https://www.jianshu.com/p/4d4b7f7d9280

来源:简书

标签:技术 ali 来源 block 进入 目的 logs 就是 不发送

原文地址:https://www.cnblogs.com/wyd-blogs/p/12634481.html