标签:strong 基本结构 调用 修改 rar 局限 就是 一个 ali

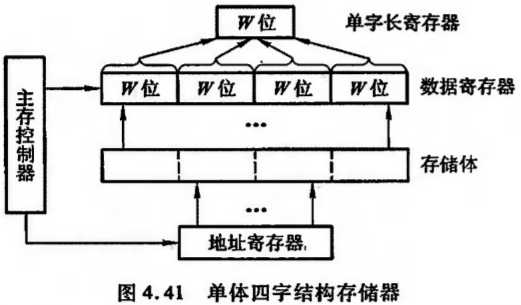

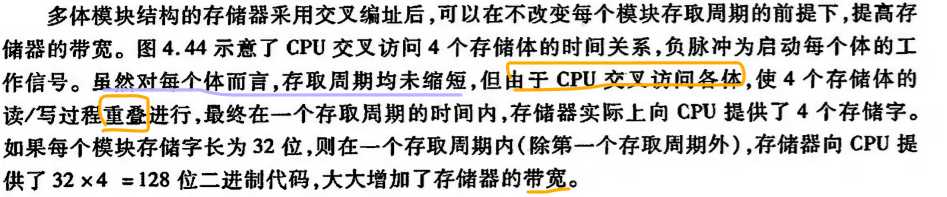

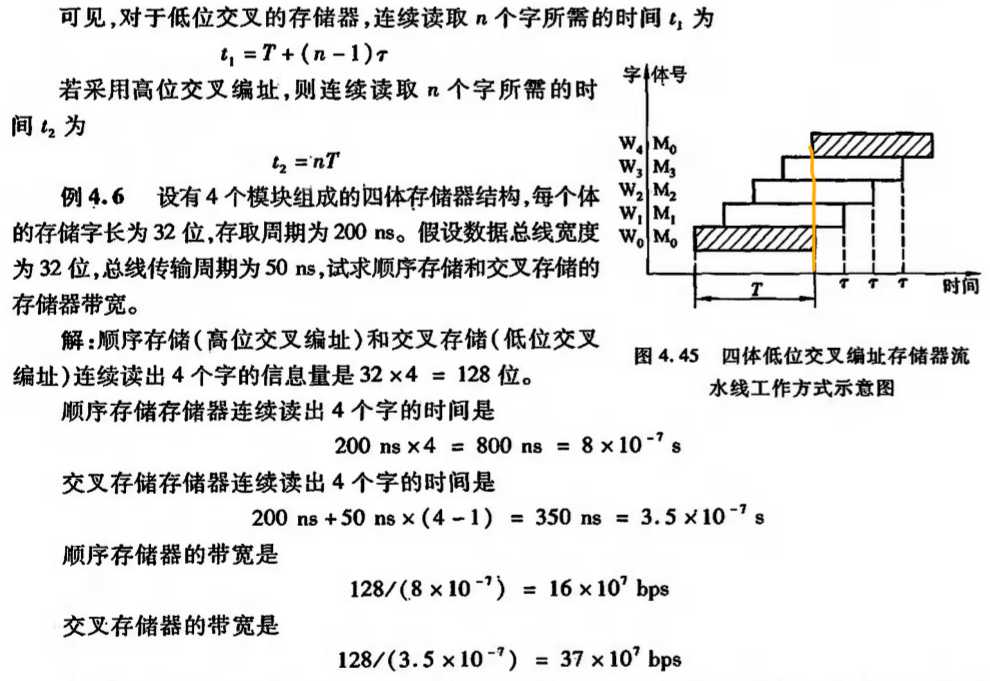

原理:在一个存取周期内,从同一地址取出四条指令(之前是一次一个的),再将这四条指令按顺序送至CPU执行——速度提高了

前提:指令和数据连续

(1)SDRAM

(2)RDRAM

(3)带Cache的RDRAM

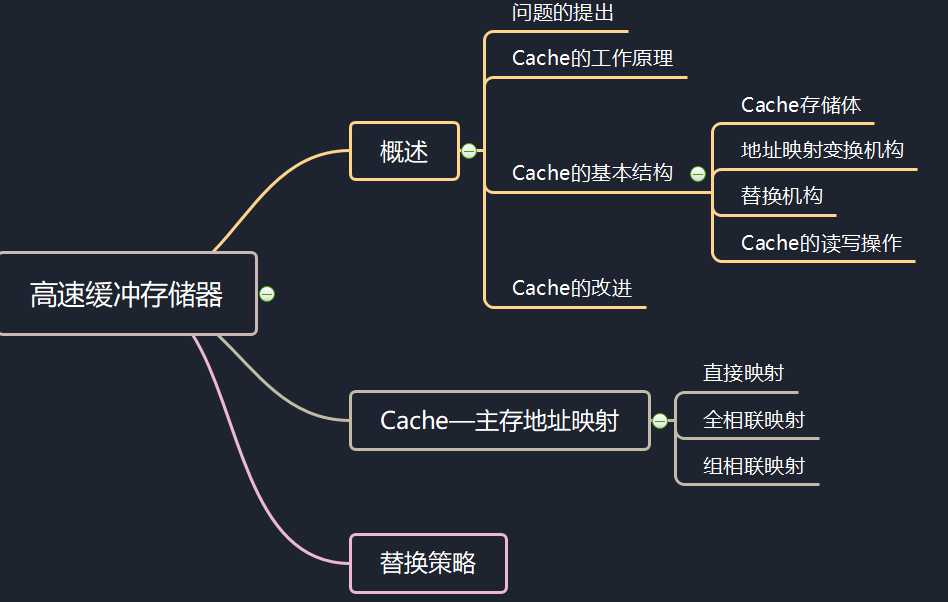

①CPU等待I/O设备,浪费时间→在CPU与主存之间加一级缓存

②主存速度提高慢,跟不上CPU的速度了

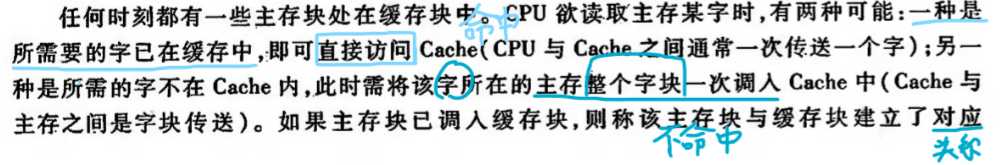

## 重大发现:由于指令和数据在主存里是连续存放的,一些子程序、循环程序和常数会多次调用→CPU访存有相对的局限性→将CPU近期要用到的数据提前送到cache,提高速度

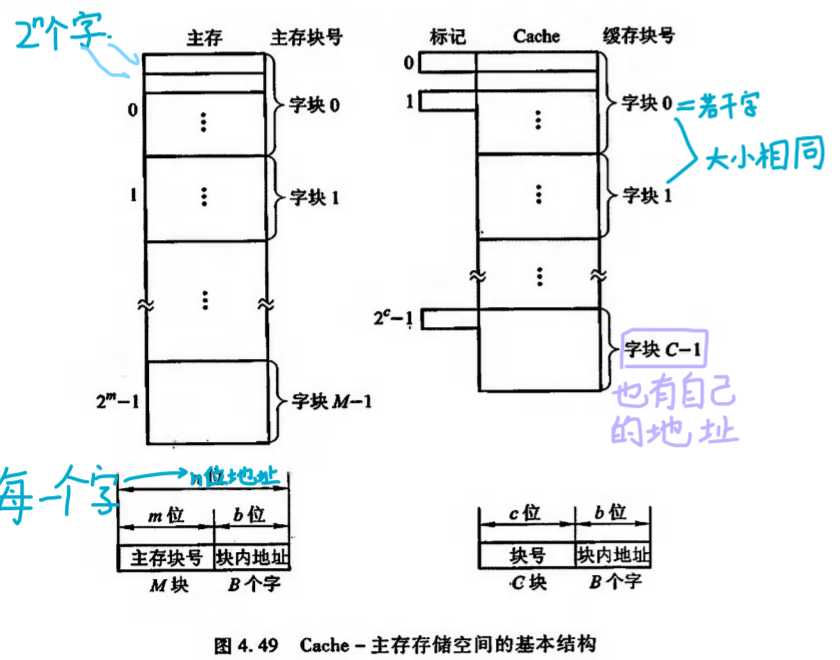

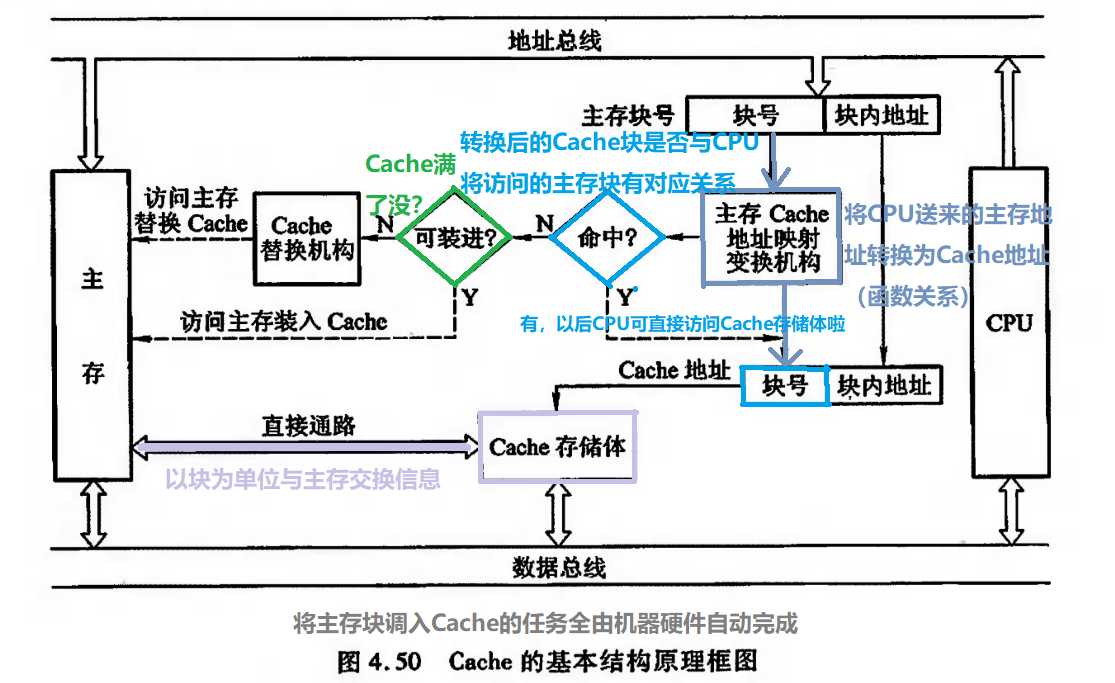

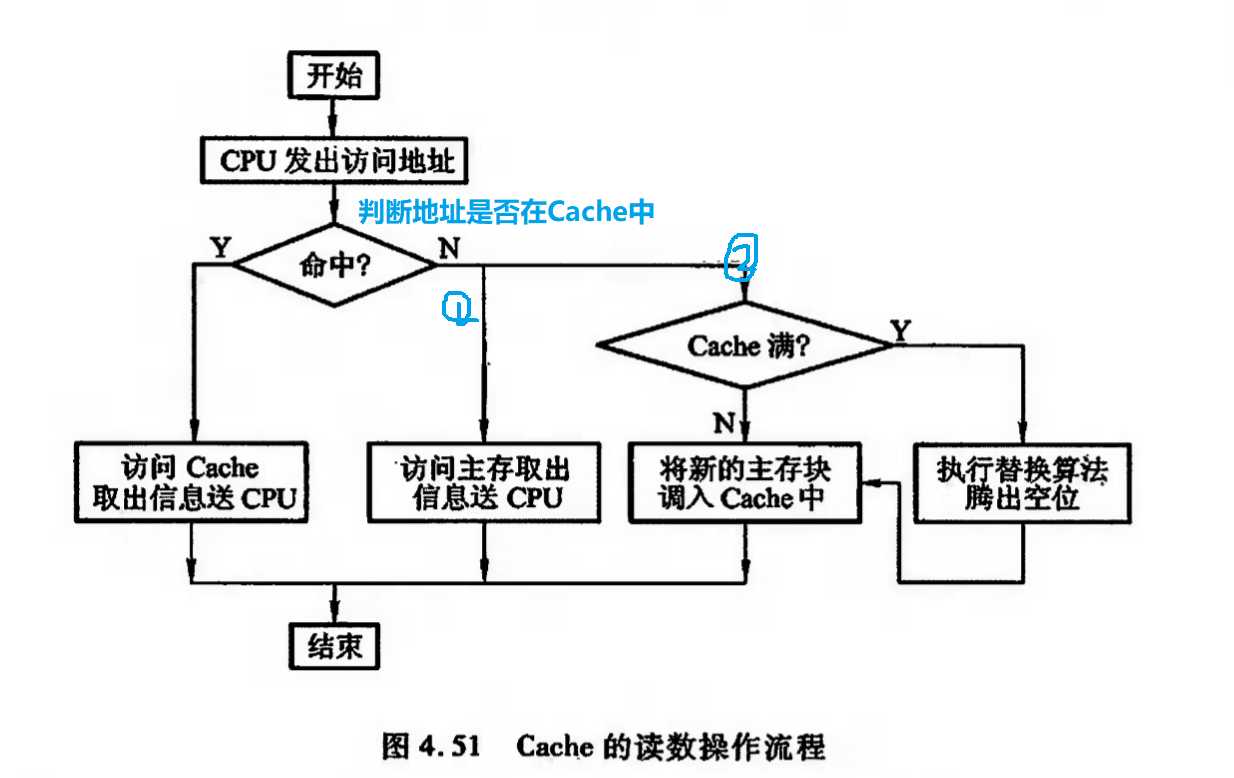

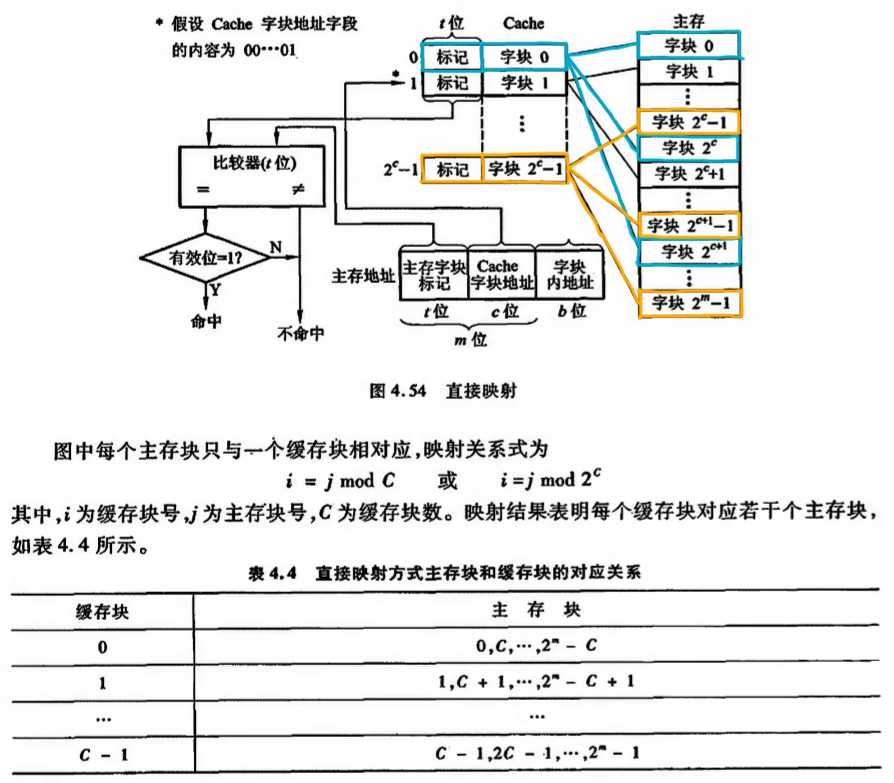

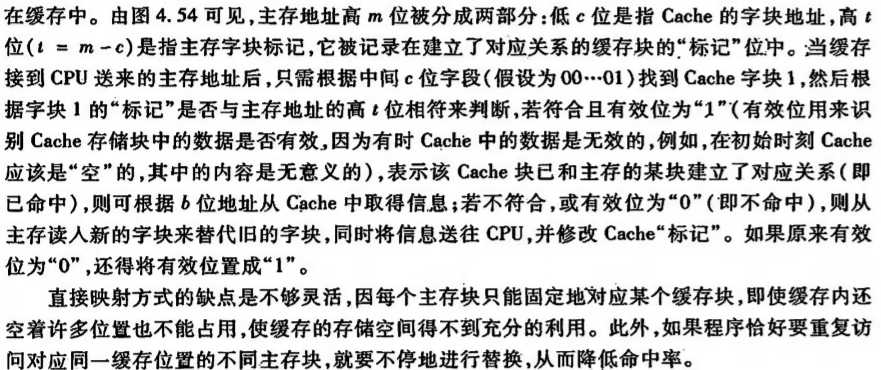

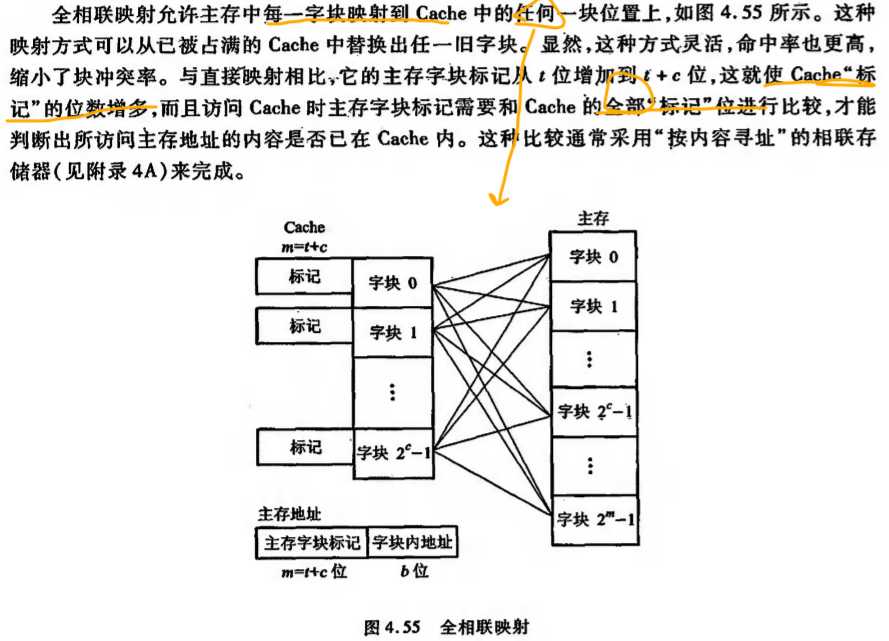

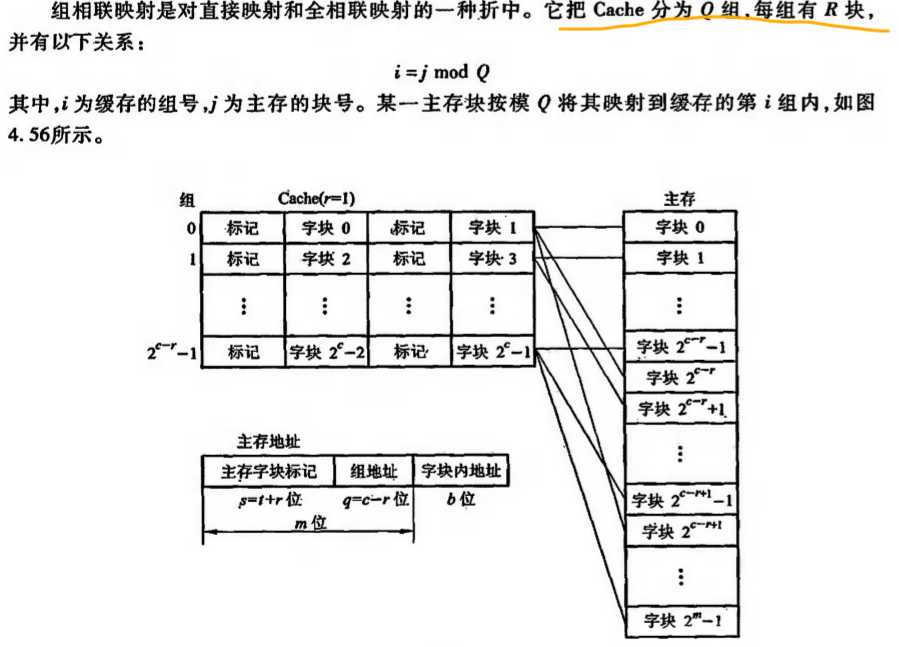

缓存里的块数远小于主存的,所以缓存里的块数是根据CPU的需要不断变化的。好是好,只是缓存里的每个块都要做一个标记,(啊~这次来我这里待的小可爱是你呀~~),标记就是主存里的块的编号。那当CPU读信息时,先将两者的块地址进行比较。

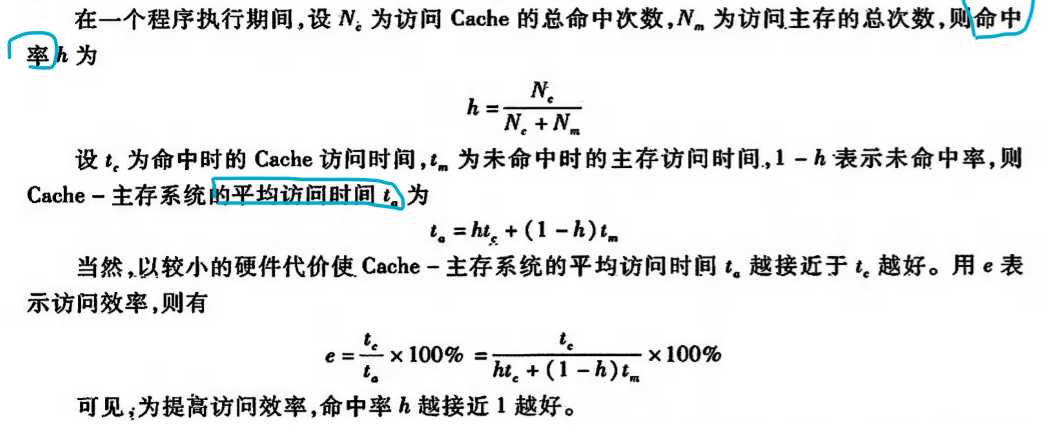

命中率与容量(越大越好)、块长(过小过大都不好)有关

写操作:使Cache与主存内容保持一致

法一:写直达法

写操作时,数据既写入Cache又写入主存→保证了数据一致,但增加了访存次数

法二:写回法

写操作时,只把数据写入Cache,而不写入主存,当Cache的数据被替换出去时才写回主存→数据会不一致;那如何判断呢?在Cache中的每一块要增设一个标志位,表示“清”(人家是清白的啦~就是未被修改过,和贮存是一致的)和“浊”(被污染了...被修改过,与主存不一致)。在为“清”时,Cache块不变化,和主存是一样的~,但“浊”的话,把Cache块的内容写到主存里,并把标志位变为清,进行新的一轮。

优点:简单。

标签:strong 基本结构 调用 修改 rar 局限 就是 一个 ali

原文地址:https://www.cnblogs.com/syzyaa/p/12633915.html