标签:style blog http io color ar os for sp

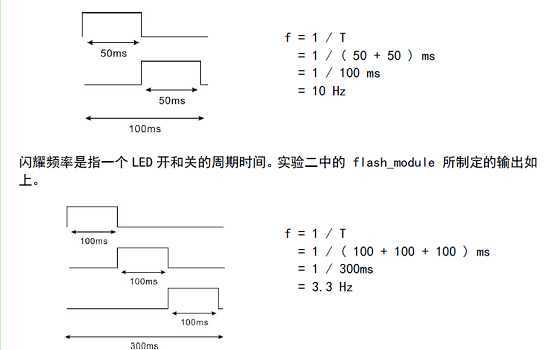

(1) 扫描频率和闪耀频率?

模块:

/**************************************** module name:flash_module function:flash a led at 10Hz by yf.x 2014-11-4 ***************/ module flash_module( CLK, RST_n, LED ); input CLK,RST_n; output LED; /*********************************/ //DE2-115 use 50MHz osc, 50M*0.05-1=2_499_999 parameter T50ms=22‘d2_499_999; /*********************************/ reg [21:0]count1; always @(posedge CLK or negedge RST_n) if(!RST_n) count1<=22‘d0; else if(count1==T50ms) count1<=22‘d0; else count1<=count1+1‘b1; /************************************/ reg rLED; always @(posedge CLK or negedge RST_n) if(!RST_n) rLED<=1‘b0; else if(count1==T50ms) rLED<=~rLED; /*********************************/ assign LED=rLED; endmodule

1 /*********************************** 2 module name:run_module 3 function:3 led light on one bye one at 4 each 100ms. 5 6 by yf.x 7 2014-11-04 8 ***********************************/ 9 10 module run_module( 11 CLK, 12 RST_n, 13 LED 14 ); 15 16 input CLK; 17 input RST_n; 18 output [2:0]LED; 19 20 /****************************************/ 21 //DE2-115 use 50MHz osc,50M*0.001-1=49_999 22 parameter T1ms=16‘d49_999; 23 24 /****************************************/ 25 26 reg [15:0]count1; 27 28 always @(posedge CLK or negedge RST_n) 29 if(!RST_n) 30 count1<=16‘d0; 31 else if(count1==T1ms) 32 count1<=16‘d0; 33 else 34 count1<=count1+1‘b1; 35 36 /**************************************/ 37 38 reg [9:0] count_ms; 39 40 always @(posedge CLK or negedge RST_n) 41 if(!RST_n) 42 count_ms<=10‘d0; 43 else if(count_ms==10‘d100) //100ms 44 count_ms<=10‘d0; 45 else if(count1==T1ms) 46 count_ms<=count_ms+1‘b1; 47 48 /*************************************/ 49 50 reg [2:0]rLED; 51 52 always @(posedge CLK or negedge RST_n) 53 if(!RST_n) 54 rLED<=3‘b001; 55 else if(count_ms==10‘d100) 56 begin 57 if(rLED==3‘b000) 58 rLED<=3‘b001; 59 else 60 rLED<={rLED[1:0],1‘b0}; 61 end 62 63 /*************************************/ 64 65 assign LED=rLED; 66 67 endmodule 68 69 70

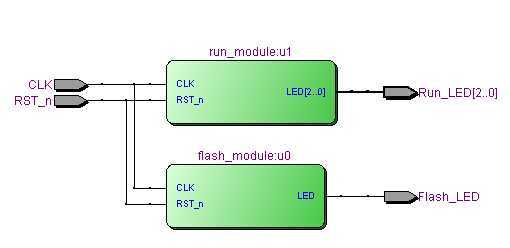

1 /**************************************** 2 module name:mix_module 3 function:top module,flash 1 led and run 3 led 4 5 pin assignments(for DE2_115) 6 ---------------------------------------- 7 CLK------------------------CLOCK_50 8 RST_n----------------------KEY[0] 9 Flash_LED------------------LEDG[3] 10 Run_LED[2:0]---------------LEDG[2:0] 11 12 *****************************************/ 13 14 module mix_module( 15 CLK, 16 RST_n, 17 Flash_LED, 18 Run_LED 19 ); 20 21 input CLK; 22 input RST_n; 23 output Flash_LED; 24 output [2:0]Run_LED; 25 26 /**************************************/ 27 28 wire flash_led; 29 30 flash_module u0( 31 .CLK(CLK), 32 .RST_n(RST_n), 33 .LED(flash_led) 34 ); 35 36 /************************************/ 37 38 wire [2:0] run_led; 39 40 run_module u1( 41 .CLK(CLK), 42 .RST_n(RST_n), 43 .LED(run_led) 44 ); 45 46 /***********************************/ 47 48 assign Flash_LED=flash_led; 49 assign Run_LED=run_led; 50 51 /************************************/ 52 53 endmodule

实验二说明:

(1) flash_module.v是一个闪烁灯模块,闪烁频率为10Hz。

(2) run_module.v是一个流水灯模块,扫描频率为3.3Hz。基本编程技巧:1ms的计数器->100ms的计数器->移位操作。

实验二完成框图:

实验二结论:

思维倾向“并行操作”对Verilog hdl语言的理解非常重要。

实验二疑问:

(1)run_module.v模块里为何先写一个1ms的计数器,再用1ms的驱动完成一个100ms的计数器,而不是直接写一个100ms的计数器?

【黑金教程笔记之003】【建模篇】【Lab 02 闪耀灯和流水灯】—笔记

标签:style blog http io color ar os for sp

原文地址:http://www.cnblogs.com/halflife/p/4077807.html