标签:概率 ram 错误 表示 实现 strong ack 系统资源 auto

因此如果简单的使用多组同步器进行数据信号跨时钟域传输,可能导致数据信号中多位数据在传输过程中发生错误。

前级时钟=发送时钟;

后级时钟=采样时钟=接收时钟;

根据发送时钟端数据信号的变化速率和采样时钟频率,可以分为一下三种情况。

问题:上升沿检测电路检测的是什么信号的上升沿?

使用发送端的控制信号进行同步,在采样到慢时钟域发出的控制信号后,接收数据的时钟沿进行数据采样。

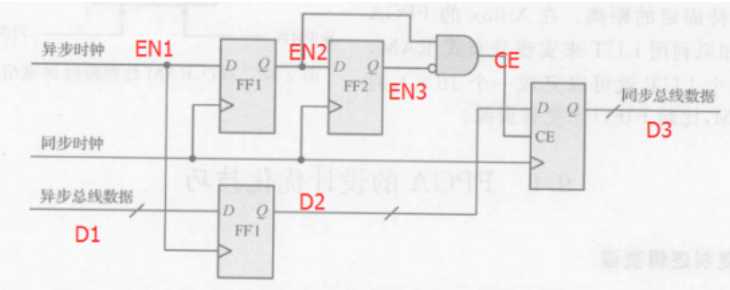

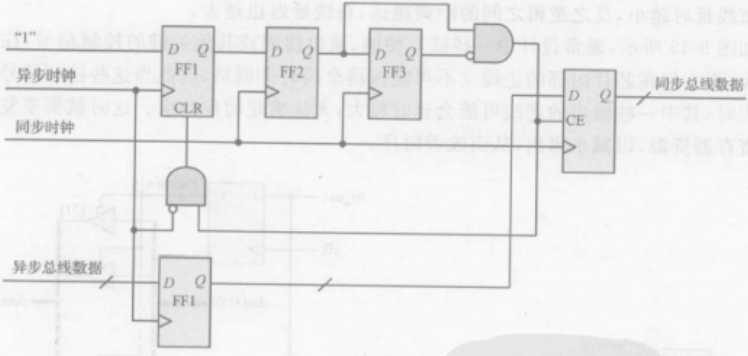

使用如图所示的上升沿检测信号CE作为控制信号(或数据接收的使能信号)控制数据信号的传输。

由于发送时钟比接收时钟快,对于接收时钟而言,发送时钟相当于窄脉冲。

为避免检测不到上升沿,可以结合窄脉冲捕获电路和上升沿检测电路进行边沿检测,并将结果作为使性能信号,但前提是发送时钟频率不能太快。

问题:可能会导致数据采样不完整,数据丢失的现象。

无法使用握手信号进行数据传输,需要使用FIFO。

FIFO设计

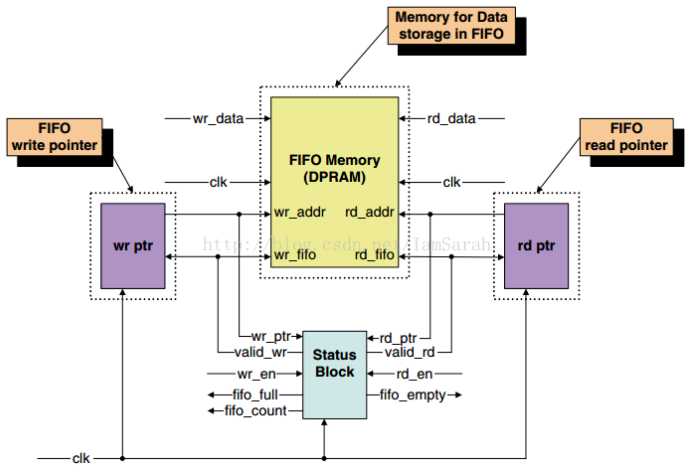

同步FIFO架构:

如图所示为同步FIFO,DPRAM(双端RAM)作为FIFO的存储器,允许读写同步进行,由状态模块控制读写的指针和FIFO的状态。

同步fifo表示fifo状态的表示方法

异步FIFO架构:

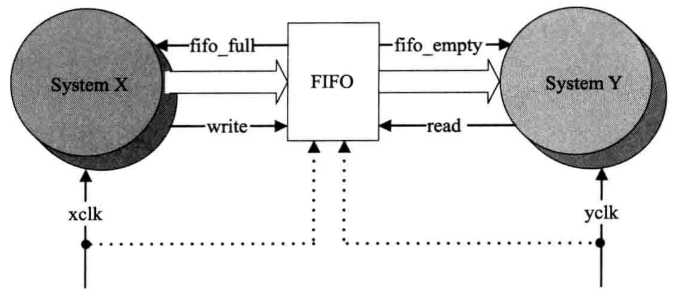

异步FIFO用于对性能要求较高的设计中,尤其是始终延迟比系统资源更为重要的环境中。

可以使用与同步FIFO类似的双端RAM和单独读写端口实现,但是要注意产生fifo_empty和fifo_full时要避免出现亚稳态现象。

避免使用二进制计数器实现指针

在写请求有效时,写指针在写时钟作用下递增;在读请求有效时,读指针在读时钟下递增。

由于读写指针分别与其各自的时钟同步,彼此之间异步,使用二进制计数器实现指针时,可能会导致比较指针值取样错误。

标签:概率 ram 错误 表示 实现 strong ack 系统资源 auto

原文地址:https://www.cnblogs.com/lizhiqing/p/12677013.html