标签:setting accept increase where 等于 aci enc ide inf

参考文章:Optimizing Transient Response of Internally Compensated dc-dc Converters With Feedforward Capacitor,http://www.ti.com.cn/cn/lit/an/slva289b/slva289b.pdf

翻译文章:优化带前馈电容的内置补偿 DC-DC转换器的瞬态响应,http://www.ti.com.cn/cn/lit/an/zhca058/zhca058.pdf

1. 基本原理

在内部补偿的converter的FB网络增加前馈电容,可调节控制环穿越频率和相位裕度,提升控制性能。

计算公式:可以参考文章:Evaluation and Performance Optimization of Fully Integrated DC-DC Converter.pdf

零点频率:

极点频率:

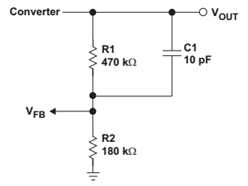

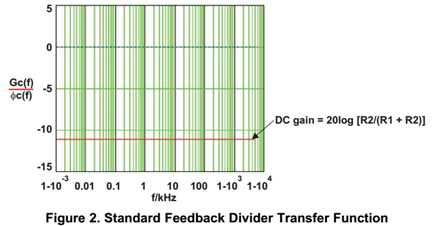

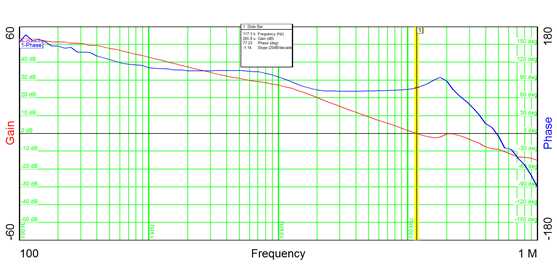

未补偿之前的波特图:

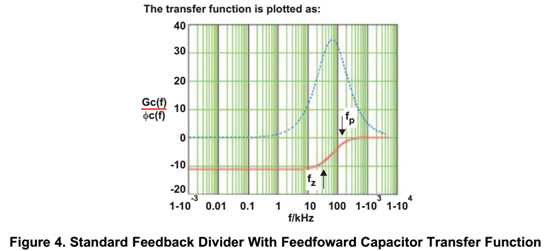

补偿之后的波特图:

To optimize transient response, a Cff value is chosen such that the gain and phase boost of the feedback increases the bandwidth of the converter, while still maintaining an acceptable phase margin. . In general, larger values of Cff provide greater bandwidth improvements. However, if Cff is too large, the feedforward capacitor causes the loop gain to crossover too high in frequency and the Cff phase boost contribution is insufficient, resulting in unacceptable phase margin or instability.

Cff的目的是提升反馈回路的增益和相位,同时保持可接受的相位裕度。

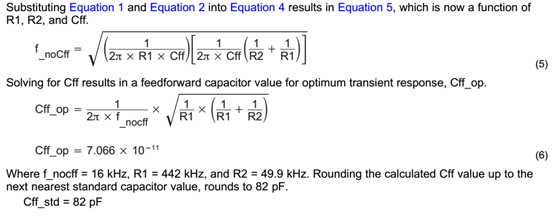

2. 如何计算前馈电容

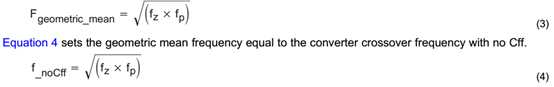

首先是补偿频率的选择。这里采用一种近似的方法,将补偿之后的频率设置为等于fz和fp的几何平均数,即fz和fp对数域的平均频率,参考下方公式3、4。在几何平均频率处,Cff电容带来的相位提升最大(The geometric mean frequency equation is used to calculate the frequency where the phase boost from the zero and pole is at a maximum.)

把几何平均频率选择在没有Cff电容时的穿越频率(Setting the geometric mean frequency equal to the converter crossover frequency with no Cff positions the maximum phase boost of Cff at f_nocff. )。但是由于Cff电容会同时提升相位和增益,新的穿越频率会比几何平均频率大(However, because Cff introduces a boost in phase and in gain, the new crossover frequency occurs at a frequency greater than the geometric mean frequency.)。按照上述公式(6)即可计算出最优化的前馈电容。最优化指的是,在穿越频率和相位裕度之间折中达到最优。

3. 更进一步,如何根据需求选择前馈电容

前馈电容选取大于计算的电容,会导致穿越频率更高(响应速度更快),但是相位裕度会减小。如果选取小一些,穿越频率会低一些,当相位裕度会大一些。需要根据实际情况选取,并用测试验证。

For most applications, this is an optimum placement of the feedforward capacitor response. Increasing the feedforward capacitance value pushes both the zero and pole frequencies closer to the origin which increases the crossover frequency but can result in lower overall phase margin. This corresponds to a faster loop at the expense of lower phase margin. Decreasing the Cff value results in the opposite result until a certain point where the feedforward capacitor gain and phase boost contribution diminishes and approaches the response of having no Cff. Having too small a Cff value injects a zero and pole at frequencies too high and effectively too late in loop response, resulting in little or no performance improvement.

DCDC: 前馈电容Feed forward capacitor增强环路稳定性

标签:setting accept increase where 等于 aci enc ide inf

原文地址:https://www.cnblogs.com/dongshenscut/p/12773360.html