标签:联想存储 编码 两种 维数 并行 缓冲 info 机构 进制

为什么要引入基本分页内存管理?

答:在连续存储管理方式中,固定分区会产生内部碎片,动态分区会产生外部碎片。这两种技术对内存的利用率都比较低。而分页式存储管理方式把主存空间划分为大小相等且固定的块,块相对较小,作为主存的基本单位,每个进程也以块为基本单位划分,进程在执行时,以块为单位逐个申请主存中的块空间。

分页式存储管理方式从形式上来看,很像固定分区,但却有着本质的不同点:

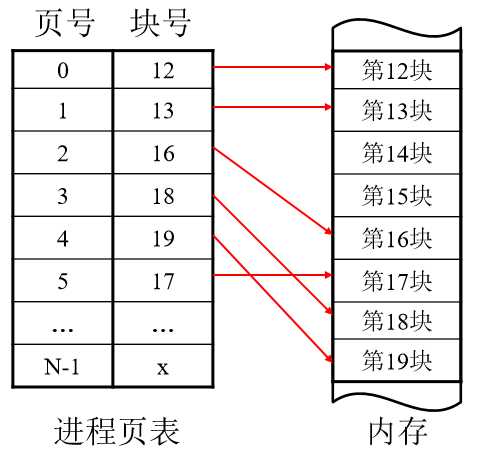

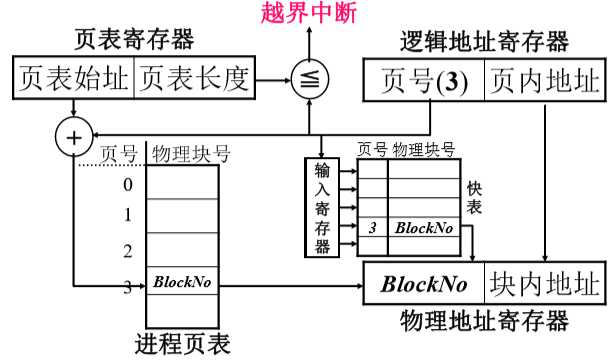

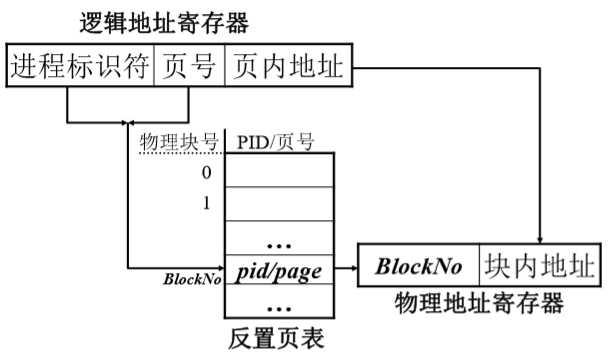

进程页表:为了便于在内存中找到进程的每个页面对应的物理块,系统为每个进程建立了一张页表,记录页面在内存中对应的物理块号,页表一般存在内存中。

页表的第一部分存的是页号,第二部分存的是物理内存中的块号,页表项的第二部分与逻辑地址的第二部分共同组成物理地址。

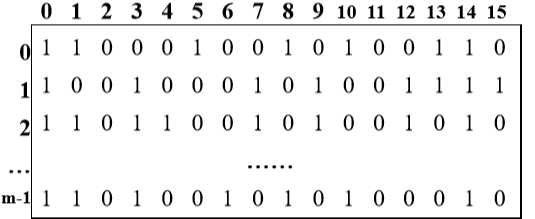

位示图

利用位示图(即二维数组Map[m][n])的一 位(0/1)来表示一个内存物理块(或磁盘盘块)的使用情况,使内存所有物理块(或磁盘上所有盘块)都与一个二进制位相对应

物理块(盘块)的分配

物理块(盘块)的回收

将回收物理块(或盘块)的物理块(或盘块)号b 转换为位示图中的行号i和列号j:

i = b DIV n;

j = b MOD n;

按物理块(或盘块)号回收物理块(或盘块)

根据回收物理块(或盘块)对应二进制位的行/列号,并修改位示图和进程页表

每个页表项代表一个页面的地址,一般很小。

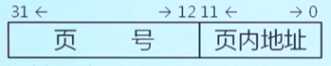

以32位逻辑地址为例,字节为编码单位,一个页面的大小为4 KB,所以2的32次方 B 除以4 KB地址空间一共有 1 M 页,则需要log 2 (1 M) = 20 位才能保证表示范围能容纳所有的页面,又因为以字节为编码单位,[20 / 8] = 3 B(字节),所以页表项的大小应该大于等于3 B,取4 B为常见。

所以该页的页号为:页表始址+页号x页表项长度

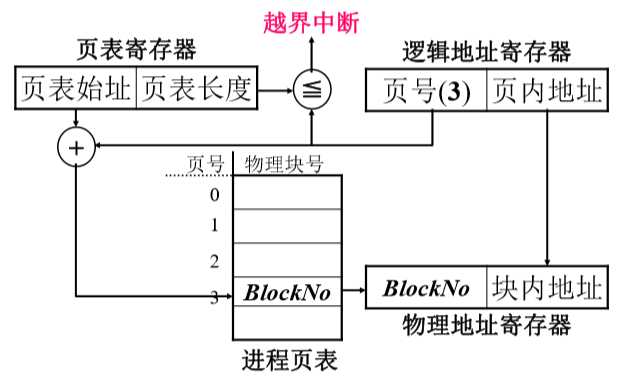

从上面我们可以看出:CPU要想获取一个数据时,必须两次访问内存:

1、从内存中的页表中,寻找对应的物理块号,将物理块号与页内地址组合成物理地址。

2、根据组合成的物理地址,来获取数据。

所以为了提高效率就引进了快表,什么是快表?

在地址变换机构中,增设一个具有并行查寻能力的特殊高速缓冲寄存器,称为“联想存储器”或“快表”。 用来存放当前访问的若干页表项,加速地址变换过程,命中率达到90%以上 。

在引入快表的分页存储管理方式中,通过快表查询,可以直接得到逻辑页所对应的物理块号,由此拼接形成实际物理地址,减少了一次内存访问,缩短了进程访问内存的有效时间。

但是,由于快表的容量限制,不可能将一个进程的整个页表全部装入快表,不一定每次在快表中都能找到要寻找得页号,所以在快表中查找到所需表项存在着命中率的问题。在快表中查不到还是得往页表中查找。但快表的命中率高,在总体上来说,还是减少了访问内存的时间。

由于引入了分页管理,进程在执行时不需要将所有页都调入内存页框中,只要将保存有映射关系的页表存入内存中即可。

我们这里考虑一下页表的大小,以32位逻辑空间,页面大小4 KB ,页表项大小4 B 为例,若要实现进程对全部逻辑地址空间的映射,则每个进程需要需要2的20次方个页表项。2的20次方个页表项 * 4 B ,为4 MB ,也就是说每个进程在页表项这一块就需要4 MB 的主存空间,显然这是比较大的内存占用。即使不考虑对全部逻辑地址空间的映射,一个逻辑地址空间稍大的进程,其页表项所占用的主存空间也是过大的。

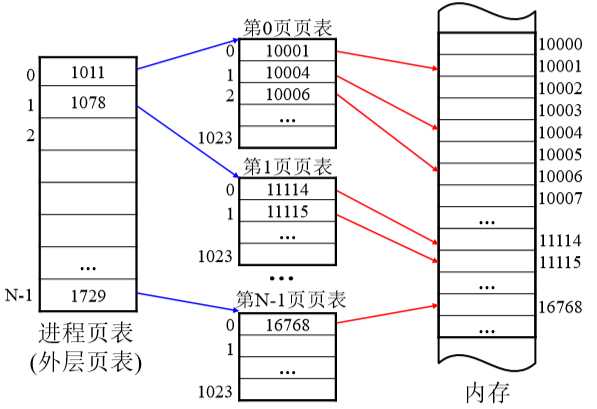

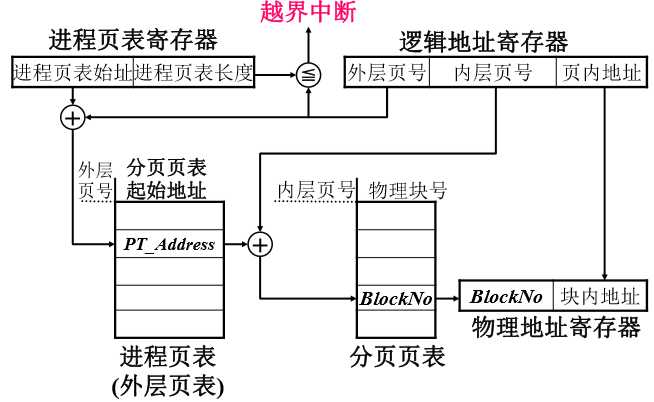

所以,为了压缩页表,我们将页表映射的思想进一步延伸,使用一个层次结构的页表——两级页表。

对页表按内存物理块大小进行分页,对它们进行 编号并离散地存放亍不同的物理块中;同时为离 散分配的页表分页再建立一张页表,称之为外层 页表,以记录各页表分页对应的物理块号 。

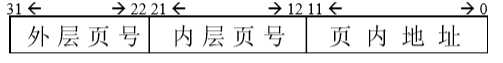

以32位逻辑地址空间、页面大小为4KB的系统为例,若采用一级页表结构,则每个进程页表的页 表项可达1M(2的20次方)个;而若采用两级页表结构,由于各页表分页包含4KB/4B=1K个页表项,故需1K(2的10次方) 个页表分页即可(也就是说每一页的页表有1K个页表项),因此外层页表的外层页号及内 层页号均为10位。此时逻辑地址结构为:

其结构示意图如下:

其地址变换结构如下:

对亍64位计算机,如规定页面大小仍为4KB,则每 个进程的页表项可达264/4K=252个,且外层页表可 能有252/210 =242个页表项;即使按每个页表分页 1M个页表项来划分(假设页表项大小4B),页表 分页将达到4MB,而外层页表仍有252/220 =4G个 页表项,要占用16GB的连续内存空间。

可见,无论 怎样划分,其结果都是不能接受的。因此,必须采 用多级页表,将16GB的外层页表再进行分页,并将 各个分页离散的分配到不相邻接的物理块中,在利 用第二级的外层页表来映射它们之间的关系。事实 上,对于64位的机器,用三级页表结构都很难适应

其地址变换机构如下:

标签:联想存储 编码 两种 维数 并行 缓冲 info 机构 进制

原文地址:https://www.cnblogs.com/Hhhighway/p/12819084.html