标签:特征 ant 加减法 介绍 cell 实现 64位 直接 手册

逻辑资源:

以Xilinx-SPARTAN6-XC6SLX25为例

LC ---Logic Cell---逻辑单元

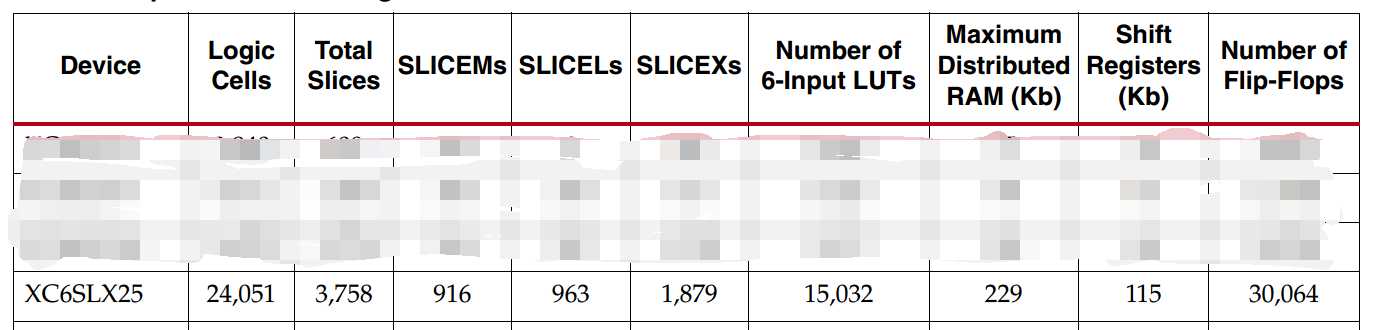

首先介绍概念最简单的逻辑单元,Logic Cell是Xilinx定义的一种标准,用于确定不同系列器件的“大小”。而在所有器件中,LC与LUT都有一个比例,但不同器件的LUT和FF搭配不一定相同,因此该比例往往会在数据手册中给出。例如在SPANTAN-6的UG384中就给出:

此外可以看看社区的回答: https://forums.xilinx.com/t5/Virtex-Family-FPGAs-Archived/logic-cell-vs-CLB/td-p/743699

CLB---Configurable Logic Block

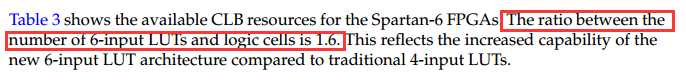

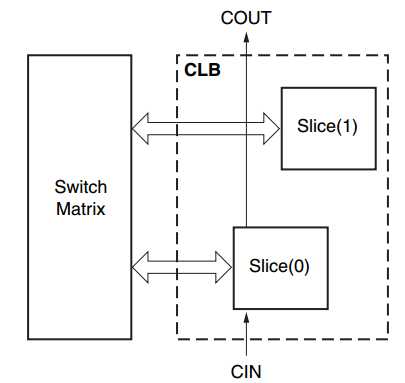

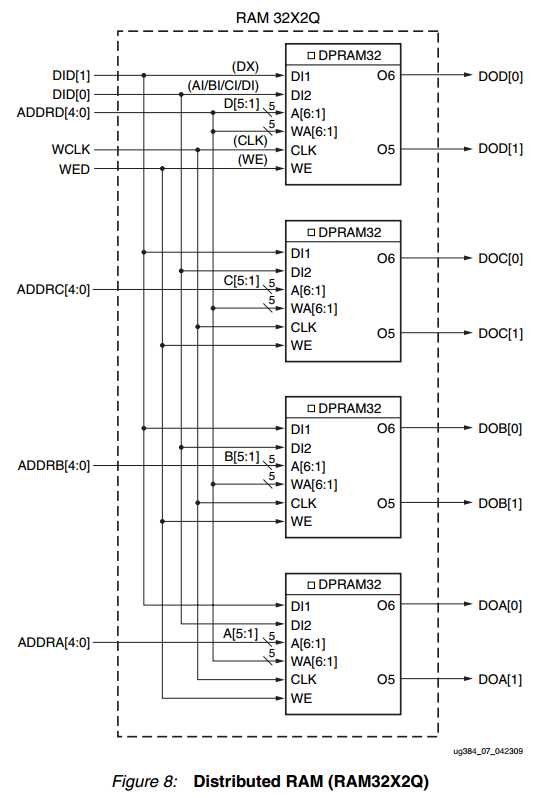

可配置逻辑块,是实现时序电路与组合电路的重要逻辑资源。CLB由多个(一般为4个或2个SPANTAN-6,并行垂直列)相同的Slice和附加逻辑(算数和进位链)构成。每个CLB模块不仅可以用于实现组合逻辑和时序逻辑,还可以配置为分布式RAM和分布式ROM。

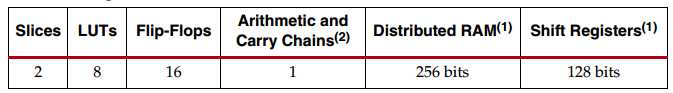

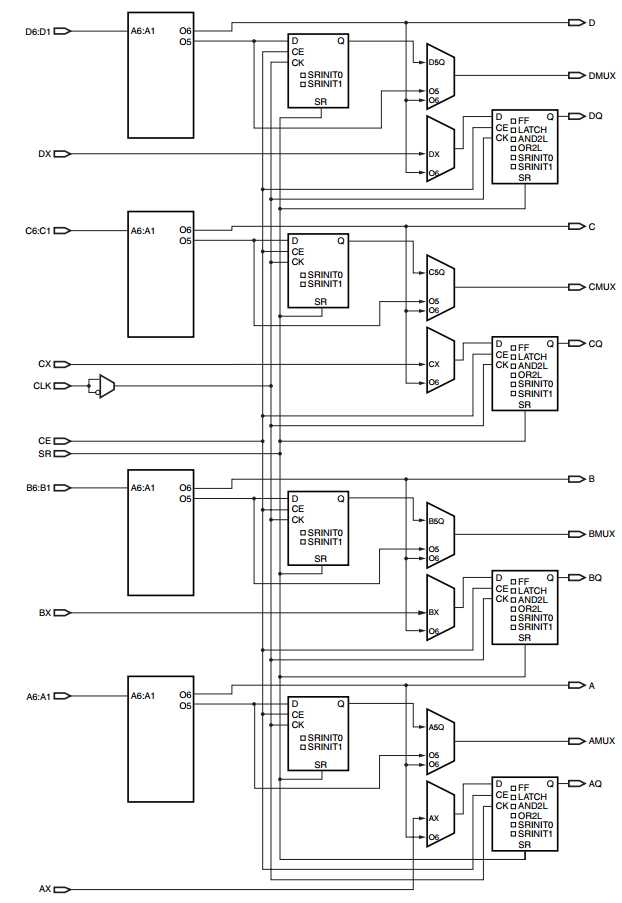

SPARTAN-6中每一个CLB的资源如下:

LS---Logic Slice

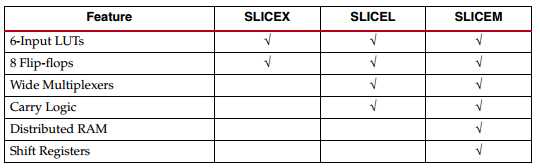

逻辑片,逻辑片由LUT、FF、各种逻辑(门阵列)组成。Slice有三种类型,分别是:SliceL(logic)与SliceM(memory)、SliceX。在每一列CLB中有两列Slice,其中一列为SliceX,另一列M与L交替。他们特征/功能如下表。

可以从表中看出就功能而言M>L>X。

SliceM

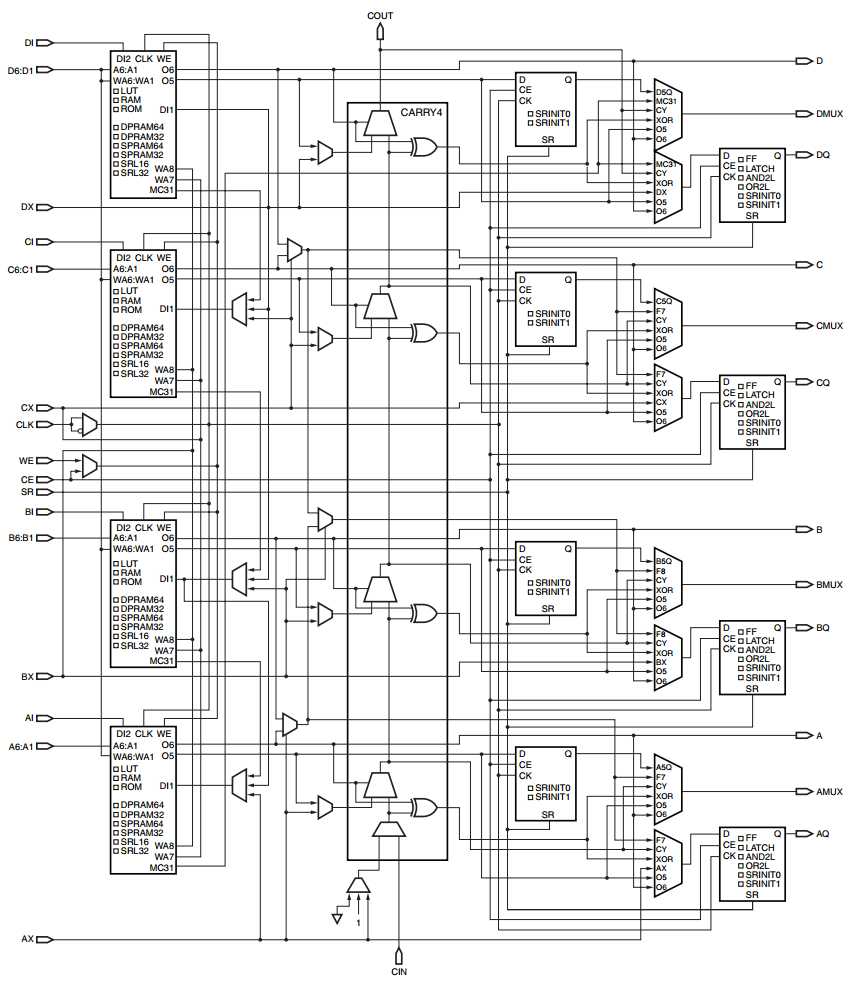

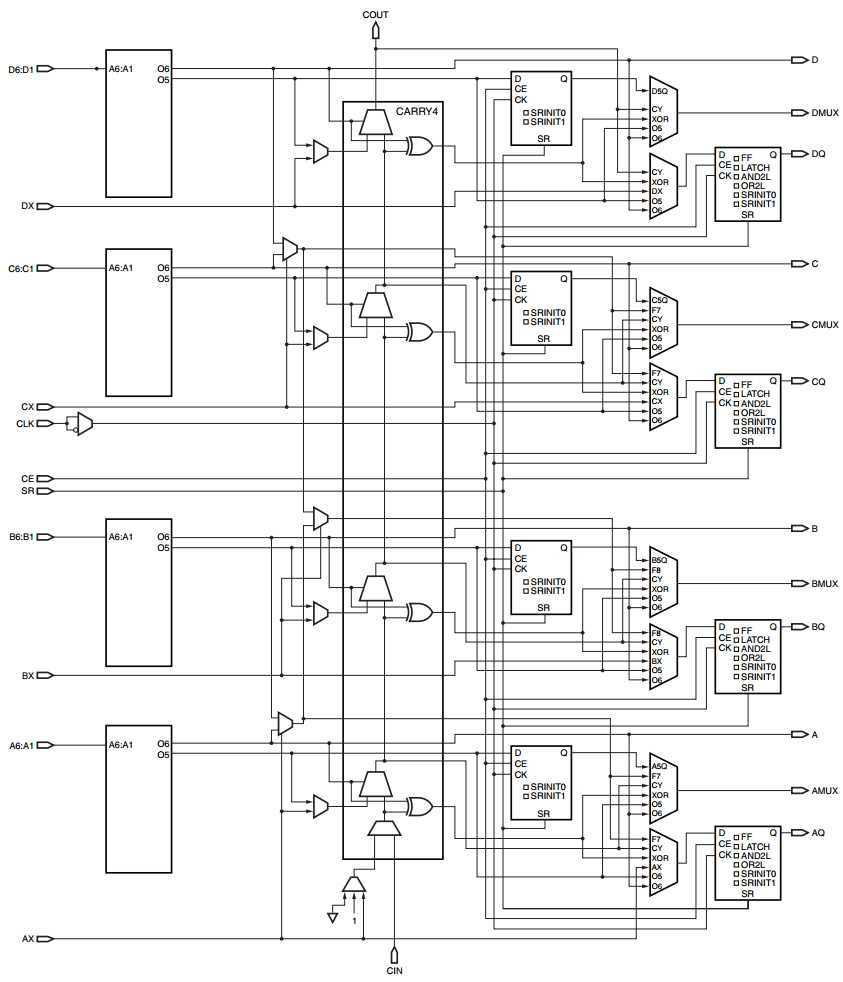

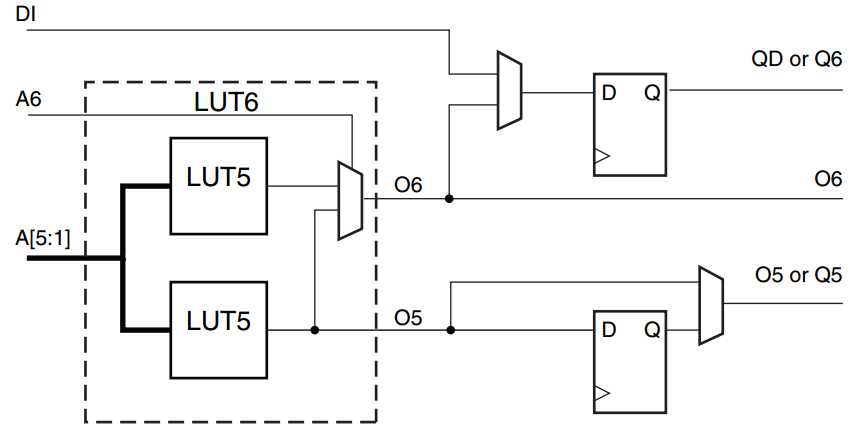

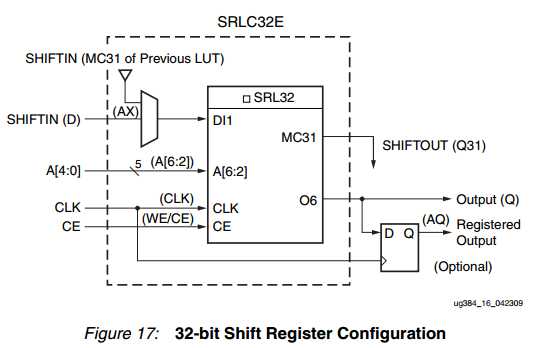

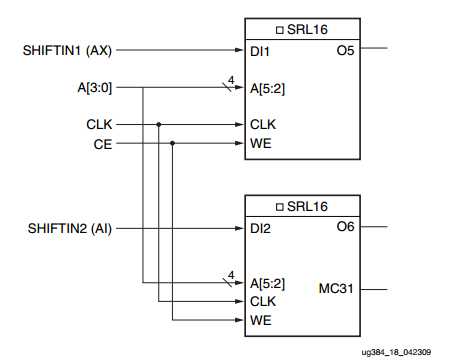

SliceM中的LUT可作为6输入1输出的LUT/相同5地址的双5输入2独立输出的LUT。同样可配置为64位/双32位(1个32位位移寄存器SRL32/2个可寻址的16位移寄存器SRL16s)的分布式RAM,在CLB中,每个LUT的输出可以及存在FF内。

简言之,SliceM可以作为查找表、触发器、宽位多路数据选择器、进位逻辑、分布式RAM、移位寄存器等。

SliceL

查找表、触发器、多路数据选择器、进位逻辑。

SliceX

查找表、触发器。

在SPANTAN-6中,一个Slice包含4个6输入LUT和8个FF以及多种逻辑。并包含SliceM(1/4),SliceL(1/4),SliceX(1/2)。(1个LS包含6.4个LC,故3758*6.4=24051.2个LC。

Q:Slice功能有哪些?

可以布局布线、可以做运算、等等,SliceM还可做RAM和位移寄存器。

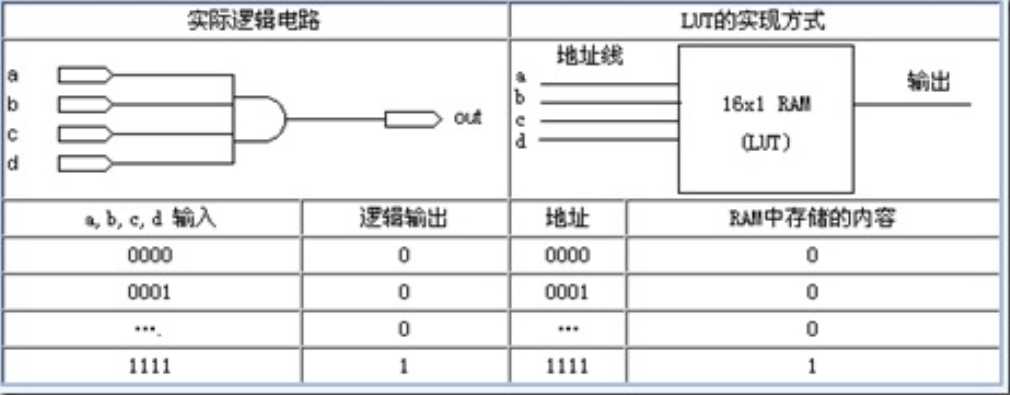

LUT---Look Up Table

查找表是最FPGA中实现逻辑的基本单元,通常有4输入查找表和6输入查找表(4/6 input LUT)。

以4输入查找表为例,可以看成4位地址输入,1位数据输出的存储器,存储的内容是真值表,依照输入的地址的真值输出对应的数据。

LUT是组合的,如果RTL是时序电路,则实际上是LUT+FF组成。

LUT就是一个4/6地址为的RAM。

Q:为什么是4/6输入?

因为对于多输入的信号处理的时候,就需要有多个LUT的级联来实现,而级联有不可避免的会导致延时过分,导致时序不满足。因此在实际的FPGA产品中多采用的是4输入或者6输入的LUT。(更快,满足时序)

LUT的重要作用-逻辑函数发生器:

Spartan-6中的函数生成器中,每个Slice中的四个函数生成器(A、B、C和D)有6个独立输入(A1-A6)和2个独立输出(O5-O6)。本质上,逻辑函数发生器存储的是真值表(Truth Table)的内容,而真值表则是通过布尔表达式获得。SPARTAN-6中函数生成器可以实现6输入布尔表达式(O6输出)或者5输入布尔表达式(O5和O6),只要这两个布尔表达式共享公共输入即可。

查找表的输出可以从O6直接输出,或者从AMUX, BMUX, CMUX, DMUX输出O5;O6输出也可进入专用异或门、O5也可进位逻辑链; O6输出进入进位逻辑多路复用器的选择线、或者存储单元的D输入;或者O6进入3输入D选择器。

布尔表达式:

从最基本的层次来说,所有的布尔表达式,不论它的长短如何,其值只能是true或false。

存储单元

Slice包含8个存储单元,有4个可以配置为由边沿触发的D触发器或者敏感锁存器,D触发器输入可由LUT输出直接触发或者经过一些门或者旁路Slice等;另外4个可配置为触发器由边沿触发的D触发器,但是当前4个锁存时不能使用。

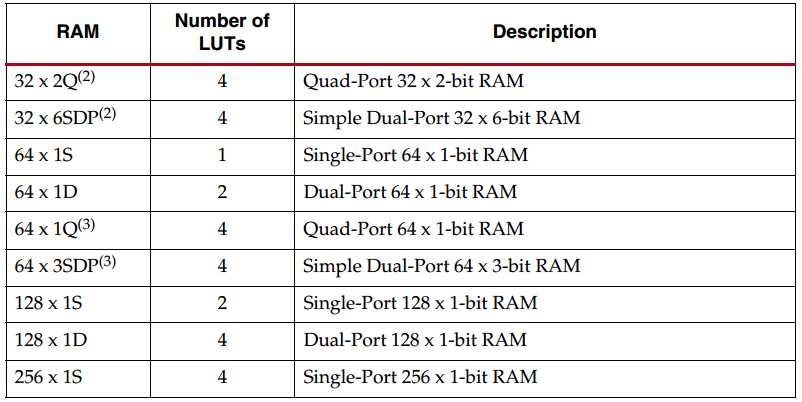

Distributed-RAM

分布式RAM,与块RAM相比消耗逻辑资源,即SliceM中的LUT。Distributed-RAM适合存储小型缓存数据、FIFO或寄存文件。对于大型存储需求使用块RAM。分布式RAM是同步写资源异步读资源,然而同步读资源可以通过添加一个FF在同一个Slice中实现,添加FF可以降低延迟。SliceM中的LUT可以通过多种组合方式来存储更多数据。

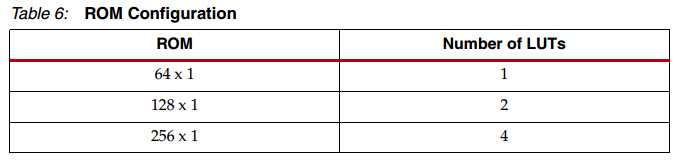

ROM

每个函数发生器可设置为64*1的ROM。

移位寄存器

SliceM中的函数发生器还可以配置为移位寄存器

数据选择器

4:1需要1个LUT; 8:1需要2个LUT; 16:1需要4个LUT

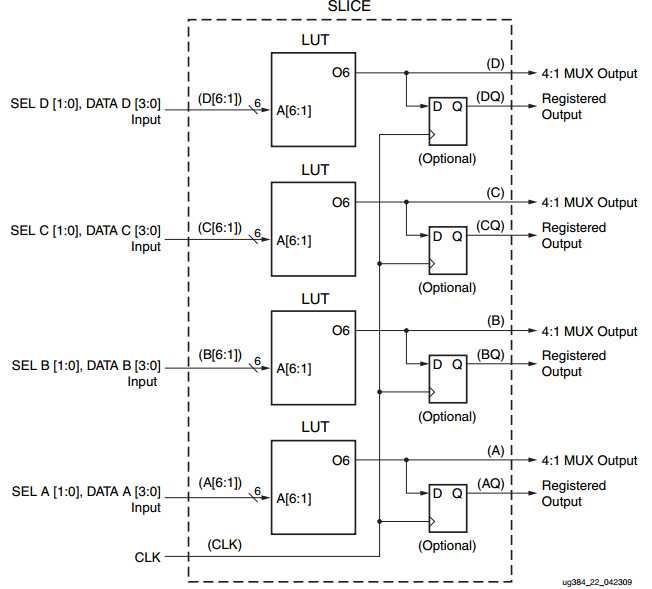

4:1选择器可以由Slice中的LUT和FF同时组成。

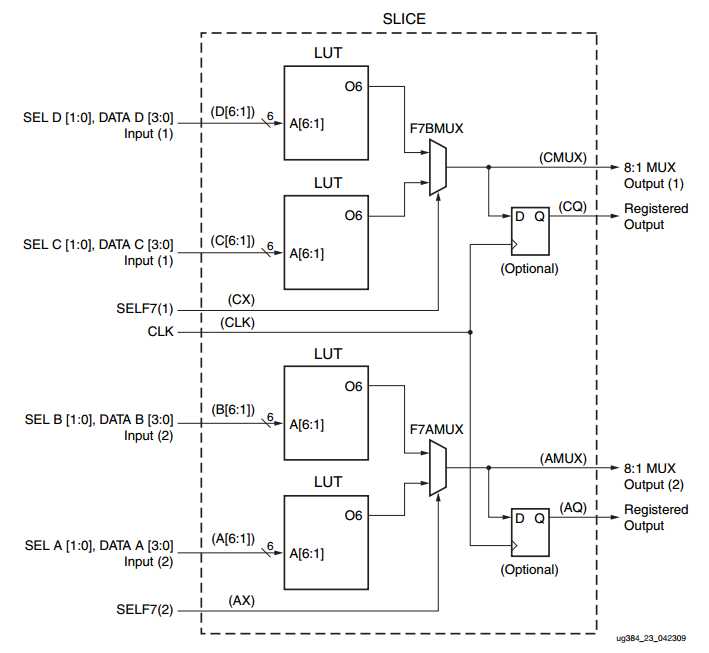

8:1选择器由Slice中的LUT、FF、三通道选择器组成,如下图。

快速超前进位逻辑

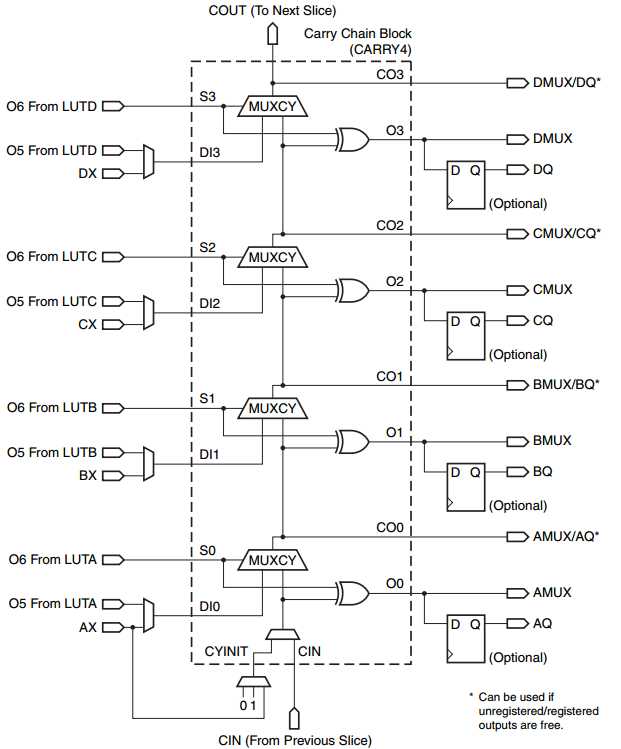

在SliceM&L中包含专用的进位逻辑,用于在一个片中执行快速算术加减法。每个CLB都有一个进位链,这些进位链可以级联形成更宽的加减逻辑。

每个Slice中向上的进位链的高度为4位。在每一位中都有一个进位选择器和一个专用异或门来对对应位的操作数进行加减。由图可见与LUT的重要作用-逻辑函数发生器相对应。

【基本知识】CLB、Slice、logic cell、LUT...

标签:特征 ant 加减法 介绍 cell 实现 64位 直接 手册

原文地址:https://www.cnblogs.com/yjw951012/p/12862746.html