标签:VID span div src 计算 配置 引入 width 频率

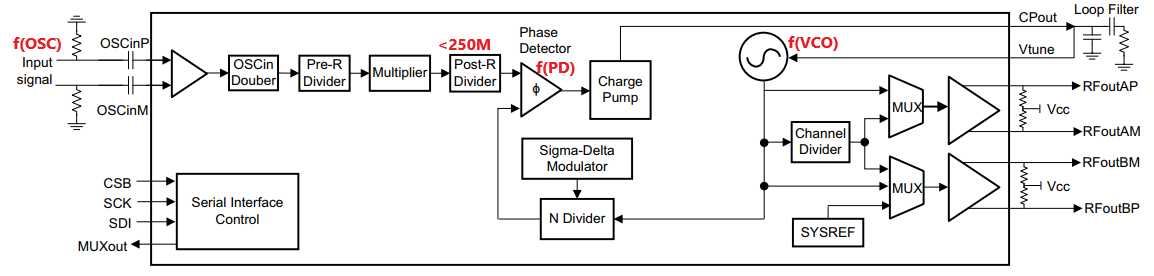

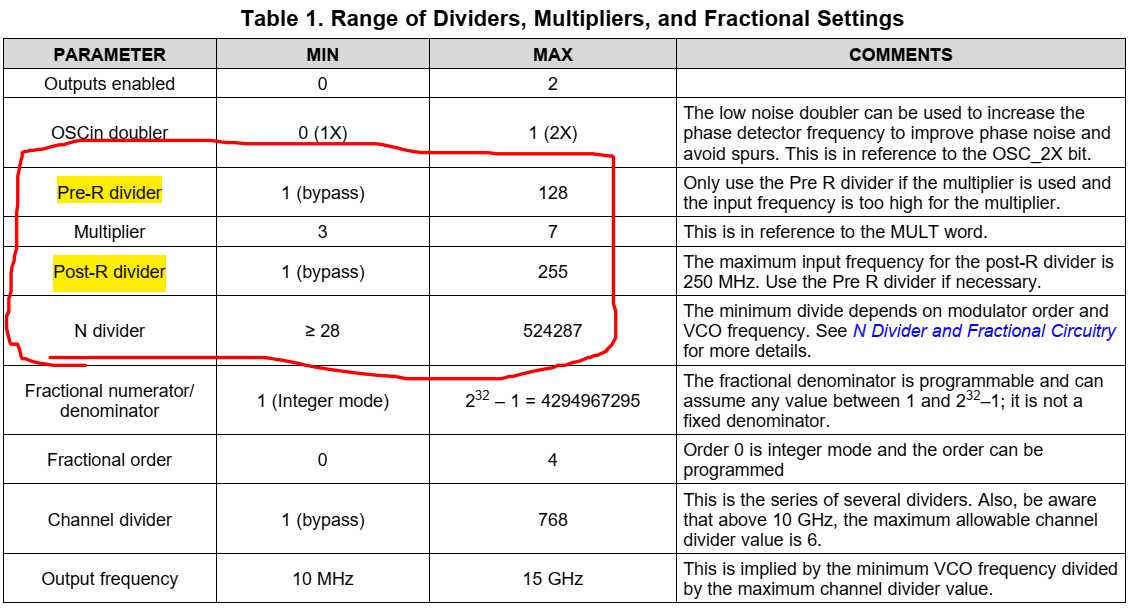

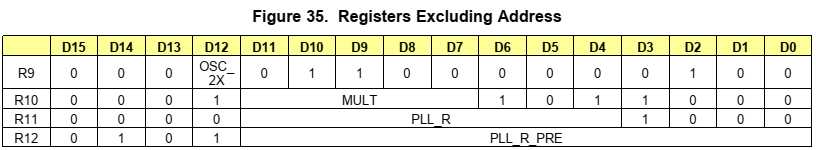

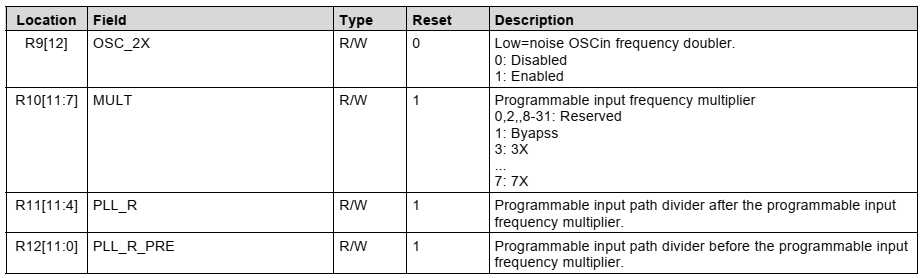

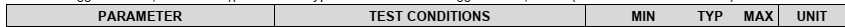

OSC_2X:2倍频

PLL_R_PRE:用于降低输入频率,限制PLL-R分频器最大250M的限制,其他情况不需要使用。

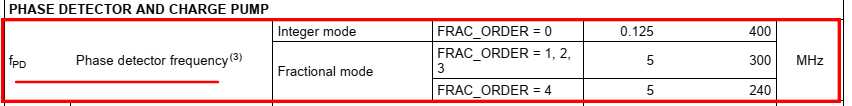

PLL_R:分频得到鉴相器频率fPD,输入进来的频率最大250Mhz

MULT:该方法对移相器的频率很有帮助,避免了整数边界激励,如果引入干净或者回路带宽较宽,将会降低锁相环的性能

注意频率范围:

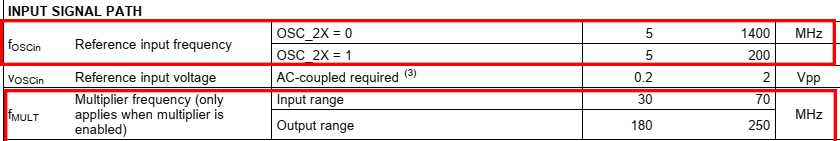

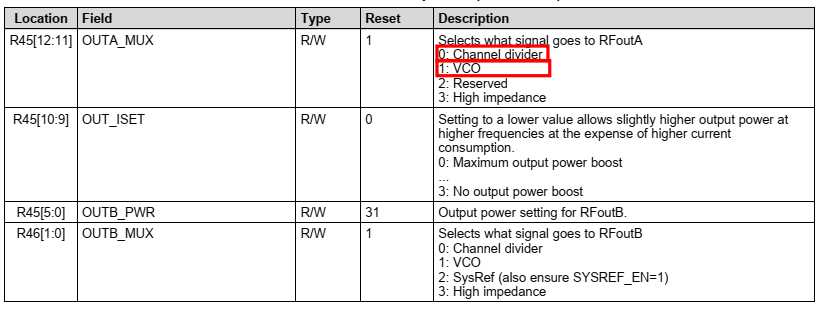

根据输出频率确定Chann Dvider各个寄存器的值以及VCO分频系数CHDIV,

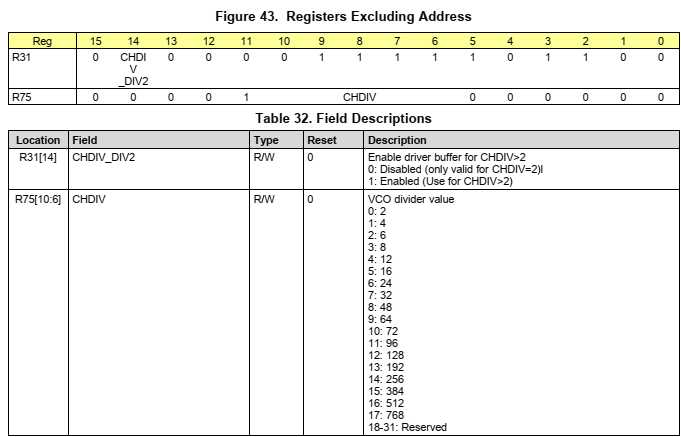

根据输出频率和上面的CHDIV,计算出fVCO

fVCO= RFout*CHDIV

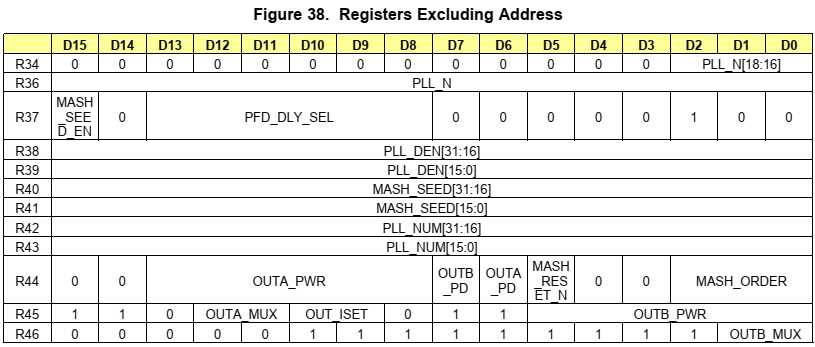

根据步骤1算出的fPD和步骤3算出的fVCO得出N Divider的整数和小数部分

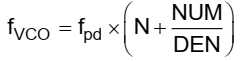

N Divider分成整数N和小数部分NUM/DEN

N:整数

NUM/DEN:小数,NUM范围1~(2^32)-1。DEN越大分辨率越高。当fPD=200Mhz,DEN=2^32时分辨率是200Mhz/2^32=0.047hz。

注意频率范围:

标签:VID span div src 计算 配置 引入 width 频率

原文地址:https://www.cnblogs.com/Mike2019/p/12880399.html