标签:功能 相同 efi 读取 start 并且 idt width height

使用FPGA向EEPROM写入0、1、2...255,再使用FPGA读取EEPROM 是否有这256个数据。

EEPROM是通过IIC协议进行通信的,以下对IIC通信协议分析:

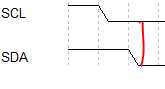

①start definition:

所以开始IIC时需要SCL和SDA都是0。

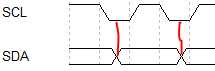

②数据稳定和数据变化:

从中可以看出SCL为1时,SDA稳定;SCL为0时,SDA改变。

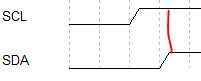

③stop definition:

因此结束时SCL和SDA都要是1。

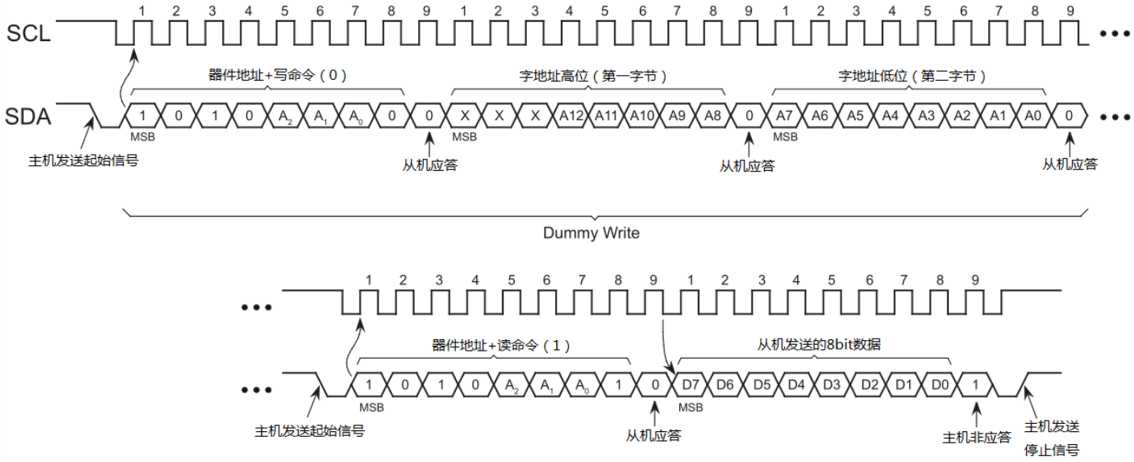

细化以上的时序图得到具体时序图如下:

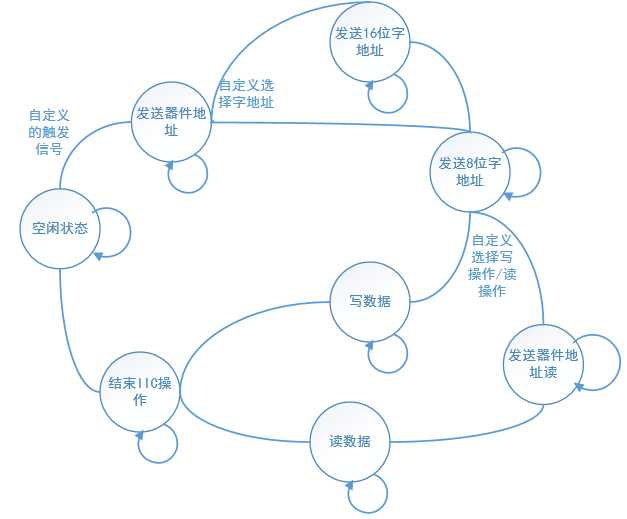

通过状态机来实现这张时序图。状态机分成三段式:状态转移、状态转移条件、状态输出。

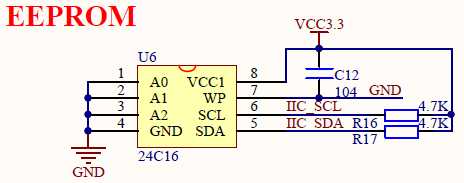

这个实验EEPROM的型号是AT24C64,根据数据手册得到原理图连接如下:

在FPGA芯片中设计了三个功能模块:eeprom_rw、i2c_dri、led_alarm。

eeprom_rw:用来向i2c_dri写入数据,并且读取i2c_dri中的数据。

i2c_dri:用来驱动IIC协议。

led_alarm:用来判断写的数据跟读的数据是否相同。

最后实战结束。

标签:功能 相同 efi 读取 start 并且 idt width height

原文地址:https://www.cnblogs.com/FPGAer/p/12907445.html