标签:基本 输出 tab ash strong 转换 png str 因此

建立时间Tsetup:时钟有效沿到来之前,数据需要保持稳定的时间,否则触发器无法锁存数据。

保持时间Thold:在时钟有效沿到来之后,数据需要保持稳定的时间,否则触发器无法锁存数据。

亚稳态semi-stable state:在数据的建立时间和保持时间中对信号进行采样,导致输出无法预测的状态。

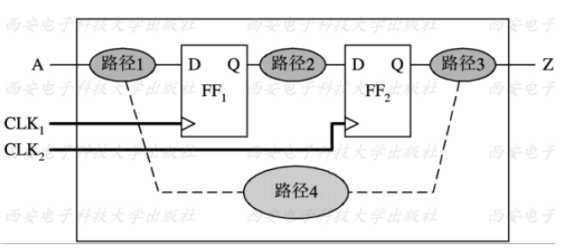

时序路径是点到点的数据通路,数据沿时序路径进行传输,每条时序路径有一个起点和终点。时序路径可以分为四条:输入端口到寄存器,寄存器到寄存器,寄存器到输出端口,输入端口到输出端口。详见《静态时序分析的基本概念和目的——3时序路径与关键路径》https://www.cnblogs.com/lizhiqing/p/12704545.html。

时序路径约束目的:约束时序路径是为了满足寄存器的建立时间和保持时间

数据从FF1的D端口传输至FF2的D端口,主要经历的时间是触发器的翻转时间/转换延时Tcq、寄存器与寄存器之间的组合逻辑延迟Tco、连线延迟等。

要求:数据经过上述延时(触发器的翻转时间/转换延时Tcq、寄存器与寄存器之间的组合逻辑延迟Tco、连线延迟)后到达FF2的D端口再加上FF2的建立时间需要小于一个时钟周期。

否则,若延时过大,在下一个cycle的有效沿到达时,FF1的数据仍在传输,则上一cycleFF1的输入数据无法在本cycle传递给FF2,数据可能无法满足建立时间导致无法更新。

对时钟进行建模后,上述延时(触发器的翻转时间/转换延时Tcq、寄存器与寄存器之间的组合逻辑延迟Tco、连线延迟)所允许的最大范围被确定。通过对时钟进行建模后,该路径的延时也被确定,DC将从单元库中选择单元来满足这些延时的约束,如果性能最好的单元仍无法满足建立时间要求,则DC会报错,需要重新修改设计(修改约束或修改代码)。

要求:数据经过上述延时后到达FF2的D端不能小于某个值,否则会导致FF2采样到FF1在本cycle的信号,导致FF2原应保存的FF1上个cycle的信号产生亚稳态。

保持时间一般能够满足,即传输延时一般大于触发器的保持时间;即使无法满足,可以在后盾版图设计的时候采用在路径添加缓冲器来增加延时。因此一般只注意建立时间,而不关注保持时间。

定义时钟(虚拟时钟除外),必须定义时钟周期(-period,下列表达式中10为一个周期的时长)和时钟源(get_port,下列表达式中clk为设计中的时钟端口);同时还允许定义可选项(option),如占空比(duty cycle),时钟偏移(offset/skew)和时钟名字(clock name)等,可通过 man create_clock查看相关命令。

create_clock -period 10 [get_ports clk]

路径1约束

路径3约束

路径4约束

####约束的作用:

对模块

##基本时序约束

###时序路径与关键路径

标签:基本 输出 tab ash strong 转换 png str 因此

原文地址:https://www.cnblogs.com/lizhiqing/p/12966424.html