标签:style blog http io color ar os sp for

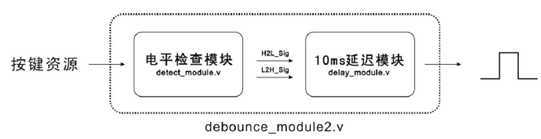

实验四和实验三的区别在于输出。实验三是检测到由高到低的电平变化时就拉高输出,检测到由低到高的电平变化时就拉低输出。而实验四检测到由高到低的电平变化时产生一个100ms的高脉冲。当检测到由低到高的电平变化时,只有消抖操作。

模块:

1 /*********************************************************** 2 module name: detect_module.v 3 function: detect pin‘s level change 4 5 by yf.x 6 2014-11-05 7 8 ************************************************************/ 9 10 module detect_module( 11 CLK, 12 RST_n, 13 Pin_in, 14 H2L_Sig, 15 L2H_Sig 16 ); 17 18 input CLK; 19 input RST_n; 20 input Pin_in; 21 output H2L_Sig; 22 output L2H_Sig; 23 24 /**************************************************************/ 25 //DE2-115 use 50MHz oscillator,50M*0.0001-1=4_999 26 parameter T100us=11‘d4999; 27 28 /**************************************************************/ 29 30 reg [10:0]count1; 31 reg isEn; 32 33 always @(posedge CLK or negedge RST_n) //100us timer 34 if(!RST_n) 35 begin 36 count1<=11‘d0; 37 isEn<=1‘b0; 38 end 39 else if(count1==T100us) 40 isEn<=1‘b1; 41 else 42 count1<=count1+1‘b1; 43 44 /***********************************************************/ 45 46 reg H2L_F1; 47 reg H2L_F2; 48 reg L2H_F1; 49 reg L2H_F2; 50 51 always @(posedge CLK or negedge RST_n) 52 if(!RST_n) 53 begin 54 H2L_F1<=1‘b1; 55 H2L_F2<=1‘b1; 56 L2H_F1<=1‘b0; 57 L2H_F2<=1‘b0; 58 end 59 else 60 begin 61 H2L_F1<=Pin_in; 62 H2L_F2<=H2L_F1; 63 L2H_F1<=Pin_in; 64 L2H_F2<=L2H_F1; 65 end 66 67 /*****************************************************/ 68 69 assign H2L_Sig=isEn?(!H2L_F1&H2L_F2):1‘b0; 70 assign L2H_Sig=isEn?(!L2H_F2&L2H_F1):1‘b0; 71 72 /*****************************************************/ 73 74 endmodule 75 76 77

1 /*************************************************** 2 module name: delay_module.v 3 function: delay 10ms. 4 5 by yf.x 6 2014-11-05 7 8 ***************************************************/ 9 10 module delay_module( 11 CLK, 12 RST_n, 13 H2L_Sig, 14 L2H_Sig, 15 Pin_out 16 ); 17 18 input CLK; 19 input RST_n; 20 input H2L_Sig; 21 input L2H_Sig; 22 output Pin_out; 23 24 /**************************************************/ 25 //5M*0.001-1=49_999 26 parameter T1ms=16‘d49_999; 27 28 /**************************************************/ 29 30 reg [15:0]count1; 31 32 always @(posedge CLK or negedge RST_n) 33 if(!RST_n) 34 count1<=16‘d0; 35 else if(iscount && count1==T1ms) 36 count1<=16‘d0; 37 else if(iscount) 38 count1<=count1+1‘b1; 39 else if(!iscount) 40 count1<=16‘d0; 41 42 /****************************************************/ 43 44 reg [6:0]count_ms; 45 46 always @(posedge CLK or negedge RST_n) 47 if(!RST_n) 48 count_ms<=7‘d0; 49 else if(iscount && count1==T1ms) 50 count_ms<=count_ms+1‘b1; 51 else if(!iscount) 52 count_ms<=7‘d0; 53 54 /*******************************************************/ 55 56 reg iscount; 57 reg rPin_out; 58 reg [1:0]i; 59 60 always @(posedge CLK or negedge RST_n) 61 if(!RST_n) 62 begin 63 iscount<=1‘b0; 64 rPin_out<=1‘b0; 65 i<=2‘d0; 66 end 67 else 68 case(i) 69 2‘d0: 70 if(H2L_Sig) 71 i<=2‘d1; 72 else if(L2H_Sig) 73 i<=2‘d3; 74 75 2‘d1: 76 if(count_ms==7‘d10) 77 begin 78 iscount<=1‘b0; 79 rPin_out<=1‘b1; 80 i<=2‘d2; 81 end 82 else 83 iscount<=1‘b1; 84 85 2‘d2: 86 if(count_ms==7‘d100) 87 begin 88 iscount<=1‘b0; 89 rPin_out<=1‘b0; 90 i<=2‘d0; 91 end 92 else 93 iscount<=1‘b1; 94 95 2‘d3: 96 if(count_ms==7‘d10) 97 begin 98 iscount<=1‘b0; 99 i<=2‘d0; 100 end 101 else 102 iscount<=1‘b1; 103 endcase 104 105 /**************************************************/ 106 107 assign Pin_out=rPin_out; 108 109 /**************************************************/ 110 111 endmodule 112 113 114 115

1 /**************************************** 2 module name: debounce_module.v 3 function: debounce a key 4 pin assignments(for DE2-115): 5 --------------------------------- 6 CLK----------------------CLOCK_50 7 RST_n--------------------KEY[0] 8 Pin_in-------------------KEY[3] 9 Pin_out------------------LEDG[3] 10 11 by yf.x 12 2014-11-05 13 14 ****************************************/ 15 16 module debounce_module( 17 CLK, 18 RST_n, 19 Pin_in, 20 Pin_out 21 ); 22 23 input CLK; 24 input RST_n; 25 input Pin_in; 26 output Pin_out; 27 28 /*******************************/ 29 30 wire H2L_Sig; 31 wire L2H_Sig; 32 33 detect_module u0( 34 .CLK(CLK), 35 .RST_n(RST_n), 36 .Pin_in(Pin_in), //input from top 37 .H2L_Sig(H2L_Sig), //output to u1 38 .L2H_Sig(L2H_Sig) //output to u1 39 ); 40 41 /***************************************/ 42 43 delay_module u1( 44 .CLK(CLK), 45 .RST_n(RST_n), 46 .H2L_Sig(H2L_Sig), //input from u1 47 .L2H_Sig(L2H_Sig), //input from u1 48 .Pin_out(Pin_out) //output to top 49 ); 50 51 /***************************************/ 52 53 endmodule

实验四说明:

实验四和实验三代码部分的区别在delay_module.v的case部分。

【黑金教程笔记之005】【建模篇】【Lab 04 消抖模块之二】—笔记

标签:style blog http io color ar os sp for

原文地址:http://www.cnblogs.com/halflife/p/4082782.html