标签:扩展 说明 方法 扩展程序 结构 情况下 存储器 避免 应用

MCS-51单片机片内集成了各种存储器和I/O功能部件,但有时根据应用系统的功能需求,片内的资源还不能满足需要,还需要外扩存储器和I/O功能部件(也称I/O接口部件),这就是通常所说的MCS-51单片机的系统扩展问题。

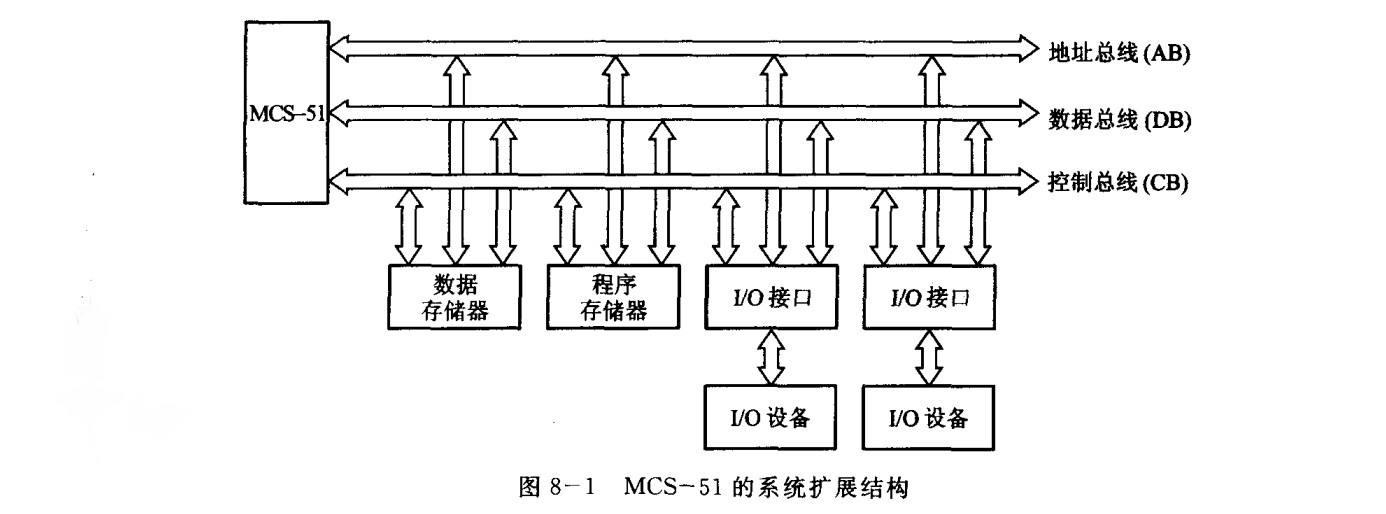

MCS-51系统扩展的内容主要有外部存储器的扩展(外部存储器又分为外部程序存储器和外部数据存储器)和I/O接口部件的扩展。本章介绍MCS-51单片机如何扩展外部存储器,有关I/O接口部件的扩展将在下一章介绍。MCS-51系统扩展结构如图8-1所示。

由图8-1可以看出:系统扩展是以MCS-51单片机为核心进行的。扩展内容包括扩展程序存储器(ROM)、数据存储器(RAM)、I/O接口部件及I/O设备等。

MCS-51单片机外部存储器结构,采用的是哈佛结构,即程序存储器的空间和数据存储器的空间是截然分开的。还有一种外部存储器的结构,它是程序存储器和数据存储器合用一个空间的结构:普林斯顿结构。例如,MCS-96单片机的存储器结构就是采用普林斯顿结构。

MCS-51单片机数据存储器和程序存储器的最大扩展空间各为64 KB,扩展后,系统形成了 2个并行的64 KB外部存储器空间。

由图8-1可以看出,扩展是通过系统总线进行的,通过总线把MCS-51单片机与各扩展部分连接起来,并进行数据、地址和控制信号的传送。因此,要进行系统扩展首先要构造系统总线。

所谓总线,就是连接计算机各部件的一组公共信号线。MCS-51使用的是并行总线结构,按其功能通常把系统总统分为三组,即:

由于单片机系统采用总线结构形式,可以大大减少单片机系统中传输线的数目,提高了系统的可靠性,增加了系统的灵活性。此外,总线结构也使扩展易于实现,各功能部件只要符合总线规范就可以很方便地接入系统,实现单片机的

系统扩展。

既然单片机的扩展系统是并行总线结构,因此单片机系统扩展的首要问题就是构造系统总线,然后再往系统总线上“挂”存储器芯片或I/O接口芯片,“挂”存储器芯片就是存储器扩展,“挂” I/O接口芯片就是I/O扩展。

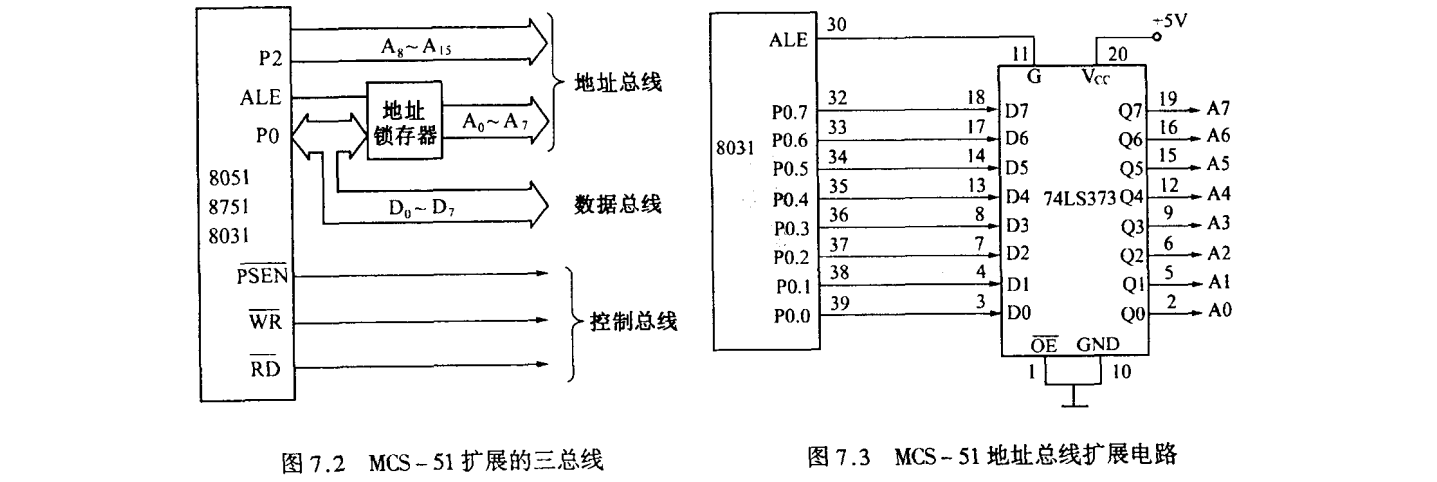

MCS-51单片机受引脚数目的限制,数据线和低8位地址线是复用的,而P0 口线兼用。为了将它们分离出来,以便同单片机片外的扩展芯片正确的连接,需要在单片机外部増加地址锁存器,从而构成与一毆CPU相类似的片外三总线,如图7.2所示。

地址锁存器一般采用74LS373,采用74LS373的地址总线的扩展电路如图7.3所示。

由MCS-51的P0 口送出的低8位有效地址信号是在ALE(地址锁存允许)信号变高的同时出现的,并在ALE由高变低时,将出现在P0 口的地址信号锁存到外部地址锁存器74LS373中,直到下一次ALE变高时,地址才发生变化,随后,P0 口又作为数据总线口。

下面说明总线的具体构造方法。

以P0 口作低8位地址/数据总线锁存器

因为P0 口即作低8位地址线,又作数据线(分时复用),因此,需要增加一个8位锁存器。在实际应用时,先把低8位地址送锁存器暂存,然后再由地址锁存器给系统提供低8位地址,而把P0 口线作为数据线使用。

实际上,MCS-51单片机的P0 口的电路设计已考虑了这种应用要求,P0口线内部电路中的多路转接电路MUX以及地址/数据控制就是为此目的而设计的。

以P2 口的口线作高位地址线

如果使用P2 口的全部8位口线,再加上P0 口提供的低8位地址,便可形成完整的16位地址总线,使单片机系统的寻址范围达到64KB。但在实际应用系统中,高位地址线并不固定为8位,需要用几位就从P2 口中引出几条口线。

控制值号线

除了地址线和数据线之外,在扩展系统中还需要一些控制信号线,以构成扩展系统的控制总线。这些信号有的是单片机引脚的第一功能信号,有的则是第二功能信号。其中包括:

可以看出,尽管MCS-51单片机有4个并行的I/O 口,共32条口线,但由于系统扩展的需要,真正作为数据I/O使用的,就剩下P1 口和P3 口的部分口线了。

外扩的RAM芯片既能读出又能写人,所以通常都有读写控制引脚,记为OE和WE。外扩RAM的读写控制引脚分别与MCS-51的RD和WR引脚相连。

外扩的EPROM在正常使用中只能读出,不能写入,故EPROM芯片没有写入控制引脚,只有读出引脚,记为OE,该引脚与MCS-51单片机的歯J引脚相连。

在实际的单片机应用系统设计中,即需要扩展程序存储器,往往又需要扩展数据存储器。在MCS-51扩展多片的程序存储器、数据存储器芯片的情况下,如何把外部各自的64KB的空间分配给各个芯片,并且使程序存储器的各个芯片之间、数据存储器(I/O接口芯片也作为数据存储器一部分)各芯片之间,地址不能发生重叠,以使单片机读、写外部存储器时,避免发生数据冲突。这就是存储器的地址空间的分配问题。存储器的地址空间分配,实际上就是使用系统提供的地址线,通过适当连接,最终达到一个存储器单元只对应一个地址的要求。

MCS-51通过地址总线发出的地址是用来选择某一个存储器单元,在外扩的多片存储器芯片中,MCS-51要完成这种功能,必须进行两种选择:一是必须选中该存储器芯片(或I/O接口芯片),这称为片选。只有被“选中”的存储器芯片才能被MCS-51读出或写入数据。二是必须选择出该芯片的某一单元,称为单元选择。为了芯片选择(片选)的需要,每个存储器芯片都有片选信号引脚,因此芯片的选择的实质就是如何通过MCS-51的地址线来产生芯片的片选信号。

通常把单片机系统的地址笼统地分为低位和高位地址,存储器芯片的某一存储单元选择使用低位地址,剩下的高位地址才作为芯片选择使用,因此芯片的选择都是使用高位地址线。实际上,在16位地址线中,高、低位地址线的数目并不是固定的,我们只是把用于存储单元选择所使用的地址线,都称为低位地址线,剩下多少就有多少高位地址线。存储器地址空间分配除了考虑地址线的连接外,还讨论各存储器芯片在整个存储空间中所占据的地址范围,以便在程序设计时正确地使用它们。常用的存储器地址分配的方法有两种:线性选择法(简称线选法)和地址译码法(简称译码法),下面分别予以介绍。

线选法就是直接利用系统的高位地址线作为存储器芯片(或I/O接口芯片)的片选信号。为此,只需把用到的高位地址线与存储器芯片的片选端直接连接即可。线选法的优点是电路简单,不需要地址译码器硬件,体积小,成本低。缺点是可寻址的器件数目受到限制,故只用于不太复杂的系统中。另外,地址空间不连续,每一个存储单元的地址不唯一,这会给程序设计带来一些不方便。

下面通过一个具体例子,来说明线选法的具体应用。

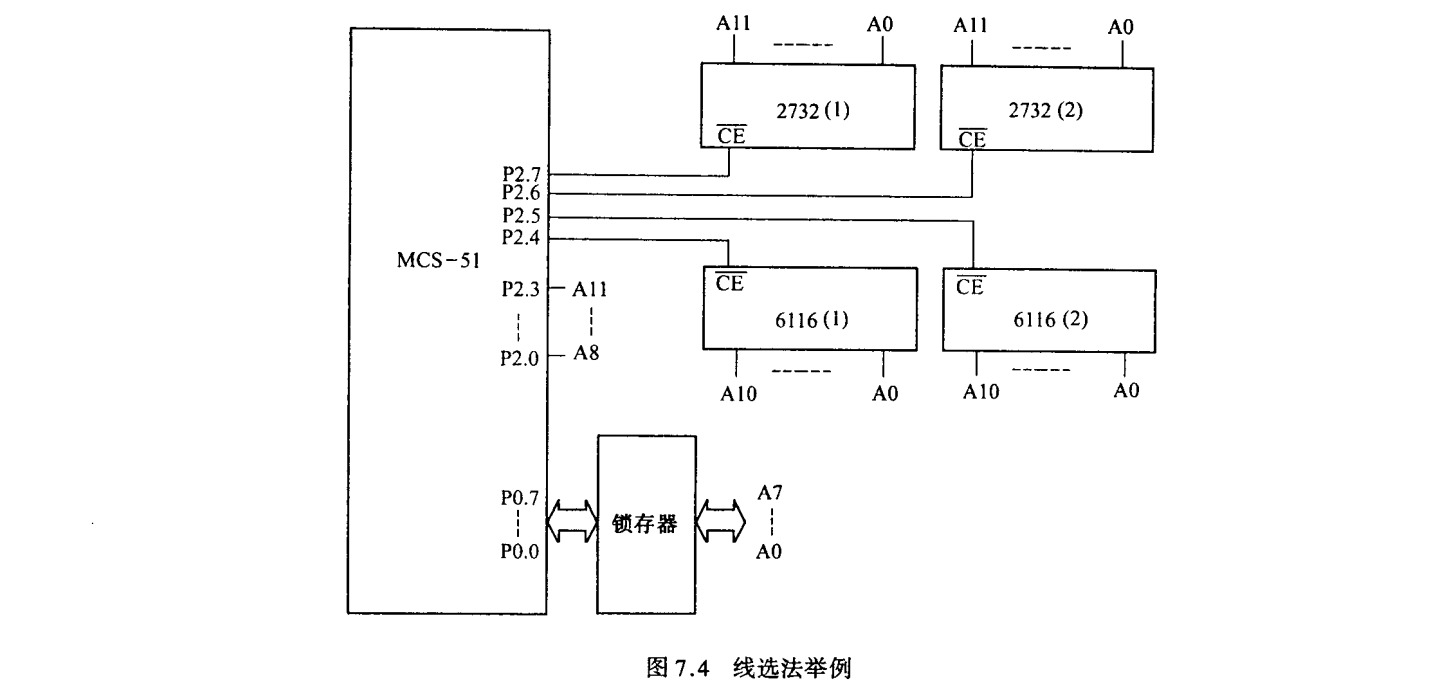

假设某一单片机系统,需要外扩8KB的EPR0M(2片2732),4KB的RAM(2片6116),这些芯片与MCS -51单片机的接口电路如图7.4所示,这里只画出与地址分配有关的地址线连线。

先看程序存储器2732与MCS-51的连接。由于2732是4KB的程序存储器,有12根地址线A11 ~ A0,它们分别与单片机的P0 口及P2.0-P2.3相连,从而实现4K字节单元的选择。电于系统中有2片程序存储器,存在2片程序存储器芯片之间相区别的问题,2732(1)片选CE接A15(P2.7),2732(2)片选端赤接A14(P2.6),当要选中某个芯片时,单片机P2 口对应的片选信号引脚应为低电平,其它引脚一定要为高电平。这样才能保证一次只选中一片,而不会再选中其它同类存储器芯片,这就是所谓的线性选址法,简称线选法。

再来看数据存储器与单片机的接口。数据存储器也有2片芯片需要区别。这里用P2.5和P2.4分别作为这2片芯片的片选信号。当要选中某个芯片时,单片机P2 口对应的片选信号引脚应为低电平,其它引脚一定要为高电平。由于6116是2KB的,需要11根地址线作为存储单元的选择,而剩下的P2 口线(P2.4-P2.7)正好作为片选线。

从图7.4中可以看出,程序存储器2732的低2KB和数据存储器6116的地址是重叠的。那么会不会MCS-51发出访问2732某个单元的地址时,同时也会选中6116的的某个单元,这样MCS-51就会同时选中两个单元,从而发生数据冲突,产生错误呢?

这种情况,完全不用担心,虽然两个单元的地址是一样的,但是MCS-51发给两类存储器的控制信号是不一样的。如果访问的是程序存储器,则是PSEN信号有效;如果访问的是数据存储器,则是RD或WR信号有效。以上控制信号是由MCS-51执行访问外部程序存储器或访问外部数据存储器的指令产生,任何时刻只能执行一种指令,产生一种控制信号,所以不会产生数据冲突的问题。

通过上面的讨论,可以得出一个重要的结论:MCS-51单片机外扩程序存储器和数据存器的地址空间可以重叠,只是注意程序存储器和程序存储器之间,数据存储器和数据存储器之间,千万不要发生地址重叠。现在再来看两个程序存储器的地址范围。

译码法就是使用译码器对MCS-51的高位地址进行译码,译码器的译码输出作为存储器芯片的片选信号。这是一种最常用的存储器地址分配的方法,它能有效的利用存储器空间,适用于大容量多芯片的存储器扩展。

译码电路可以使用现成的译码器芯片。最常用的译码器芯片有:74LS138(3- 8译码器)7415139(双2-4译码器)7415154(4- 16译码器),它们的CMOS芯片分别为:74HC138、74HC139、74HC154。它们使用灵活,完全可根据设计者的要求来组合译码,产生片选信号。

若全部地址都参加译码,称为全译码;若部分地址参加译码,称为部分译码,部分译码存在着部分存储器地址空间相重叠的情况。

标签:扩展 说明 方法 扩展程序 结构 情况下 存储器 避免 应用

原文地址:https://www.cnblogs.com/lihello/p/12983921.html