标签:style blog http io color ar os sp for

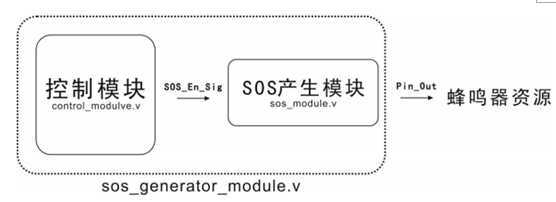

sos_module.v是产生SOS信号的功能模块。即有次序的输出莫斯码:点、画、间隔。control_module.v是一个定时触发器,每一段时间使能sos_module.v。

模块:

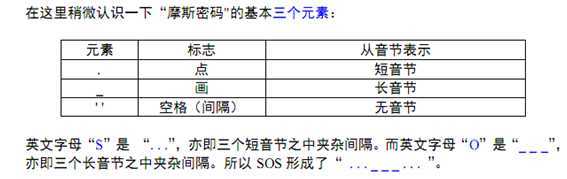

1 /********************************************************** 2 module name:sos_module.v 3 function: generate sos signal 4 5 by yf.x 6 2014-11-07 7 8 **********************************************************/ 9 10 module sos_module( 11 CLK, 12 RST_n, 13 Pin_out, 14 SOS_en_sig 15 ); 16 17 input CLK; 18 input RST_n; 19 input SOS_en_sig; 20 output Pin_out; 21 22 /***********************************************************/ 23 // DE2-115 use 50MHz oscillator,50M*0.001-1=49_999 24 parameter T1ms=16‘d49_999; 25 26 /**********************************************************/ 27 28 reg [15:0]count1; //1ms counter 29 30 always @(posedge CLK or negedge RST_n) 31 if(!RST_n) 32 count1<=16‘d0; 33 else if(iscount && count1==T1ms) 34 count1<=16‘d0; 35 else if(iscount) 36 count1<=count1+1‘b1; 37 else if(!iscount) 38 count1<=16‘d0; 39 40 /***********************************************************/ 41 42 reg [9:0]count_ms; 43 44 always @(posedge CLK or negedge RST_n) 45 if(!RST_n) 46 count_ms<=10‘d0; 47 else if(iscount && count1==T1ms) 48 count_ms<=count_ms+1‘b1; 49 else if(!iscount) 50 count_ms<=10‘d0; 51 52 /***********************************************************/ 53 54 reg iscount; 55 reg rPin_out; 56 reg [4:0]i; 57 58 always @(posedge CLK or negedge RST_n) 59 if(!RST_n) 60 begin 61 iscount<=1‘b0; 62 rPin_out<=1‘b0; 63 i<=5‘d0; 64 end 65 else 66 case(i) 67 68 5‘d0: 69 if(SOS_en_sig==1‘b1) 70 i<=5‘d1; 71 72 5‘d1, 73 5‘d3, 74 5‘d5, 75 5‘d13, 76 5‘d15, 77 5‘d17: //short 78 if(count_ms==10‘d100) 79 begin 80 iscount<=1‘b0; 81 rPin_out<=1‘b0; 82 i<=i+1‘b1; 83 end 84 else 85 begin 86 iscount<=1‘b1; 87 rPin_out=1‘b1; 88 end 89 90 5‘d2, 91 5‘d4, 92 5‘d6, 93 5‘d8, 94 5‘d10, 95 5‘d12, 96 5‘d14, 97 5‘d16, 98 5‘d18: //interval 99 if(count_ms==10‘d50) 100 begin 101 iscount<=1‘b0; 102 i<=i+1‘b1; 103 end 104 else 105 iscount<=1‘b1; 106 107 5‘d7, 108 5‘d9, 109 5‘d11: //long 110 if(count_ms==10‘d300) 111 begin 112 iscount<=1‘b0; 113 rPin_out<=1‘b0; 114 i<=i+1‘b1; 115 end 116 else 117 begin 118 iscount<=1‘b1; 119 rPin_out=1‘b1; 120 end 121 122 5‘d19: //end 123 begin 124 rPin_out<=1‘b0; 125 i<=1‘b0; 126 end 127 endcase 128 129 /*******************************************************************/ 130 131 assign Pin_out=rPin_out; 132 133 endmodule 134 135 136 137 138

1 /************************************************************ 2 module name:control_module.v 3 function:generate a enable signal at each 3 second. 4 5 by yf.x 6 2014-11-07 7 8 ************************************************************/ 9 10 module control_module( 11 CLK, 12 RST_n, 13 SOS_en_sig 14 ); 15 16 input CLK; 17 input RST_n; 18 output SOS_en_sig; 19 20 /***********************************************************/ 21 // 50MHz*3S-1=149_999_999 22 parameter T3s=28‘d149_999_999; 23 24 /***********************************************************/ 25 26 reg isEn; 27 reg [27:0] count1; 28 29 always @(posedge CLK or negedge RST_n) 30 if(!RST_n) 31 begin 32 isEn<=1‘b0; 33 count1<=28‘d0; 34 end 35 else if(count1==T3s) 36 begin 37 isEn<=1‘b1; 38 count1<=28‘d0; 39 end 40 else 41 begin 42 isEn<=1‘b0; 43 count1<=count1+1‘b1; 44 end 45 46 /************************************************************/ 47 48 assign SOS_en_sig=isEn; 49 50 /************************************************************/ 51 52 endmodule 53 54

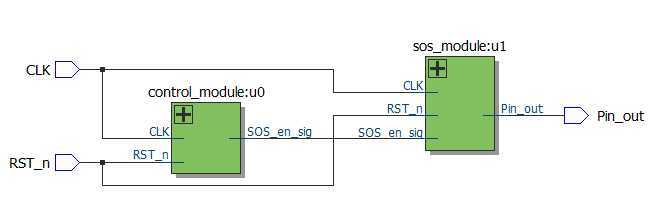

1 /******************************************************************** 2 module name: sos_generator_module.v 3 function: top module. 4 5 pin assignmets(for DE2-115): 6 -------------------------------------------------- 7 CLK----------------------------------CLOCK_50 8 RST_n--------------------------------KEY[0] 9 Pin_out------------------------------LEDG[8] 10 -------------------------------------------------- 11 12 by yf.x 13 2014-11-07 14 15 ********************************************************************/ 16 17 module sos_generator_module( 18 CLK, 19 RST_n, 20 Pin_out 21 ); 22 23 input CLK; 24 input RST_n; 25 output Pin_out; 26 27 /*********************************************************************/ 28 29 wire SOS_en_sig; 30 31 control_module u0( 32 .CLK(CLK), 33 .RST_n(RST_n), 34 .SOS_en_sig(SOS_en_sig) 35 ); 36 37 wire pin_out_wire; 38 39 sos_module u1( 40 .CLK(CLK), 41 .RST_n(RST_n), 42 .SOS_en_sig(SOS_en_sig), 43 .Pin_out(pin_out_wire) 44 ); 45 46 /********************************************************************/ 47 48 assign Pin_out=pin_out_wire; 49 50 /********************************************************************/ 51 52 endmodule

模块框图:

实验五说明:

实验五中control_module.v每隔3秒产生一个使能信号,触发sos_module.v产生sos信号。

【黑金教程笔记之006】【建模篇】【Lab 06 SOS信号之一】—笔记

标签:style blog http io color ar os sp for

原文地址:http://www.cnblogs.com/halflife/p/4082789.html