标签:信号 strong spl inpu inf 时序 img module display

一般来说,同步系统,都使用异步复位。这是因为同步复位的电路实现,比异步复位的电路实现,要浪费更多电路资源。

工程实践中,确实见过由于未做异步复位的同步处理,而出现大概率系统死机现象(复位的作用域是很大的)。

1.什么是异步复位

在带有复位端的D触发器中,当reset信号“复位”有效时,它可以直接驱动最后一级的与非门,令Q端“异步”置位为“1”or“0”。这就是异步复位。

当这个复位信号release时,Q的输出由前一级的内部输出决定(D端口)。

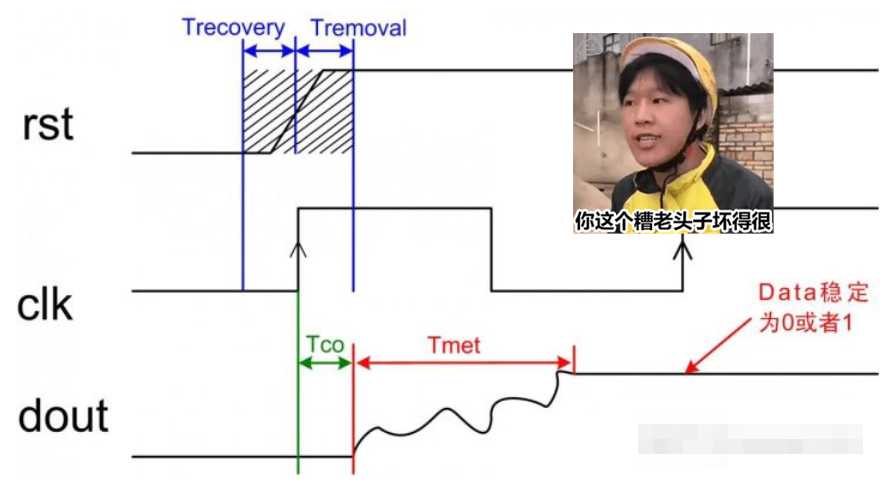

2.复位信号的恢复时间T( recovery time ):

原本有效的复位信号释放(对于低电平有效的复位信号指上升沿),与紧跟其后的第一个时钟上升沿之间的最小时间。

这个时间的意义是,如果保证不了这个最小恢复时间,也就是说这个异步控制信号的解除与“下个时钟沿”离得太近(但在这个时钟沿之前),没有给寄存器留有足够时间来恢复至正常状态,那么就不能保证“下个时钟沿”能正常作用,也就是说这个“时钟沿”可能会失效。

3.复位信号的移除时间T(recovery time):

时钟信号的上升沿,与紧跟其后异步复位信号从有效到无效的最小时间。

这个时间的意义是,如果保证不了这个去除时间,也就是说这个异步控制信号的解除与“有效时钟沿”离得太近(但在这个时钟沿之后),那么就不能保证有效地屏蔽这个“时钟沿”,也就是说这个“时钟沿”可能会起作用。

4.恢复与移除时间的意义

如果你想让某个时钟沿起作用,那么你就应该在“恢复时间”之前是异步控制信号变无效,如果你想让某个时钟沿不起作用,那么你就应该在“去除时间”过后使控制信号变无效。如果你的控制信号在这两种情况之间,那么就没法确定时钟沿是否起作用或不起作用了,也就是说可能会造成寄存器处于不确定的状态。而这些情况是应该避免的。所以在复位信号的处理上,要遵守恢复时间和去除时间。

如下图异步复位时序所示,为复位电路复位时序图。如果异步复位信号的撤销时间在Trecovery(恢复时间)和Tremoval(移除时间)之内,那势必造成亚稳态的产生,输出在时钟边沿的Tco后会产生振荡,振荡时间为Tmet(决断时间),最终稳定到“0”或者“1”,就会可能造成复位失败。

5.总结

异步复位信号亚稳态的原因

复位结束也就是释放的时刻,恰在时钟上升沿的建立时间和保持时间之间时,无法决定现在的复位状态是1还是0,造成亚稳态。

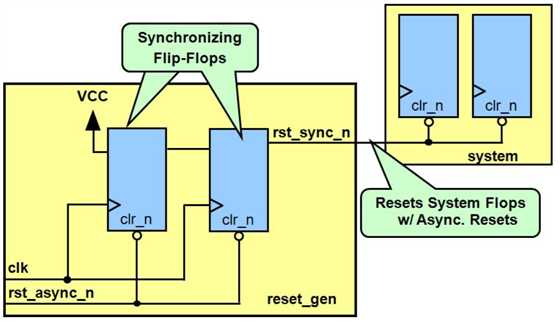

1.电路结构

异步复位:显而易见,rst_async_n异步复位后,rst_sync_n将拉低,即实现异步复位。

同步释放:这个是关键,看如何实现同步释放,即当复位信号rst_async_n撤除时,由于双缓冲电路(双寄存器)的作用,rst_sync_n复位信号不会随着rst_async_n的撤除而撤除。

假设rst_async_n撤除时发生在clk上升沿,如果不加此电路则可能发生亚稳态事件,但是加上此电路以后,假设第一级D触发器clk上升沿时rst_async_n正好撤除,则D触发器1输出高电平“1”,此时第二级触发器也会更新输出,但是输出值为前一级触发器clk来之前时的Q1输出状态。显然Q1之前为低电平,因此第二级触发器输出保持复位低电平,直到下一个clk来之后,才随着变为高电平。即同步释放。

2.代码实现

1 module reset_gen ( output rst_sync_n, input clk, rst_async_n); 2 reg rst_s1, rst_s2; 3 wire rst_sync_n ; 4 5 always @ (posedge clk, posedge rst_async_n) 6 if (rst_async_n) 7 begin 8 rst_s1 <= 1‘b0; 9 rst_s2 <= 1‘b0; 10 end 11 else 12 begin 13 rst_s1 <= 1‘b1; 14 rst_s2 <= rst_s1; 15 end 16 17 assign rst_sync_n = rst_s2; //注意这里的rst_sync_n才是我们真正对系统输出的复位信号 18 19 endmodule

标签:信号 strong spl inpu inf 时序 img module display

原文地址:https://www.cnblogs.com/streetlive/p/12994120.html