标签:大小端 设计 code 第二部分 designed risc undefined lis system

0、为什么要推出ARM汇编 ? 0.1 对比X86,8051汇编,从更底层的角度去理解相关的知识的 ?

1、ARM分类 ? 参考官方:http://infocenter.arm.com/ ? 1.1版本号分类 ? ARM7 ARM9 ARM11 cortex系列:

Cortex-R

Cortex-M MO M3 M4 M7 ? Cortex-A A8 A9 A15A72 A53

1.2 指令集分类(指令集原则上是向下兼容的)ARMV4 ARMV7 ARMV8

2、ARM商业模式及半导体公司

2.1 IP核(知识产权)

ARM MIPS X86 PowerPC(IBM)

ARM出卖IP而不卖芯片的策略

2.2 半导体公司 三星、高通、苹果、NXP(Freescale)、TI、ST、ATMEL、Ambarella MTK、海思、全志、瑞芯微、展讯(基带)、炬力、联咏 例如:S3C2440(ARM9)EXYNOS4412(Cortex-A9) STM32F103(Cortex-M3) i.MX.RT1050(Cortex-M7) i.MX.283(ARM9) AT89C51(8051核) AR9331(MIPS) HI3518(ARM9) NT96650(MIPS)--网络摄像头 A33(Cortex-A7) RK3399(Cortex-A72 A53)--利用了Arm big.LITTLE compatible技术

2.3 生态系统:核公司---半导体公司---半导体生产(台积电等)----产品研发---产品生产 作为个体:半导体行业,产品应用行业 方案选型-调试Demo板-打样生产 (通用方案与专用方案)

3、嵌入式处理器

CPU、MCU、GPU、PLC、DSP、SOC、ASIC、FPGA的关系

CPU包含运算器和控制器

MCU最简单的理解就是一个芯片就是一个微型计算机

GPU包含很多个运算器,专门解决图形计算 PLC半成品工控设备

soc片上系统,专用/通用软件和硬件系统(ESP8266【wifi芯片】)

ASIC专用集成电路,IP核设计(软核/硬核/固核)

DSP处理大量数据运算,一般用于音视频计算上。

EPGA解决程序滞后性问题,并行计算 比如:一个产品上可以同时包含MCU,GPU,SOC,ASIC,DSP,FPGA

哈佛结构与冯式结构

ARM的处理器状态和处理器模式

ARM内部寄存器及SFR

ARM异常处理

ARM的存储系统(大小端及对齐问题)

CISC与RISC(指令特点)

开发工具

寻址方式

指令分类

ARM汇编程序格式

程序控制

ARM汇编与C的混合编程

ARM汇编THUMB2指令集

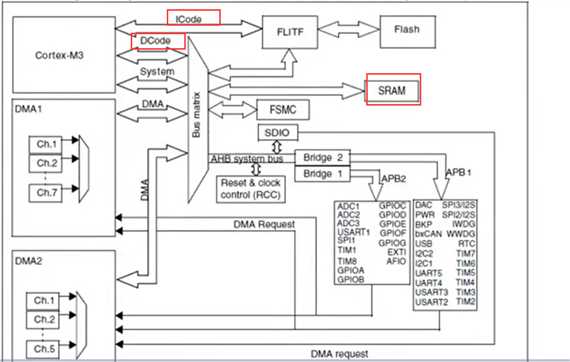

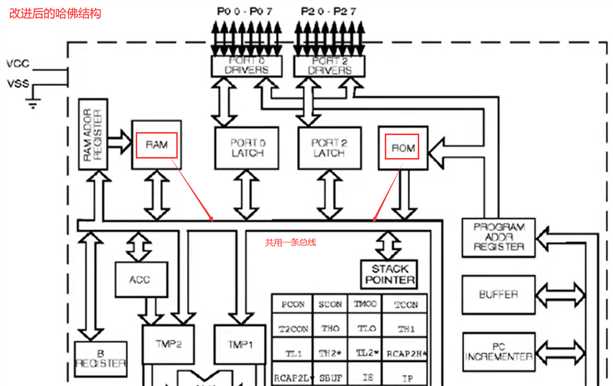

2.11 两者的区别: ? 哈弗结构:独立的存储架构和信号通道(代码与数据是否统一编址) ? 与是否统一编址没有关系,也与CPU没有关系,与计算机整体设计有关 ? CACHE的引入(CPU内部哈佛结构) ? 8086冯式结构 相同存储(RAM)相同的通道 (统一编址) 区别:运行态与存储态 ? STM32F103哈弗结构 不同的存储(ROM/RAM)不同的通道 (统一编址)

8051改进型的哈弗结构 不同的存储(ROM/RAM)相同的通道 (独立编址)

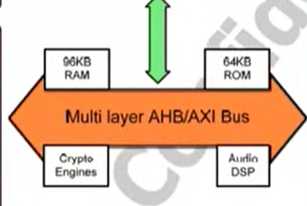

ARM9改进型的冯式结构 相同的存储(RAM)/不同的通道 (统一编址) ? 总结:高性能单片机:冯式结构 普通单片机:哈弗结构

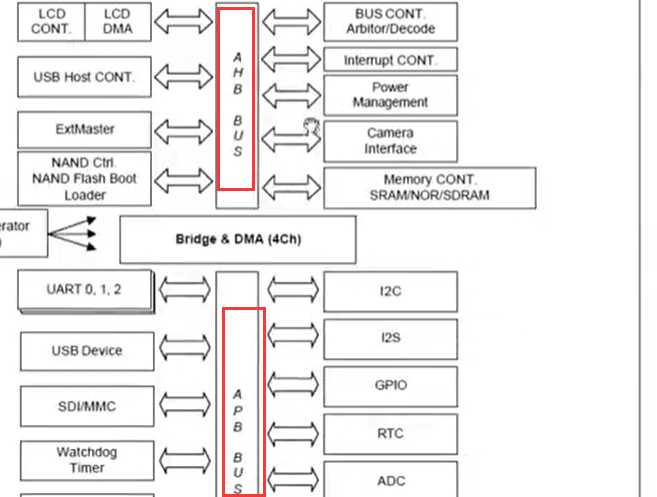

2.1.2 总线与I0访问 ARM总线结构(AHB【高速总线】,APB【一般的总线】,AXI【arm自己研发的总线】)与内部外设

(系统)总线访问与Io访问(独立与统一) IO就是指CPU的各种内部与外部外设 Io接口的编址方式:Io接口中能被CPU访问的寄存器称为端口/寄存器 端口与存储器统一编址(ARM)uart gpio 端口与存储器独立编址(X86)8259A8255(并口)8253(定时器) 通过MEMR/MEMW和IOR/IOW两组控制信号来实现对I/o端口和存储器的不同寻址 注意:内存(memory map)与内存条,内存条只是内存的一部分

意:在不同的体系下一些概念有所不同,在这里我们使用S3C2440手册进行参考

| ARMV4 | ARMV7 | ||

|---|---|---|---|

| ARM状态 | 执行效率高 | 32bit | 32bit |

| THUMB状态 | 代码密度好 | 16bit | 16/32bit(THUMBEE状态) |

处理器状态的切换 BX BLX 各种指令:ARM指令(32位),THUMB指令(16位),THUMB2指令(32/16位) CORTEX-M只是指令THUMB2指令子集

usr,fiq,irq,svc,abt,sys,und usr(用户模式):The normal ARM program execution state fiq(快速中断):Designed to support a data transfer or channel process irq(中断):Used for general-purpose interrupt handling svc(保护模式):Protected mode for the operating system

abt(异常):Entered after a data or instruction prefetch abort sys(用户特权模式):A privileged user mode for the operating system und(未定义):Entered when an undefined instruction is executed 设计的目的:提高响应速度,注意:保护模式/特权模式,需要MWU和代码支持

每条指令五个工位:取指--译码--执行--访存--回写

| t1 | t2 | t3 | t4 | t5 | t6 | ||||

|---|---|---|---|---|---|---|---|---|---|

| 指令1 | 取指 | 译码 | 执行 | 防存 | 回写 | ||||

| 指令2 | 取指 | 译码 | 执行 | 防存 | 回写 | ||||

| 指令3 | 取指 | 译码 | 执行 | 防存 | 回写 | ||||

| 指令4 | 取指 | 译码 | 执行 | 防存 | 回写 | ||||

| 指令5 | 取指 | 译码 | 执行 | 防存 | 回写 |

结论:程序指针PC=执行指令地址+8

标签:大小端 设计 code 第二部分 designed risc undefined lis system

原文地址:https://www.cnblogs.com/nieaojie625/p/13083264.html