标签:png code sed 编码器 examples amp html 写法 reg

首先,实现可以参考这篇博客

https://www.cnblogs.com/yllinux/p/7065331.html

我的代码跟网上的是一样的,师兄给出了其他写法,有空再补。

module coder_83( input [7:0] data_in, input en_in_n, output reg [2:0] code_out, output reg en_out, output reg state ); always@(en_in_n or data_in) begin if(en_in_n) begin code_out <= 3‘b111; en_out <= 1; state <= 1; end else if (data_in[7] == 0) begin code_out <= 3‘b000; en_out <= 1; state <= 0; end else if (data_in[6] == 0) begin code_out <= 3‘b001; en_out <= 1; state <= 0; end else if (data_in[5] == 0) begin code_out <= 3‘b010; en_out <= 1; state <= 0; end else if (data_in[4] == 0) begin code_out <= 3‘b011; en_out <= 1; state <= 0; end else if (data_in[3] == 0) begin code_out <= 3‘b100; en_out <= 1; state <= 0; end else if (data_in[2] == 0) begin code_out <= 3‘b101; en_out <= 1; state <= 0; end else if (data_in[1] == 0) begin code_out <= 3‘b110; en_out <= 1; state <= 0; end else if (data_in[0] == 0) begin code_out <= 3‘b111; en_out <= 1; state <= 0; end else if (data_in == 8‘b11111111) begin code_out <= 3‘b111; en_out <= 0; state <= 1; end else begin // in case of genetaring latch, while many examples ignore this step code_out <= 3‘b111; en_out <= 1; state <= 1; end end endmodule

以及testbench

`timescale 1ns/1ps module coder_83_tb(); reg [7:0] data_in; reg en_in_n, clk; wire en_out; wire state; wire [2:0] code_out; coder_83 u_coder_83( .data_in(data_in), .en_in_n(en_in_n), .en_out(en_out), .state(state), .code_out(code_out) ); always #20 clk = ~clk; always@(posedge clk) begin if(!data_in) data_in <= 8‘b11111111; else data_in <= data_in << 1; end initial begin clk = 0; data_in = 8‘b11111111; en_in_n = 1; # 100 en_in_n = 0; # 5000 en_in_n = 1; end endmodule

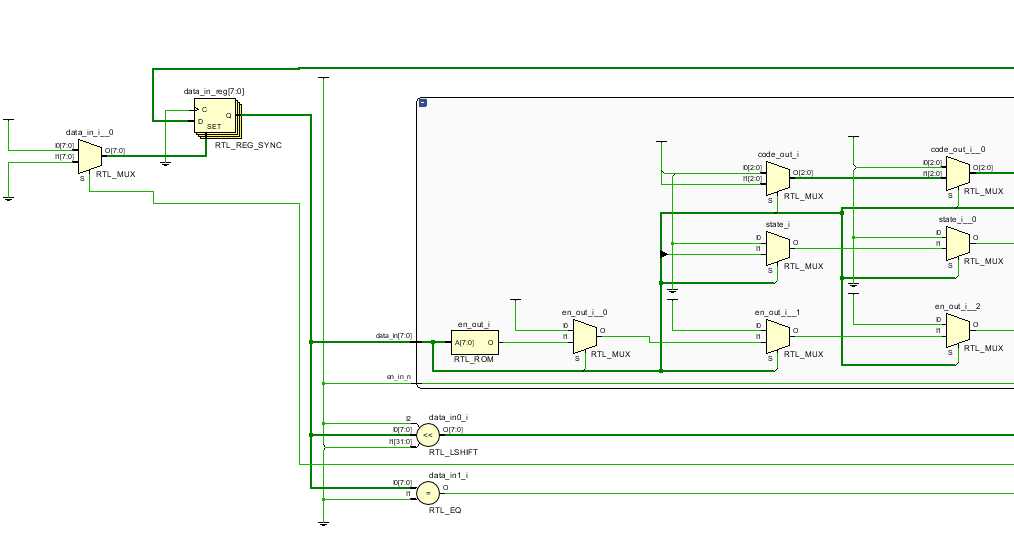

但是vivado综合的时候就很奇怪,出现了一个ROM。

很难解释为什么会出现这个东西……但功能仿真都是正常的。

标签:png code sed 编码器 examples amp html 写法 reg

原文地址:https://www.cnblogs.com/wuwanghanchuan/p/13160677.html