标签:电路 rar 笔试 delay info 决定 不同 效果 capture

A. RTL先被替代成通用的逻辑单元,再mapping到工艺库中的逻辑单元

B. RTL文件,设计约束,library和UPF文件是综合的输入

C. 综合的约束越紧越好,以便给后端实现留出足够的余量

D. 为模拟芯片实际使用的环境,综合一般使用typical的library

解析:选项A:DC过程包括三个步骤,Synthesis= Translate + Mapping + Optimization,如下图:

(1)Translate是将 HDL转化为GTECH库元件组成的电路(GTECH库是Synopsys公司提供的通用的、独立于工艺的元件库)

(2)Mapping是将GTECH映射到设计指定的工艺库(target library + link library)。

(3)Optimization是将网表按设计约束进行优化。

选项C:综合一般时钟频率过约10%,太紧会使工具难以收敛

选项D:综合的STA一般保证setupclean,所以一般选用传输延迟大(高温,低压)的库,比如slow library

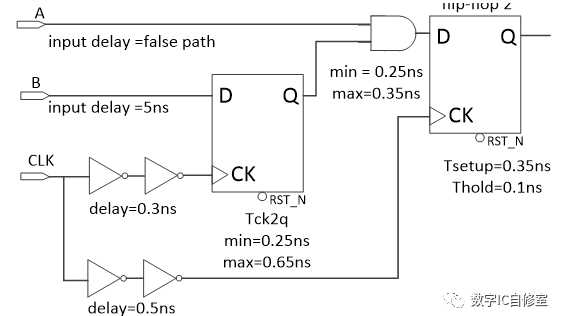

解析:reg2reg的STA hold时序分析:Tlaunch+Tck2q+Tcomb>Tcapture+Thold,所以flip-flop 2的hold timemargin=Tlaunch+Tck2q(min)+Tcomb(min)-Tcapture-Thold=0.3+0.25+0.25-0.5-0.1=0.2ns。

A. 5ns

B. 10ns

C. 15ns

D. 20ns

解析:

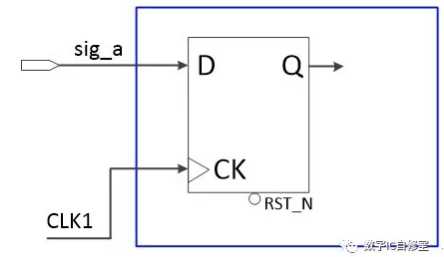

思路一:题目中当CLK1为100MHz,输入端口到D端的margin为10ns-5ns=5ns,当CLK1为50MHz时,时钟周期增大为20ns,为保证约束效果一致,margin应该保持为5ns,因此input_delay应设置为15ns。

思路二:保持50%时钟的margin,设置为10ns。

思路三:input delay根据外围电路而定,应保持为5ns。所谓的一致应该是timing clean。不管时钟频率多少,input delay都是由外围电路决定。通常外设手册上会给出一个max和一个min的值,分别setup和hold。设max影响setup分析,设min影响hold分析。一个设计,在不同应用场景频率可能会运行在不同的频率上。

标签:电路 rar 笔试 delay info 决定 不同 效果 capture

原文地址:https://www.cnblogs.com/lizhiqing/p/13206768.html